메모리 부족 시대의 하드웨어 설계: 엔지니어와 소싱 팀을 위한 현장 가이드

이 시리즈의 1부인 AI가 메모리 시장을 어떻게 무너뜨렸는가에서는 AI 데이터센터 수요가 어떻게 메모리를 병목으로 만들었는지, 그리고 DRAM 및 NAND 가격이 왜 빠르게 정상화되기 어려운지를 살펴봤습니다. 이제는 이런 환경에서 어떻게 대응해야 하는지 알아보겠습니다. 2026년에 하드웨어를 설계하거나 소싱하고 있다면 여전히 선택해야 할 것들이 있습니다. 어떤 부품을 사양으로 채택할지, 설계를 어떻게 유연하게 구성할지, 그리고 공급망 리스크를 어떻게 관리할지입니다.

먼저 개발 파이프라인에 있는 “차세대” 메모리 부품들을 살펴보고, 이어서 실무에서 많이 쓰이는 DRAM 및 플래시 부품으로 넘어가겠습니다. 그다음에는 엔지니어링과 조달 양쪽 모두를 위한 실질적인 대응 전략을 정리하겠습니다.

메모리 부품 전반을 폭넓게 살펴보려면, 제조사, 패키지, 공급 가능 여부를 기준으로 검색할 수 있는 Octopart의 메모리 IC 및 플래시 메모리 카테고리 페이지가 좋은 출발점이 됩니다.

핵심 요점

- 앞으로 나올 것과 지금 구할 수 있는 것을 구분해야 합니다. LPDDR6와 HBM4 같은 차세대 부품은 플랫폼이 어디로 향하고 있는지를 보여주지만, 2026년 설계 제품은 결국 오늘 재고로 확보 가능한 DDR5, LPDDR5X, 그리고 성숙한 NAND를 기반으로 출하될 가능성이 높습니다.

- 대체 가능성과 유연성을 고려해 설계하십시오. 주류 인터페이스를 표준으로 삼고, 부품 패밀리를 인증하며, 펌웨어에서 여러 용량을 지원해야 합니다. 가능하면 소켓과 모듈을 사용하고, 사용자 경험 목표를 충족하면서도 동작 가능한 다운빈 메모리 옵션도 계획해야 합니다.

- 공급 리스크를 엔지니어링 문제처럼 접근하십시오. 멀티소스 AVL을 구축하고, 핵심 라인에 대해서는 물량을 선확보하며, 수명주기와 대체품을 Octopart 같은 도구로 추적해야 합니다.

방향성을 보여주는 차세대 부품

Samsung의 LPDDR6 모바일 DRAM

온디바이스 AI, 자동차, 차세대 모바일 및 PC 플랫폼을 위해 설계된 Samsung의 LPDDR6는 LPDDR5X 대비 의미 있는 효율 향상, 확장된 I/O 아키텍처, 최대 10.7Gbps의 초기 속도를 제공합니다. 또한 LPDDR6 표준은 생태계가 성숙함에 따라 더 높은 수준으로 확장되도록 설계되었습니다. 아직 유통업체 재고에서 LPDDR6를 보기는 어렵지만, 선도적인 SoC나 플래그십 기기를 중심으로 설계한다면 이를 접하게 될 가능성이 높습니다.

HBM4

최상위 영역에서는 SK Hynix의 16단 적층, 48GB HBM4 디바이스가 2TB/s를 넘는 대역폭을 약속하고 있으며, 양산은 2026년 3분기 전후를 목표로 하고 있습니다. Samsung은 다른 접근 방식을 취하고 있는데, 4nm 로직과 1c DRAM을 사용해 열 성능을 개선하고 있습니다. AI 하드웨어를 개발하는 엔지니어가 일반 카탈로그 유통사를 통해 이런 제품을 직접 소싱하는 경우는 드물겠지만, HBM4는 모두에게 중요합니다. 첨단 DRAM 생산능력의 상당 부분을 흡수하고 있기 때문에, 기존 DRAM 공급이 계속 타이트한 이유 중 하나가 되기 때문입니다.

Samsung 10세대 V-NAND

400개가 넘는 레이어와 5.6GT/s 인터페이스를 갖춘 Samsung의 10세대 V-NAND는 데이터센터 및 AI급 워크로드를 위한 PCIe 5.0 및 향후 PCIe 6.0 SSD를 겨냥합니다. 이 실리콘 기반의 고집적 TLC는 향후 몇 년간 많은 엔터프라이즈 및 고급 클라이언트 드라이브의 기반이 될 것으로 예상됩니다.

Kioxia/Sandisk BiCS10 NAND

이 332단 BiCS10은 Toggle DDR 6.0 인터페이스를 통해 핀당 4.8Gb/s를 제공하며, AI 및 하이퍼스케일 스토리지를 겨냥합니다. EE Times에 따르면, Kioxia는 2026년 NAND 전체 생산량이 이미 AI 관련 애플리케이션에 판매 완료되었다고 밝혔으며, 수요 대응을 위해 BiCS10 양산 확대 시점을 2027년 하반기에서 2026년으로 앞당겼습니다.

상대적으로 제약이 덜한 주력 메모리 제품

이 부품들은 2026년 3월 초 기준으로 주요 유통업체에서 주문 가능했습니다. 공급 상황은 빠르게 변하고 있으므로 BOM을 확정하기 전에 Octopart에서 재고와 수명주기 상태를 반드시 확인하십시오.

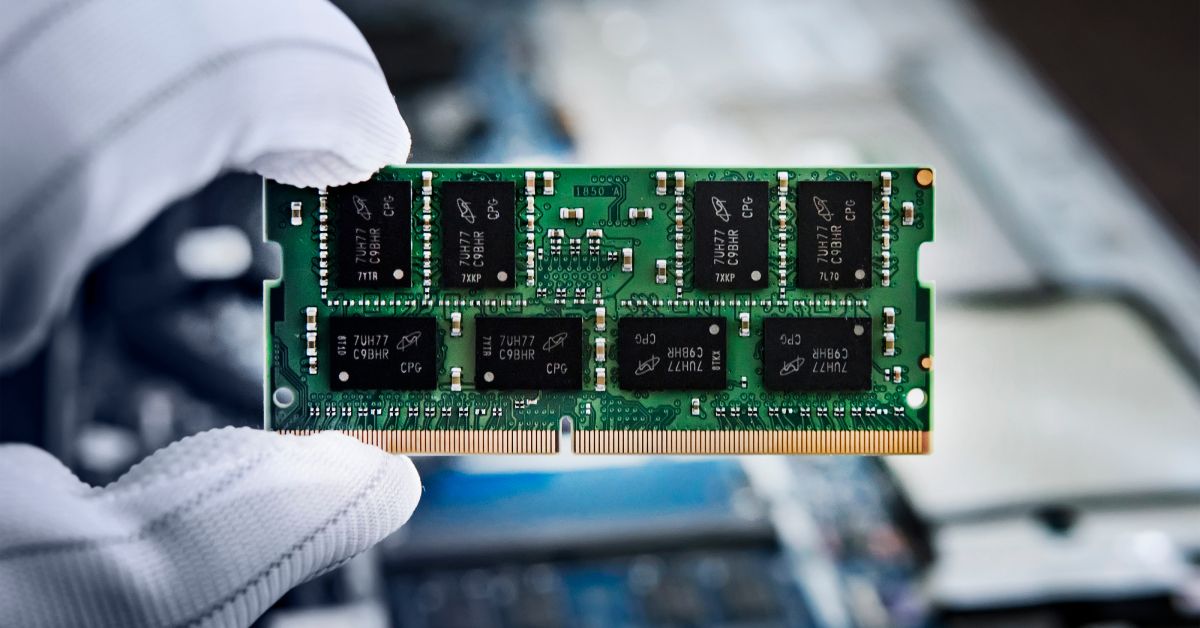

- Apacer D22.31491S.001, 8GB DDR5-4800 SO-DIMM. 소켓형 모듈을 사용할 수 있는 설계에 적합한 실용적인 “레이트 바인드” DRAM 옵션으로, 대체 부품 적용 시 조달 측의 협상력을 높여줍니다.

- MT60B2G8RZ-56B IT:D, 16Gbit DDR5 SDRAM(2G x 8), 78볼 VFBGA. 맞춤형 보드 레벨 메모리 설계에 적합한 주류 x8 DDR5-5600급 DRAM IC로, 단일 모듈 SKU보다 더 현실적인 세컨드 소스 유연성을 제공합니다.

- Macronix MX30LF4G28AD-XKI-TR, 4Gbit SLC NAND(VFBGA-63). 내구성과 예측 가능한 동작 특성이 필요한 산업용 및 임베디드 NAND 설계에 잘 맞으며, 컴팩트한 BGA 풋프린트를 제공합니다.

- Macronix MX60LF8G28AD-TI-T, 8Gbit SLC NAND(TSOP-48). 성숙한 컨트롤러 생태계와의 호환성, 그리고 미세 피치 BGA보다 쉬운 보드 리워크가 필요한 경우, 널리 지원되는 병렬 NAND 풋프린트로 실용적인 선택이 됩니다.

- Macronix MX52LM04A11XSI, 4GB eMMC 5.1(BGA-153). 컨트롤러 의존성을 줄이고, 로우 NAND와 커스텀 플래시 스택 조합보다 더 깔끔한 대체 경로를 원할 때 적합한, 단순하고 관리가 쉬운 NAND 옵션입니다.

- Macronix MX52LM08A11XVW, 8GB eMMC 5.1(BGA-153). 많은 임베디드 Linux 및 HMI급 시스템에 적합한 실용적인 용량 지점이며, 더 작은 eMMC 부품과 동일한 인터페이스 및 통합상의 장점을 제공합니다.

- Micron MT40A2G8SA-062E:F, 16Gbit DDR4 DRAM(2G x 8). 여전히 많은 플랫폼에서 대량으로 사용되는 주력 제품이며, DDR5가 필수가 아닐 때 현실적인 “즉시 출하” 옵션입니다.

설계 플레이북: 엔지니어가 유연성을 내장하는 방법

이런 배경 속에서도 하드웨어 엔지니어가 설계를 더 탄탄하게 만들기 위해 취할 수 있는 조치는 여전히 많습니다.

- 주류 인터페이스와 패밀리를 표준화하십시오. DDR5, LPDDR5X, e.MMC, UFS, SPI/QSPI 플래시는 생태계가 깊고 세컨드 소스도 많습니다. 일반적인 전압과 패키지 범위 안에 머무르면 호환 가능한 부품 풀을 최대화할 수 있습니다.

- 펌웨어와 메모리 맵에 유연성을 내장하십시오. 단일 DRAM 용량이나 SPI 플래시 크기를 하드코딩하지 마십시오. 초기화 코드에서 여러 지오메트리를 지원해 대체 부품을 쉽게 교체할 수 있도록 해야 합니다.

- 적합하다면 관리형 비휘발성 메모리를 우선 고려하십시오. e.MMC와 UFS는 안정적인 인터페이스 뒤에 NAND 관리 세부사항을 숨기며, 특정 컨트롤러에 묶인 로우 NAND보다 대체 경로가 더 명확한 경우가 많습니다.

- 다운빈 변형도 계획하십시오. 더 낮은 메모리 구성에서도 허용 가능한 사용자 경험을 제공할 수 있도록 소프트웨어를 설계해야 합니다. 예를 들어 기본 동시성 수준을 낮추거나, 에셋 세트를 줄이거나, 기능 등급화를 적용하는 방식이 있습니다.

- 가능하면 모듈형 메모리와 스토리지를 사용하십시오. SO-DIMM, UDIMM, M.2 SSD용 소켓은 구성의 레이트 바인딩을 가능하게 하고 조달 측의 협상력을 높여줍니다. 납땜 고정형 메모리는 정말로 필요한 제약된 폼팩터에만 남겨두십시오.

소싱 플레이북: 조달팀이 리스크를 관리하는 방법

현재 상황은 적극적인 대응을 요구합니다. 2026년 2월 말, Lenovo는 채널 파트너들에게 3월 가격 인상 전에 주문을 넣기 위해 월말 이전 발주를 권고했고, TrendForce는 PC용 DRAM(DDR4/DDR5) 평균 가격이 1분기에만 전 분기 대비 105~110% 상승할 것으로 전망했습니다. 아래 플레이북은 이러한 새로운 현실을 반영합니다.

- 핵심 DRAM 및 NAND 라인에 대해 물량 배정과 장기 계약을 확보하십시오. 특히 서버, AI 박스, 고급 노트북이 그렇습니다. TrendForce 같은 기관의 시장 인텔리전스는 언제 커밋해야 할지 판단하는 데 도움이 됩니다.

- 승인 공급업체 목록은 개별 SKU가 아니라 패밀리 중심으로 구축하십시오. 허용 가능한 모듈, NAND, e.MMC의 범주를 정의하고, 엔지니어링 팀과 협력해 여러 옵션을 사전에 검증해야 합니다.

- 제품을 메모리 민감도에 따라 세분화하십시오. 성능과 마진에 가장 큰 영향을 주는 SKU에 희소하고 고가의 메모리를 우선 배정하고, 메모리 민감도가 낮은 장치에는 보다 공격적인 비용 통제를 적용하십시오.

- 장수명 제품에는 메모리 재고를 전략적 헤지로 활용하십시오. 핵심 DRAM 또는 NAND의 버퍼 재고를 보유하는 것이, 부품이 제약 상태에 들어갔을 때 제품 수명 중간에 보드를 재설계하거나 펌웨어를 다시 작성하는 것보다 더 저렴할 수 있습니다.

유연성이 곧 전략입니다

이 시리즈의 1부에서는 메모리 수급난의 배경을 살펴봤습니다. 그리고 여기서는 지금 무엇을 해야 하는지를 다뤘습니다. 엔지니어든 조달 담당자든 답은 같습니다. 최고의 헤지는 유연성입니다. 대체 가능성을 고려해 설계하고, 폭넓게 검증하며, Octopart 같은 도구를 활용해 선택지를 항상 가시화하고 최신 상태로 유지하십시오. 이번 사이클을 가장 잘 버텨낼 팀은 설계와 공급망에 초기에 선택 가능성을 내장해 두고, 공급과 가격 변화에 맞춰 계속 적응하는 팀일 것입니다.

자주 묻는 질문

왜 2026년에도 DRAM과 NAND를 여전히 구하기 어려운가요?

현재의 부족 현상은 기술 한계가 아니라 웨이퍼 배분 때문에 발생하고 있습니다. 메모리 업체들은 특히 HBM과 데이터센터 DRAM 같은 고마진 AI 수요를 다년 계약 하에 우선시하고 있습니다. HBM은 비트당 기존 DRAM보다 훨씬 더 많은 웨이퍼 생산능력을 소모하기 때문에 DDR5, LPDDR, NAND에 남는 생산능력이 줄어들고, 그 결과 공급이 계속 타이트하게 유지됩니다.

엔지니어는 지금 LPDDR6나 HBM4 같은 차세대 메모리를 설계에 반영해야 할까요?

LPDDR6와 HBM4는 플랫폼의 향후 방향을 보여주지만, 2026년 제품 대부분은 현재 조달 가능한 DDR5, LPDDR5X, 그리고 성숙한 NAND를 기반으로 출하될 것입니다. 엔지니어는 아직 유통망에 풀리지 않은 부품에 베팅하기보다, 생산 기간 동안 안정적으로 소싱할 수 있는 부품을 선택하면서도 향후 호환성을 염두에 두고 설계해야 합니다.

하드웨어 설계를 메모리 부족 상황에 더 강하게 만들려면 어떻게 해야 하나요?

탄탄한 설계는 유연성과 대체 가능성에 초점을 맞춥니다. 여기에는 주류 인터페이스 표준화, 여러 용량과 공급업체 검증, 펌웨어에서 메모리에 대한 하드코딩된 가정 제거, 그리고 가능할 경우 소켓이나 모듈 사용이 포함됩니다. 다운빈 메모리 옵션까지 지원하면 더 높은 용량의 부품이 부족할 때도 제품을 계속 출하할 수 있습니다.

조달팀이 메모리 공급 리스크를 관리하는 가장 좋은 방법은 무엇인가요?

조달 부서는 메모리를 범용 구매 품목이 아니라 전략적 자원으로 다뤄야 합니다. 모범 사례로는 핵심 SKU에 대해 장기 물량을 선확보하고, 단일 부품이 아닌 부품군 중심으로 AVL을 구축하며, Octopart 같은 도구로 수명 주기와 대체품을 모니터링하고, 강제적인 재설계를 피하기 위해 장수명 제품에 대해서는 선별적으로 재고를 보유하는 것이 포함됩니다.