실용적인 단계: PCB에서 측면 방출 LED 구현하기

임베디드 PCB 동공은 PCB의 가장자리를 따라 LED와 같은 구성 요소에 측면 접근을 제공하는 데 사용될 수 있습니다.

제품 소형화에 대한 요구를 충족하기 위해 더 많은 사람들이 내장형 구성 요소를 사용하고 있습니다. 내장형 구성 요소(캐패시터와 저항만 있는 경우에는 내장형 수동소자로 언급되기도 함)는 멀티 레이어 PCB의 내부 레이어에 추가할 수 있는 표면 실장 장치로, 최종 PCB 스택업 내부에 내장될 수 있도록 주변 유전체 레이어에 공동이 있습니다. 또한, 사람들은 같은 클록을 공유하고 디자인 전체에 연속되는 시프트 레지스터를 사용한 디자인으로 전환하고 있습니다.

이 블로그에서 Max Clemons(AE, 마케팅)은 작업 중인 인쇄 회로 기판의 매우 가장자리에서 빛을 발할 수 있는 내장형 측면 시야 LED를 만드는 새로운 접근 방식을 보여줍니다. 이 LED는 레이어 스택에 라미네이트됩니다.

내장형 측면 시야 LED 만들기

Altium Designer 설치 시 포함된 블루투스 센티넬 디자인은 새로운 리지드-플렉스 도구 중 일부를 소개하는 데 좋은 예시입니다. 저는 이 디자인을 수정하여 다른 스타일의 유연한 영역을 포함시키도록 요청받았지만, 재사용된 보드는 주변에 LED를 배치할 공간이 없었습니다. LED 스트립을 추가하는 방법을 찾는 것은 흥미로운 도전이며, 새로운 도구를 시도해 볼 완벽한 기회를 제공합니다.

Altium Designer에 추가된 멋진 새 기능 중 하나는 보드 내에 전자 부품을 내장할 수 있는 기능입니다. 이는 매우 밀집된 디자인에서 공간을 줄이거나 고속 애플리케이션에서 반환 길이를 단축하기 위한 여러 가지 이유로 수행될 수 있습니다. 수정된 블루투스 센티넬 디자인의 경우, LED에 대한 대안이 필요했고, 내장형 사이드뷰 LED는 디자인 도구의 원래 기능을 유지하면서 너무 많이 수정할 필요가 없었습니다.

보드에서 사용 가능한 수직 공간의 양에만 제한되었지만, Everlight 48-213 SMD LED와 같은 얇은 패키지는 내장하기에 이상적이었습니다. 이 풋프린트를 생성하는 것은 새로운 기능을 활용하기 위한 몇 가지 작은 추가 사항만 있으면 비교적 간단했습니다.

1. PCB 풋프린트로 시작하기

시작하기 위해, 기존의 풋프린트를 가져와 PCB 캐비티에 맞게 수정할 수 있습니다. 먼저, 수정하기 전에 내장하고자 하는 구성 요소의 복사본을 만듭니다.

풋프린트가 없고 온라인 자원을 통해 풋프린트를 찾을 수 없다면, 처음부터 풋프린트를 만들어야 합니다. 풋프린트 정보와 패키지 치수는 모두 데이터시트에서 확인할 수 있습니다. 풋프린트를 생성할 때, 좋은 결과를 빠르게 얻는 방법 중 하나는 적절한 참조점과 그리드 간격을 설정하는 것입니다. 거기서부터는 단순히 패드, 3D 바디, 그리고 필요한 추가적인 기계적 정보를 배치하는 문제입니다.

2. 3D 바디 정의하기

대부분의 LED에 대해 압출된 바디가 잘 작동했으며, 렌즈 객체만이 예외였습니다. 압출된 바디는 놀랍도록 견고하며 다각형 모양에 잘 작동하지만, 렌즈의 곡선 모서리는 외부에서 생성하여 STEP 모델로 가져오는 것이 더 실현 가능했습니다.

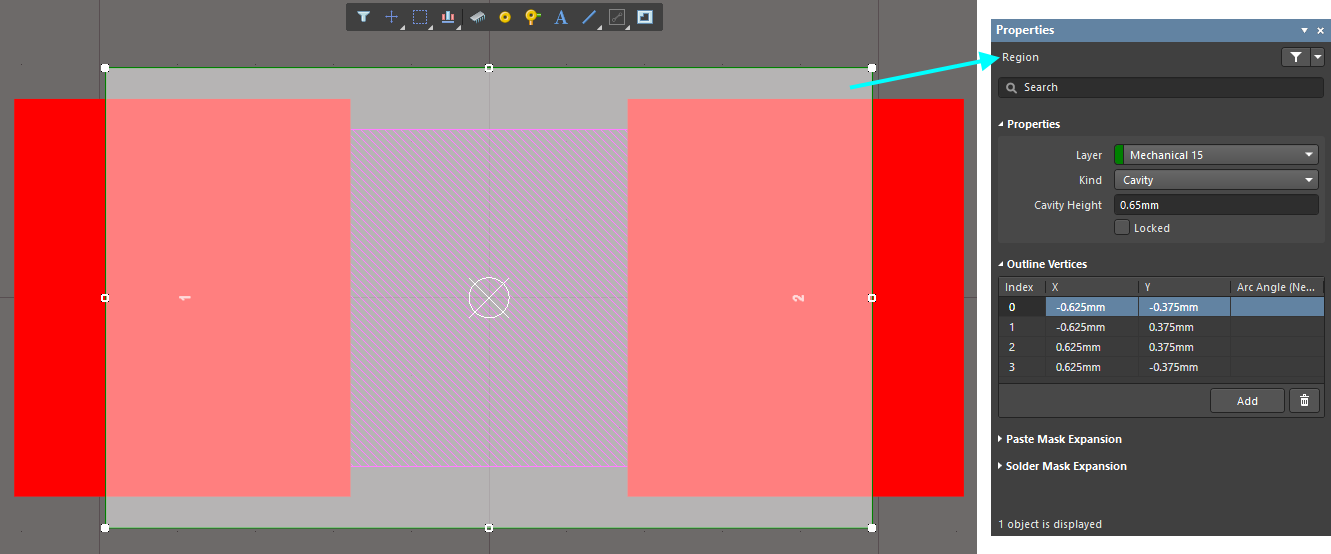

3. PCB 풋프린트의 캐비티

구성 요소를 내장하기 위한 준비는 발자국 자체에서 시작됩니다. 캐비티는 단순히 아래와 같이 설정된 솔리드 영역으로, 패널에 배치되어야 합니다. 속성에서 정의된 높이는 구성 요소 본체를 위해 충분히 커야 합니다. LED 패키지는 0.3mm였으므로, 캐비티는 0.35mm 높이로 생성되었습니다. 물론, 이는 궁극적으로 귀하의 특정 레이어 스택과 전체 설계 의도에 따라 달라질 것입니다.

4. 캐비티를 배치하기 위한 부품 배치

캐비티는 내장형 측면 보기 LED가 될지 여부와 관계없이 어떤 발자국 내에도 배치될 수 있다는 점을 주목하는 것이 중요합니다. 전자 구성 요소가 내부 레이어에 배치될 때, 캐비티는 코어 재료의 일부를 깎아내지만, 외부 레이어에서는 디자인에 어떤 영향도 주지 않습니다. 새로 생성된 LED 중 하나를 내부 레이어에 배치하면 이것이 실제로 얼마나 멋진지 볼 수 있습니다.

5. 스택업 내의 내장 캐비티

기술적으로, 캐비티는 특정 영역에서 레이어 스택을 변경하며, 이 정보가 제작 노트를 통해 전달되는 것이 중요합니다. 자동으로 생성되어 배치될 수 있는 레이어 스택 다이어그램은 이미 이를 고려하고 있습니다. 이 설계에서 캐비티가 추가된 위치나 스택업에서 해당 영역에 포함된 레이어에 대한 의문은 없었습니다.

6. 조립 과정

조립도 고려해야 할 사항이며, 내장된 구성 요소는 보드 외부의 구성 요소보다 먼저 배치됩니다. 내부 레이어에 전자 구성 요소가 내장된 경우 별도의 픽 앤 플레이스 보고서와 추가 조립 도면 출력물을 생성하는 것이 좋습니다.

저는 참조를 위해 발자국과 완성된 디자인을 포함시켰지만, 내장된 구성 요소를 사용하는 방법에는 분명 한계가 없습니다. 그저 이 문제를 해결하는 흥미로운 방법일 뿐입니다!

위에 표시된 프로젝트의 사본을 다운로드하세요:

- Bluetooth Sentinel Modified.zip

내장되지 않았을 때도 캐비티가 전자 구성 요소의 일부가 될 수 있다는 점을 언급할 가치가 있습니다 - 구성 요소를 내부 레이어로 이동할 때 자동으로 그 역할을 수행하기 때문입니다.

그런 다음 언급할 가치가 있는 것은 제작 및 조립 출력이 필요하다는 것입니다 - 캐비티 영역을 보여주는 레이어 스택 테이블과 임베디드 패널을 위한 별도의 픽 앤 플레이스 보고서가 필요합니다. 왜냐하면 그것들은 이전 공정 단계에서 장착되기 때문입니다.