Tự động hóa Định tuyến PCB Với Situs Topological Autorouter

Trang này xem xét Situs Topological Autorouter. Phần này của PCB Editor sử dụng bản đồ topo để xác định đường dẫn định tuyến PCB và chuyển đổi điều này thành một tuyến đường chất lượng cao.

Có một công cụ trong ứng dụng thiết kế PCB mà mọi người thường yêu ghét: máy định tuyến tự động. Tôi đã sử dụng máy định tuyến tự động trong một số thiết kế đầu tiên của mình có nhiều đường mạch. Những bảng mạch đầu tiên đó không có bất kỳ yêu cầu nào hạn chế tự do định tuyến như trở kháng kiểm soát hay ngân sách tổn thất. Có lẽ tôi có thể (và nên) đã định tuyến những bảng mạch đầu tiên đó bằng tay chỉ để có thêm kinh nghiệm về bố trí PCB, nhưng tôi vẫn sử dụng máy định tuyến tự động.

Trong khi nhiều máy định tuyến tự động thế hệ hiện tại đáp ứng mỗi yêu cầu này ở một mức độ nào đó, các phương pháp dựa trên lưới, dựa trên hình dạng hoặc hình học mà chúng áp dụng trong việc lập bản đồ không gian định tuyến đều gặp phải những hạn chế nghiêm trọng với công nghệ đóng gói linh kiện dày đặc, không vuông góc và hình học không đều - những công nghệ đang trở nên phổ biến hơn trong thiết kế bảng mạch hiện đại. Máy định tuyến tự động thế hệ hiện tại, vì những hạn chế hình học của chúng, cũng thường tạo ra kết quả có "vẻ như được định tuyến tự động", dẫn đến việc phải sửa chữa thủ công rộng rãi. Thực sự, nhiều nhà thiết kế e ngại sử dụng máy định tuyến tự động chỉ vì hạn chế này.

Công cụ tự định tuyến Situs™ của Altium Designer là một công cụ có thể được sử dụng để tự động định tuyến các mạch cụ thể hoặc các lớp mạch, và nó có thể là một công cụ hữu ích cho quy trình thiết kế của bạn. Điều quan trọng cần lưu ý là công cụ tự định tuyến này là một công cụ tự động hóa tiên tiến có thể giúp loại bỏ nhiều công việc định tuyến thủ công, nhưng quan trọng là phải biết khi nào và ở đâu sử dụng nó.

Công cụ tự định tuyến Situs không phải là một công cụ chỉ cần nhấp và sử dụng. Nó đòi hỏi sự lên kế hoạch và cấu hình.

Để tận dụng tối đa công cụ này đòi hỏi một số kế hoạch và suy nghĩ trước trong bố cục PCB, thiết lập các Lớp Mạch để các nhóm mạch cụ thể có thể được nhắm mục tiêu bằng công cụ tự định tuyến, và thậm chí thiết kế một chiến lược định tuyến tùy chỉnh để triển khai với công cụ tự định tuyến Situs.Trong bài viết này, chúng ta sẽ xem xét một số nền tảng về tự định tuyến, cách cấu hình công cụ tự định tuyến Situs, và một ví dụ cho thấy kết quả của một công cụ tự định tuyến như Situs. Sử dụng các liên kết Mục lục ở trên để nhảy đến từng phần trong hướng dẫn này.

Tổng quan về Situs Autorouter

Các Phương pháp Truyền thống trong Tự Định Tuyến

Thiết kế điện tử cơ bản là một tập hợp các linh kiện, với các chân của chúng được kết nối với nhau theo một cách đặc biệt. Thiết kế được thực hiện bằng cách sắp xếp các linh kiện lên một cấu trúc cơ khí đa lớp, được gọi là bảng mạch in (PCB). Các kết nối được thực hiện vật lý thông qua các đường dẫn đồng rời rạc đi xuyên qua và trên PCB, từ chân của linh kiện này sang chân của linh kiện khác.

Nhiệm vụ tạo ra đường dẫn đồng rời rạc, hay còn gọi là đường mạch, cho mỗi kết nối có thể rất phức tạp. Một thiết kế điển hình có thể có hàng nghìn kết nối giữa các chân của linh kiện, và các đường mạch có thể phải được tạo ra giữa các linh kiện được đặt rất chật chội trên bề mặt PCB.

Các autorouter đầu tiên đã lập bản đồ không gian thiết kế bằng cách định nghĩa một lưới đều, thường xuyên trên toàn bộ bảng mạch, với mục tiêu là mỗi chân linh kiện nằm trực tiếp trên một điểm lưới và bao gồm đủ điểm lưới trong không gian trống để mạch tất cả các kết nối. Các linh kiện đầu tiên được cung cấp với các chân của chúng cách nhau bằng bội số của 0,1 inch, do đó việc định nghĩa một lưới phù hợp tương đối dễ dàng, như được hiển thị dưới đây.

Khi tất cả các linh kiện đều có chân với khoảng cách 0,1 inch, một bộ định tuyến lưới có thể được sử dụng.

Với sự ra đời của các linh kiện gắn mặt, khoảng cách giữa các chân linh kiện trở nên nhỏ hơn nhiều, và các nhà sản xuất cũng bắt đầu cung cấp linh kiện với khoảng cách chân theo hệ mét. Sự cải tiến trong công nghệ chế tạo cho phép nhà thiết kế sử dụng các đường dẫn rất hẹp, có thể được sắp xếp gần nhau hơn. Những yếu tố này kết hợp làm cho các bộ định tuyến lưới đồng nhất truyền thống trở nên không thể sử dụng được trên các thiết kế sử dụng công nghệ đóng gói và chế tạo này. Bởi vì lưới cần phải đủ mịn để có thể đối phó hiệu quả với các công nghệ mới, các bộ định tuyến lưới cần một lượng lớn bộ nhớ và sức mạnh xử lý - chưa kể đến thời gian - để xây dựng lưới định tuyến và định tuyến thiết kế.

Để cải thiện phương pháp này, một kỹ thuật được biết đến với tên gọi mở rộng hình chữ nhật [1] đã được phát triển. Kỹ thuật này định nghĩa không gian giữa các chướng ngại vật trên bảng mạch như một loạt các hình chữ nhật. Một khi bộ hình chữ nhật đã được xác định, một đường dẫn định tuyến được xác định bằng cách theo dõi các cạnh của hình chữ nhật. Kỹ thuật này cho phép định tuyến các linh kiện với khoảng cách chân khác nhau, và nó cũng cho phép bộ định tuyến tự động đối phó với các công nghệ chế tạo mới hơn như linh kiện gắn mặt. Phương pháp này thường được gọi là định tuyến tự động dựa trên hình dạng, bởi vì nó mô hình hóa các kênh định tuyến sử dụng các hình dạng hình chữ nhật, như được hiển thị trong hình dưới đây.

Bộ định tuyến hình chữ nhật chia không gian thành các khu vực hình chữ nhật, sau đó được sử dụng để tìm đường đi.

Mặc dù bộ định tuyến tự động mở rộng hình chữ nhật có thể khắc phục một số vấn đề về tốc độ và bộ nhớ của bộ định tuyến lưới đồng nhất, chúng vẫn bị hạn chế về hình học trong các đường đi có thể xác định được. Một khi bản đồ hình chữ nhật được thiết lập cho một bảng mạch, các "mặt sóng" định tuyến mở rộng ra dọc theo các cạnh của các hình chữ nhật liền kề - chỉ theo hướng dọc và ngang. Định tuyến bị hạn chế theo hướng vuông góc với các ranh giới của các hình chữ nhật. Vấn đề có thể phát sinh với các hình học không vuông góc, như được tìm thấy với, ví dụ, các thành phần mảng chân ghép lệch hoặc các thành phần được xoay. Thường trong những trường hợp này, không thể tìm thấy đường đi vuông góc và bộ định tuyến mở rộng hình chữ nhật sẽ thất bại.

Bao bì linh kiện tiếp tục thu nhỏ về kích thước và khoảng cách chân, và các gói mới như Ball Grid Arrays (BGAs) sử dụng lưới lệch để tối đa hóa mật độ chân của chúng. Kết hợp với điều này, bao bì sản phẩm nhỏ và không bình thường thường yêu cầu các linh kiện được đặt ở các hướng không đều và trên các PCB có hình dạng không thường. Khi xu hướng này ngày càng phát triển, sẽ trở nên ngày càng khó khăn cho bộ định tuyến mở rộng hình chữ nhật để đáp ứng các thách thức định tuyến của thiết kế bảng mạch hiện đại.

Điều cần thiết là một kỹ thuật mới để lập bản đồ không gian định tuyến, không mô hình hóa bảng mạch chỉ như những hình chữ nhật đơn giản và không giới hạn trong các lối đi rectilinear giữa các chướng ngại vật.

- [1] Một Phương Pháp Định Tuyến Không Lưới cho Bảng Mạch In, Hội nghị Tự động Hóa Thiết kế lần thứ 22nd, Bài báo 32.2 năm 1984, A.C. Finch, K.J. Mackenzie, G.J. Balsdon, G Symonds của Racal Redac Ltd.

Phương pháp Topological

Một cách tiếp cận topological đối với việc tự động định tuyến, như được sử dụng bởi Situs autorouter của Altium Designer, sử dụng một phương pháp lập bản đồ không gian định tuyến khác - một phương pháp không bị giới hạn về mặt hình học. Thay vì sử dụng thông tin tọa độ không gian làm khung tham chiếu, một autorouter topological xây dựng bản đồ chỉ sử dụng vị trí tương đối của các chướng ngại vật trong không gian, không tham chiếu đến tọa độ của chúng.

Bản đồ topo là một kỹ thuật phân tích không gian sử dụng phương pháp tam giác hóa không gian giữa các chướng ngại vật liền kề. Bản đồ tam giác này sau đó được các thuật toán định tuyến sử dụng để "dệt" qua các cặp chướng ngại vật, từ điểm bắt đầu tuyến đường đến điểm kết thúc tuyến đường. Ưu điểm lớn nhất của phương pháp này là bản đồ không phụ thuộc vào hình dạng (các chướng ngại vật và đường định tuyến có thể có bất kỳ hình dạng nào) và không gian có thể được đi qua ở bất kỳ góc độ nào - các thuật toán định tuyến không bị giới hạn chỉ di chuyển theo đường thẳng đứng hoặc ngang, như với các bộ định tuyến mở rộng hình chữ nhật.

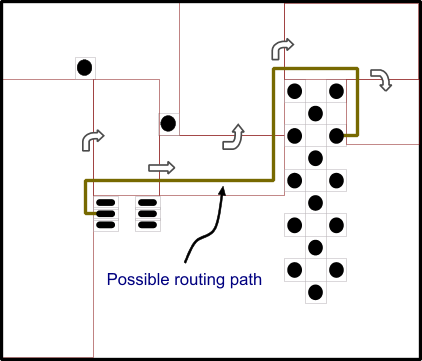

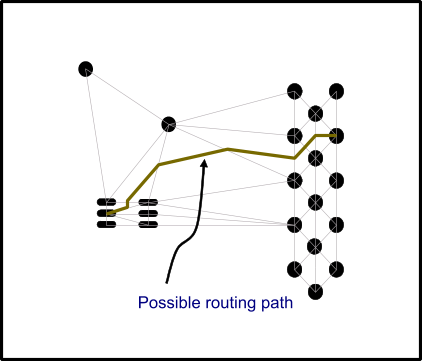

Để xây dựng bản đồ topo của một bảng mạch, Situs liên kết mỗi chướng ngại vật trên bảng mạch với các chướng ngại vật lân cận, tạo nên thứ giống như một tập hợp các mạng nhện kết nối. Các đường định tuyến tiềm năng sau đó được xác định bằng cách bước từ một sợi mạng này sang sợi mạng tiếp theo, rồi đến sợi mạng tiếp theo, và cứ thế cho đến khi đạt được mục tiêu. Phương pháp lập bản đồ này không bị ràng buộc về mặt hình học với không gian định tuyến; đường đi tiềm năng đơn giản chỉ là dệt qua giữa mỗi cặp chướng ngại vật, như hình dưới đây cho thấy.

Bản đồ topo loại bỏ hạn chế cơ bản của các bộ định tuyến trước đây - hạn chế được tạo ra bởi việc sử dụng cùng một không gian hình học để lập bản đồ đường đi như họ thực hiện định tuyến. Bằng cách tách không gian lập bản đồ khỏi không gian định tuyến, bộ định tuyến topo có khả năng lập bản đồ các con đường tự nhiên hơn và cũng tìm được các lộ trình định tuyến không vuông góc. Quá trình lập bản đồ này hoạt động giống như cách các nhà thiết kế làm, ở chỗ họ tìm kiếm một lộ trình đi qua bảng mạch theo cách trực tiếp nhất, đồng thời duy trì, ở một mức độ nào đó, hướng lớp họ đã chỉ định. Các nhà thiết kế không hạn chế quyết định của mình dựa trên việc liệu một kết nối qua một khu vực cụ thể có thể được thực hiện bằng cách sử dụng một loạt các đường dẫn vuông góc hay không, mà đơn giản quyết định liệu một đường dẫn có thể hoặc không thể đi qua một kênh định tuyến khả dĩ.

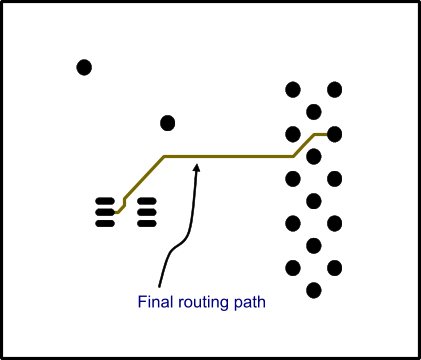

Như được minh họa bởi lộ trình được lập bản đồ trong hình bên trái, lộ trình ban đầu được định nghĩa theo topo có thể không phù hợp làm lộ trình hoàn thiện. Thông qua các thuật toán định tuyến tinh vi, Situs chuyển đổi lộ trình được lập bản đồ thành lộ trình định tuyến phù hợp, một ví dụ được minh họa trong hình bên phải.

Một bộ định tuyến topo không cố gắng lập bản đồ vào hình học của không gian, nó tìm kiếm một lộ trình giữa các chướng ngại vật.

Phân tích topo ban đầu của một lộ trình, mà không cần quan tâm đến tọa độ của các chướng ngại vật, dẫn đến tỷ lệ hoàn thành cao và tốc độ cao trên các bảng mạch thường được coi là khó cho các bộ định tuyến tự động - ví dụ như những bảng mạch có hình dạng không chuẩn, các thành phần có chân cắm dày đặc xen kẽ, hoặc các đường nét và lỗ cắt có hình dạng không đều.

Tìm Kiếm Lộ Trình

Một lợi ích khác của phương pháp topo là việc phân tích và xác định lộ trình định tuyến giống nhiều hơn với cách mà một nhà thiết kế thực hiện khi định tuyến bảng mạch một cách thủ công.

Ví dụ, kinh nghiệm đã cho thấy việc định tuyến tất cả các kết nối chia sẻ một lớp theo cùng một hướng là hiệu quả nhất, dẫn đến khái niệm về hướng lớp định tuyến. Trên các bảng mạch hai lớp đơn giản, điều này được thực hiện bằng cách chỉ định một lớp theo hướng ngang và lớp kia theo hướng dọc. Cả nhà thiết kế và bộ định tuyến tự động sau đó có thể đặt các lộ trình theo quy ước này.

Giống như các làn đường trên đường bộ, cách tiếp cận này mang lại trật tự cho nhiệm vụ định tuyến, cho phép nhà thiết kế hoặc autorouter xem bảng mạch như một loạt các kênh, sau đó có thể được phân công một cách có tổ chức. Trong cả hai loại bộ định tuyến lưới truyền thống và bộ định tuyến mở rộng hình chữ nhật, hướng của các lớp giới hạn ở dọc - các đường chạy từ đầu trên của bảng mạch xuống dưới, và ngang - các đường chạy ngang qua bảng mạch từ một bên sang bên kia.

Khi mật độ của thiết kế tăng lên, số lượng lớp cần thiết để định tuyến bảng mạch cũng sẽ tăng theo. Một khi thiết kế yêu cầu nhiều hơn hai lớp, việc tìm kiếm các lộ trình định tuyến theo các hướng khác ngoài dọc và ngang có thể sẽ hiệu quả hơn. Đây chính xác là điều mà một nhà thiết kế sẽ làm - xem xét dòng chảy của các đường kết nối và, nếu có đủ số lượng di chuyển theo một hướng cụ thể, ví dụ như chéo, gán một lớp cho hướng đó, sau đó định tuyến các kết nối đó trên lớp đó theo hướng đó.

Cả bộ định tuyến lưới cố định và bộ định tuyến mở rộng hình chữ nhật đều không thể ánh xạ trực tiếp theo hướng phi vuông góc; chúng chỉ có thể ánh xạ không gian theo cách ngang/dọc. Để tạo ra các tuyến đường chéo gọn gàng, những loại bộ định tuyến tự động này phải định nghĩa trước một tuyến đường sử dụng các đường ray vuông góc và sau đó chạy các quy trình hậu xử lý đặc biệt để chuyển các góc vuông thành các đường chéo.

Mặt khác, bộ định tuyến theo địa hình không bị giới hạn bởi hình học vuông góc và có thể xác định trực tiếp các tuyến đường chéo và gán chúng vào lớp phù hợp. Điều này không chỉ dẫn đến việc tự động định tuyến "tự nhiên" hơn, mà còn tạo ra việc định tuyến hiệu quả hơn và giảm thiểu số lượng vias cần thiết trong thiết kế hoàn chỉnh.

Hoàn thành Định Tuyến

Như đã đề cập trước đây, phân tích địa hình cung cấp một cách hiệu quả để xác định một con đường định tuyến có thể, nhưng con đường địa hình này phải được chuyển đổi thành một tuyến đường hoàn chỉnh chất lượng. Giống như một nhà thiết kế, bộ định tuyến tự động sẽ gặp phải nhiều tình huống khác nhau cần được xử lý theo các cách khác nhau, chẳng hạn như giải quyết con đường định tuyến qua bản đồ, theo dõi một ranh giới, hoặc đẩy chống lại các đối tượng tuyến đường hiện có trong nỗ lực di chuyển chúng qua.

Để đáp ứng các tình huống khác nhau, Situs sử dụng một loạt các động cơ định tuyến, bao gồm định tuyến bộ nhớ, định tuyến theo mẫu, định tuyến nguồn và mặt đất, định tuyến sóng trước, định tuyến dựa trên hình dạng đẩy và kéo, và một số động cơ định tuyến dựa trên phương pháp suy luận cho các tình huống cụ thể, như BGA fanout. Những động cơ này dựa trên các thuật toán định tuyến mạnh mẽ và đã được phát triển qua nhiều năm. Trong Situs, những động cơ định tuyến này tận dụng quá trình xác định đường đi thông minh của quá trình ánh xạ topo để tạo ra các kết nối hoàn thiện chất lượng cao.

Các động cơ định tuyến của Situs được điều khiển bởi một bộ tập tin chiến lược phức tạp, đóng vai trò là "bộ não" của máy định tuyến tự động. Một nhà thiết kế con người có một số lợi thế so với máy định tuyến tự động khi nói đến việc định tuyến một bảng mạch. Trí óc con người có thể lên kế hoạch, và khi làm như vậy, nó có thể xem xét và sắp xếp một số lượng lớn các yếu tố, phóng to để tập trung vào một yếu tố cá nhân, sau đó quay lại xem xét lại tình hình. Máy định tuyến tự động sử dụng một tập tin chiến lược để định nghĩa các mô hình suy nghĩ của chúng. Tập tin chiến lược kiểm soát các động cơ định tuyến, gọi chúng khi cần thiết và điều chỉnh hành động của chúng như vậy.

Để hiểu rõ vai trò quan trọng của tệp chiến lược, hãy xem xét cách thức công việc định tuyến thay đổi theo tiến trình định tuyến. Các phương pháp được sử dụng để định tuyến một bảng mạch trống ở giai đoạn đầu của quá trình định tuyến khác biệt so với khi mật độ định tuyến tăng lên, đòi hỏi các động cơ định tuyến khác nhau, được đánh trọng số tương ứng. Các hướng dẫn được viết trong tệp chiến lược định nghĩa một kế hoạch về cách định tuyến bảng mạch, gọi và đánh trọng số các động cơ định tuyến một cách cụ thể khi không gian định tuyến tương đối trống, sau đó thay đổi các động cơ và trọng số của chúng khi nó ép các tuyến đường cuối cùng qua không gian định tuyến đông đúc.

Bằng cách triển khai quá trình suy nghĩ hoặc bộ não của máy định tuyến tự động trong một tệp chiến lược, Altium có thể dễ dàng phát triển máy định tuyến tự động khi công nghệ bảng mạch thay đổi. Tệp chiến lược Situs là một trong những tệp chiến lược tinh vi nhất của bất kỳ máy định tuyến tự động nào hiện có. Nó kết hợp nhiều năm nghiên cứu về quá trình định tuyến, ghi lại sự chuyên môn của nhiều nhà thiết kế PCB kỳ cựu.

Định tuyến tự động cho PCB

Bộ định tuyến Situs Topological mang lại một cách tiếp cận mới cho thách thức định tuyến tự động. Nó sử dụng bản đồ địa hình tiên tiến để định nghĩa trước đường đi định tuyến, sau đó gọi một loạt các thuật toán định tuyến đã được chứng minh để chuyển đổi 'đường đi giống như con người' này thành một tuyến đường chất lượng cao. Là một phần không thể tách rời của PCB Editor, nó tuân theo các định nghĩa quy tắc điện và định tuyến của PCB.

Dự định Sử dụng Định tuyến Tự động

Trong khi Situs khá dễ dàng để thiết lập và chạy, có một số bước chuẩn bị trước khi định tuyến bạn có thể thực hiện để đảm bảo công cụ tạo ra kết quả định tuyến tối ưu với ít công việc dọn dẹp nhất. Một số mẹo cho việc định tuyến tự động bao gồm:

- Xác định các mạng lưới có ràng buộc lỏng lẻo nhất. Những mạng này thường là mạng số chậm không yêu cầu trở kháng.

- Xác định nhóm mạng lưới nào bạn muốn định tuyến tự động và thêm chúng vào Net Classes.

- Định tuyến các mạng quan trọng nhất trước. Những mạng này thường là mạng cặp vi sai tốc độ cao, mạng RF tần số cao hơn, và giao diện tương tự tần số thấp hơn.

- Giữ các kênh định tuyến mở để công cụ có thể đặt các đường dẫn.

- Áp dụng công cụ định tuyến tự động cho từng Net Class riêng lẻ. Bạn cũng có thể sử dụng công cụ để nhắm mục tiêu vào các thành phần cụ thể, hoặc thậm chí là từng mạng lưới riêng lẻ (xem bên dưới).

Đặt Vị trí Thành phần

Cuối cùng, việc đặt linh kiện có ảnh hưởng lớn nhất đến hiệu suất định tuyến. Trình chỉnh sửa PCB của Altium Designer bao gồm một số công cụ, như các đường kết nối được tối ưu hóa động, cho phép bạn điều chỉnh tinh vi vị trí đặt linh kiện. Vị trí đặt linh kiện tối ưu là khi các đường kết nối càng ngắn và ít "rối" nhất có thể.

Những phương pháp thiết kế tốt khác bao gồm việc đặt linh kiện sao cho các pad của chúng nằm trên một lưới đều (để tối đa hóa lượng không gian trống giữa các pad cho việc định tuyến), đặt các linh kiện gắn bề mặt cùng kích thước đối diện chính xác với nhau trên các bảng mạch hai mặt, và tham khảo bảng dữ liệu của nhà sản xuất thiết bị để biết hướng dẫn đặt bộ lọc. Đây không phải là danh sách đầy đủ các yếu tố cần xem xét khi đặt linh kiện, chỉ là một vài gợi ý.

Keepouts

Trình định tuyến yêu cầu một ranh giới đóng, được tạo thành từ các đối tượng keepout đã đặt. Thông thường, ranh giới này theo dõi mép của bảng mạch. Các đối tượng đã đặt sẽ tuân theo quy tắc khoảng cách áp dụng để đảm bảo rằng chúng giữ khoảng cách phù hợp từ ranh giới này, để đáp ứng bất kỳ yêu cầu khoảng cách cơ khí hoặc điện nào mà thiết kế có thể có. Trình định tuyến cũng sẽ tuân thủ các keepout bên trong ranh giới ngoài này, cũng như các keepout cụ thể cho từng lớp.

Bạn có thể tạo một ranh giới kín theo cạnh hình dạng của bảng mạch, sử dụng hộp thoại Line/Arc Primitives từ Board Shape. Để biết thêm thông tin về keepouts, xem Object Specific Keepouts.

Đổ đa giác

Đổ đa giác (hoặc đồng) có thể là dạng đặc (được lấp đầy bởi một hoặc nhiều vùng đồng) hoặc dạng lưới (được tạo từ các đường và cung). Một đổ đa giác dạng lưới từ trung bình đến lớn bao gồm một số lượng lớn các đường và cung. Mặc dù bộ định tuyến có thể định tuyến một bảng mạch bao gồm các đổ đa giác như vậy, số lượng đối tượng lớn mà chúng giới thiệu làm tăng độ phức tạp của quá trình định tuyến.

Thông thường, bạn chỉ nên đặt các đổ đa giác trước khi định tuyến nếu chúng là cần thiết, ví dụ, chúng được sử dụng để xây dựng hình dạng định tuyến trước không bình thường, có thể là định tuyến dòng điện chính đến hoặc một khu vực tiếp đất quan trọng. Nếu không, thì việc thêm các đổ đa giác vào thiết kế sau khi hoàn thành định tuyến là tốt hơn.

Có thể Định Tuyến?

Một bộ định tuyến tự động cố gắng hiểu và mô hình hóa quá trình định tuyến. Nếu bo mạch chứa một khu vực không thể định tuyến bằng tay, thì nó cũng không thể được định tuyến tự động. Nếu bộ định tuyến liên tục thất bại trên một linh kiện hoặc một phần của bo mạch thì bạn nên cố gắng định tuyến một cách tương tác. Có thể có vấn đề về vị trí đặt linh kiện hoặc cấu hình quy tắc khiến việc định tuyến trở nên không thể thực hiện được.

Định tuyến trước

Định tuyến trước cho các mạch quan trọng và, nếu việc chúng không được thay đổi bởi quá trình định tuyến là cần thiết, hãy khóa chúng bằng cách kích hoạt tùy chọn Khóa Tất Cả Định Tuyến Trước trong hộp thoại Chiến Lược Định Tuyến Situs. Tuy nhiên, hãy tránh khóa không cần thiết; một số lượng lớn đối tượng bị khóa có thể làm cho vấn đề định tuyến trở nên khó khăn hơn nhiều.

Các cặp mạch vi sai phải được định tuyến và khóa thủ công trước khi sử dụng bộ định tuyến tự động. Nếu bạn không làm điều này, việc định tuyến rất có thể sẽ thay đổi và làm ảnh hưởng đến tính toàn vẹn tín hiệu của cặp vi sai.

Cấu hình Quy Tắc Thiết Kế

Thuật ngữ quy tắc mặc định được sử dụng để mô tả một quy tắc với phạm vi truy vấn là Tất Cả.

Nếu một quy tắc bao gồm các giá trị Tối thiểu, Ưu tiên và Tối đa, bộ định tuyến tự động sẽ sử dụng giá trị Ưu tiên.

Hãy chắc chắn rằng các quy tắc thiết kế định tuyến phù hợp với công nghệ bảng mạch bạn đang sử dụng. Các quy tắc thiết kế không chính xác hoặc không phù hợp có thể dẫn đến hiệu suất tự động định tuyến rất kém. Lưu ý rằng bộ định tuyến tuân thủ tất cả các quy tắc Điện và Định tuyến, trừ quy tắc Góc Định tuyến.

Quy tắc được định nghĩa trong hộp thoại PCB Rules and Constraints Editor (Design » Rules), có thể truy cập trực tiếp từ hộp thoại Situs Routing Strategies.

Nếu một quy tắc bao gồm các giá trị Tối thiểu, Ưu tiên và Tối đa, bộ định tuyến sẽ sử dụng giá trị Ưu tiên.

Hệ thống quy tắc của Altium Designer là phân cấp. Ý tưởng là bạn bắt đầu với một quy tắc mặc định cho tất cả các đối tượng, sau đó thêm các quy tắc bổ sung để nhắm mục tiêu chọn lọc các đối tượng khác có yêu cầu khác biệt. Ví dụ, bạn nên có một quy tắc mặc định cho chiều rộng định tuyến bao phủ chiều rộng định tuyến phổ biến nhất được sử dụng trên bảng mạch, sau đó thêm các quy tắc tiếp theo để nhắm mục tiêu chọn lọc các mạng khác, các lớp mạng và vân vân.

Để kiểm tra một quy tắc có đang nhắm đúng đối tượng hay không, sao chép Truy vấn của quy tắc vào Bảng lọc PCB và Áp dụng nó. Chỉ những đối tượng được quy tắc nhắm đến mới nên vượt qua bộ lọc và được hiển thị với độ rõ nét đầy đủ. Một cách khác, sử dụng Bảng Quy tắc và Vi phạm PCB để nhanh chóng xem áp dụng quy tắc trên bất kỳ quy tắc nào được định nghĩa cho bảng mạch hiện tại.

Quy tắc quan trọng nhất là Độ rộng và Khoảng cách. Các cài đặt công nghệ định tuyến này xác định mức độ chặt chẽ của việc định tuyến có thể được 'đóng gói'. Việc chọn lựa này là một quá trình cân nhắc - đường dẫn càng rộng và khoảng cách càng lớn, việc chế tạo bảng mạch càng dễ dàng; ngược lại, đường dẫn và khoảng cách càng hẹp, việc định tuyến bảng mạch càng dễ dàng. Nên tham khảo ý kiến của nhà chế tạo để xác định 'mức giá' cho độ rộng và khoảng cách định tuyến, những giá trị mà nếu bạn đi dưới sẽ dẫn đến hiệu suất chế tạo thấp hơn và giá PCB cao hơn. Cũng như đáp ứng các yêu cầu điện của thiết kế, công nghệ định tuyến cũng nên được chọn để phù hợp với công nghệ linh kiện, để cho phép mỗi chân được định tuyến đến.

Quy tắc thứ ba thuộc về công nghệ định tuyến là Phong cách Via Định tuyến. Nó cũng nên được chọn để phù hợp với đường dẫn và khoảng cách sử dụng, đồng thời xem xét chi phí sản xuất của kích thước lỗ và vòng bên ngoài được chọn.

Bạn cũng nên tránh các quy tắc thừa hoặc không cần thiết - càng nhiều quy tắc, thời gian xử lý càng lâu, quá trình định tuyến càng chậm. Các quy tắc có thể được vô hiệu hóa nếu không cần thiết cho việc định tuyến tự động.

Độ Rộng Định Tuyến

Đảm bảo có một Quy tắc Độ Rộng Định Tuyến với Truy vấn Tất cả (một quy tắc mặc định), và rằng cài đặt Ưu tiên phù hợp với độ rộng định tuyến phổ biến nhất bạn yêu cầu. Đảm bảo rằng độ rộng này, kết hợp với quy tắc khoảng cách phù hợp, cho phép tất cả các pad được định tuyến đến. Cấu hình thêm các quy tắc độ rộng định tuyến cho các mạng lưới yêu cầu độ rộng định tuyến rộng hơn hoặc hẹp hơn.

Nếu có các thành phần có khoảng cách chân mảnh mà có chân trên các mạng lưới với độ rộng định tuyến rộng hơn - ví dụ, mạng lưới điện - hãy thử định tuyến ra từ một chân điện và cũng định tuyến ra chân ở hai bên để đảm bảo rằng việc định tuyến các chân này là khả thi về mặt vật lý.

Ràng Buộc Khoảng Cách

Kiểm tra các yêu cầu khoảng cách đặc biệt, chẳng hạn như các thành phần có khoảng cách chân linh kiện nhỏ hơn khoảng cách tiêu chuẩn của bảng mạch. Những yêu cầu này có thể được đáp ứng bằng cách sử dụng một quy tắc thiết kế có phạm vi và ưu tiên phù hợp. Lưu ý rằng mặc dù bạn có thể định nghĩa một quy tắc nhắm vào một bản in chân linh kiện, nó sẽ không nhắm vào việc định tuyến kết nối với bản in chân linh kiện đó. Như vừa đề cập trong phần Độ Rộng Định Tuyến, thử nghiệm định tuyến để đảm bảo rằng các chân linh kiện có thể được định tuyến.

Phong Cách Định Tuyến Via

Đảm bảo có mộtQuy Tắc Phong Cách Định Tuyến Via với một Truy vấn củaTất Cả và rằng cài đặt ưu tiên phù hợp. Bao gồm các quy tắc ưu tiên cao hơn cho những mạch cần một phong cách via khác so với quy tắc mặc định.

Altium Designer hỗ trợ vias mù và vias chôn, việc sử dụng chúng được quyết định bởi sự đổi lớp được cho phép bởi các Loại Via được định nghĩa trong Quản lý Xếp Lớp (Thiết kế » Quản lý Xếp Lớp). Giống như định tuyến tương tác, khi bộ định tuyến tự động chuyển giữa hai lớp, nó kiểm tra các định nghĩa Loại Via hiện tại - nếu các lớp này được định nghĩa là một cặp lớp mù hoặc chôn thì via được đặt sẽ có các lớp này là lớp bắt đầu và kết thúc của nó. Điều quan trọng là phải hiểu các hạn chế khi sử dụng vias mù/chôn; chúng chỉ nên được sử dụng sau khi thảo luận với nhà sản xuất của bạn. Ngoài các hạn chế do công nghệ xếp chồng sản xuất áp đặt, còn có các xem xét về độ tin cậy và khả năng truy cập kiểm tra. Một số nhà thiết kế cho rằng thêm nhiều lớp định tuyến hơn là tốt hơn là sử dụng vias mù/chôn.

Lớp Định Tuyến

Đảm bảo có một Quy tắc Lớp Định Tuyến với một truy vấn của Tất cả. Tất cả các lớp tín hiệu được kích hoạt (được định nghĩa trong xếp lớp) sẽ được liệt kê. Kích hoạt các lớp mà bạn muốn cho phép định tuyến theo yêu cầu. Bao gồm các quy tắc ưu tiên cao hơn cho các mạch mà bạn muốn được định tuyến trên các lớp cụ thể chỉ.

Nếu bạn muốn loại trừ một mạch cụ thể (hoặc một lớp mạch) khỏi việc được định tuyến bởi bộ định tuyến tự động, hãy định nghĩa một quy tắc Lớp Định Tuyến nhắm vào mạch hoặc lớp mạch đó và, trong khu vực Ràng Buộc của quy tắc đó, đảm bảo rằng tùy chọn Cho Phép Định Tuyến cho mỗi lớp tín hiệu được kích hoạt là bị vô hiệu hóa. Độ ưu tiên của quy tắc phải cao hơn so với quy tắc mặc định (quy tắc có một truy vấn của Tất Cả).

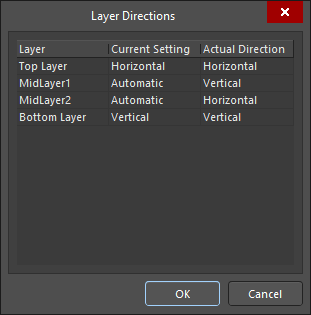

Hướng Của Lớp

Hướng định tuyến của lớp được chỉ định trong Hộp thoại Hướng Lớp, có thể truy cập từ Hộp thoại Chiến lược Định tuyến Situs. Tất cả các lớp tín hiệu được kích hoạt (được định nghĩa trong ngăn xếp lớp) sẽ được liệt kê. Chọn hướng lớp phù hợp để phù hợp với dòng chảy của các đường kết nối. Situs sử dụng bản đồ topo để xác định các đường định tuyến, do đó nó không bị giới hạn định tuyến theo chiều ngang và dọc. Thông thường, tốt nhất là có các lớp ngoài cùng theo chiều ngang và dọc. Tuy nhiên, nếu bạn có một bảng mạch nhiều lớp với số lượng kết nối lớn ở góc '2 giờ', thì hãy đặt một hoặc nhiều lớp nội bộ để có hướng định tuyến ưu tiên này. Đặc biệt, quá trình truyền Mẫu Lớp sử dụng thông tin này, và việc chọn hướng đúng có thể tạo ra sự khác biệt đáng kể đối với hiệu suất định tuyến về cả thời gian và chất lượng. Lưu ý rằng khi bạn sử dụng các lớp góc, bạn không cần phải có một lớp đối tác chạy ở góc 90 độ so với lớp này, vì bộ định tuyến thường sẽ định tuyến theo chiều ngang hoặc dọc nếu cần tránh một chướng ngại vật trên một lớp góc.

Tránh sử dụng hướng Bất kỳ - lớp được chọn để định tuyến một kết nối dựa trên mức độ kết nối được căn chỉnh chặt chẽ với hướng của lớp, vì vậy lớp này trở thành lớp cuối cùng được chọn. Hướng Bất kỳ thường chỉ được sử dụng trên các bảng mạch đơn mặt.

Ưu tiên Định tuyến

Sử dụng Quy tắc Ưu tiên Định tuyến để đặt ưu tiên cao hơn cho các mạch khó, hoặc những mạch bạn muốn có đường định tuyến sạch sẽ nhất.

Kiểm soát Phân tán SMD

Hệ thống truy vấn bao gồm các từ khóa được thiết kế đặc biệt để nhắm mục tiêu vào các gói linh kiện gắn bề mặt khác nhau bao gồm IsLCC (Leadless Chip Carrier), IsSOIC (Small Outline IC), và IsBGA (Ball Grid Array). Các quy tắc mặc định được tự động tạo ra cho các gói linh kiện phổ biến nhất và vì các lần chạy fanout được thực hiện sớm trong quá trình tự động định tuyến, nên việc giữ lại các quy tắc không áp dụng cho bất kỳ linh kiện nào cũng không gây ra nhiều hậu quả. Bạn nên có ít nhất một quy tắc thiết kế kiểm soát fanout SMD nếu có linh kiện gắn bề mặt trên bảng mạch - một truy vấn phù hợp cho một quy tắc duy nhất nhắm mục tiêu vào tất cả các linh kiện gắn bề mặt sẽ là IsSMTComponent. Để biết thông tin về cách mỗi từ khóa truy vấn xác định một gói linh kiện, mở Query Helper, nhập từ khóa cần thiết và nhấn F1.

Các quy tắc fanout bao gồm các cài đặt điều khiển liệu các pad sẽ được fan in hay fan out, hoặc là sự kết hợp của cả hai. Để giúp làm quen với hành vi của các thuộc tính quy tắc Kiểm soát Fanout, lệnh Route » Fanout » Component có thể được thực hiện trên bất kỳ thành phần gắn bề mặt nào không có mạch nối được gán cho nó. Cũng như sử dụng điều này để kiểm tra xem một thành phần fan out như thế nào với công nghệ định tuyến hiện tại được định nghĩa trong bảng mạch, bạn cũng có thể sử dụng nó để fan out một thành phần mà bạn muốn giữ trong thư viện như một dấu chân đã được fan out trước. Một khi nó được fan out trong không gian làm việc PCB, sao chép và dán thành phần và các đường dẫn fanout và vias vào một thư viện.

Ưu Tiên Quy Tắc

Thứ tự ưu tiên, hoặc mức độ ưu tiên, của các quy tắc được định nghĩa bởi nhà thiết kế. Mức độ ưu tiên của quy tắc được sử dụng để xác định quy tắc nào sẽ được áp dụng khi một đối tượng bị che phủ bởi nhiều hơn một quy tắc. Nếu mức độ ưu tiên không được thiết lập một cách chính xác, bạn có thể thấy rằng một quy tắc không được áp dụng chút nào.

Ví dụ, nếu quy tắc với truy vấn InNet('VCC') có độ ưu tiên thấp hơn so với quy tắc với truy vấn All, thì quy tắc All sẽ được áp dụng cho mạch VCC. Sử dụng nút Priorities trong hộp thoại PCB Rules and Constraints Editor dialog để truy cập vào hộp thoại Edit Rule Priorities dialog, từ đó có thể tinh chỉnh độ ưu tiên như cần thiết. Lưu ý rằng độ ưu tiên không quan trọng khi hai phạm vi quy tắc không chồng lấn (không nhắm đến cùng một đối tượng). Ví dụ, không có sự khác biệt nào giữa hai phạm vi quy tắc này về độ ưu tiên - InNet('VCC') hoặc InNet('GND').

Quy Tắc Vàng

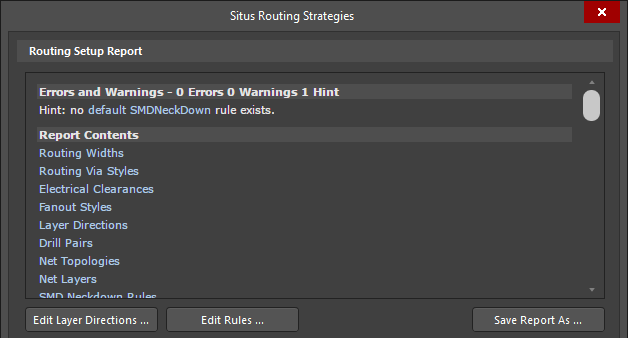

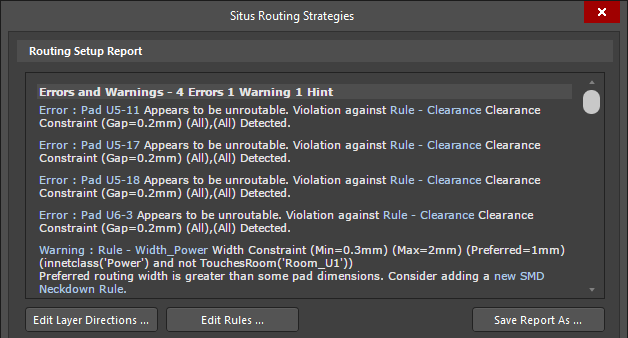

Bước quan trọng nhất là thực hiện kiểm tra quy tắc thiết kế (DRC) trước khi bắt đầu sử dụng autorouter. Khi sử dụng các lệnh Route » Auto Route » Setup, hoặc Route » Auto Route » All, Situs thực hiện phân tích trước khi định tuyến của riêng mình và trình bày kết quả dưới dạng báo cáo trong hộp thoại Situs Routing Strategies dialog.

Hãy chắc chắn rằng Báo cáo Cài đặt Định tuyến được làm sạch trước khi bắt đầu tự động định tuyến.

Báo cáo cung cấp thông tin bao gồm:

- Các quy tắc thiết kế hiện được định nghĩa cho thiết kế sẽ được tuân thủ bởi bộ tự động định tuyến (và số lượng đối tượng thiết kế - mạch, linh kiện, pad - bị ảnh hưởng bởi mỗi quy tắc)

- Hướng định tuyến được định nghĩa cho tất cả các lớp định tuyến tín hiệu

- Định nghĩa cặp lớp khoan

Báo cáo liệt kê các vấn đề tiềm ẩn có thể ảnh hưởng đến hiệu suất định tuyến. Nếu có thể, gợi ý được cung cấp nhằm tư vấn cách chuẩn bị tốt hơn cho thiết kế trước khi tự động định tuyến. Bất kỳ lỗi/cảnh báo/gợi ý nào được liệt kê đều nên được xem xét kỹ lưỡng và, nếu cần, điều chỉnh các quy tắc định tuyến tương ứng, trước khi tiến hành định tuyến thiết kế.

Kiểm tra tất cả lỗi, cảnh báo và gợi ý để hiểu những vấn đề tiềm ẩn mà bộ tự động định tuyến sẽ phải đối mặt.

Việc giải quyết bất kỳ vi phạm quy tắc liên quan đến định tuyến nào trước khi bắt đầu tự động định tuyến là cực kỳ quan trọng. Vi phạm không chỉ có thể ngăn chặn việc định tuyến tại vị trí vi phạm, mà còn có thể làm chậm đáng kể bộ định tuyến khi nó liên tục cố gắng định tuyến một khu vực không thể định tuyến được.

Mẹo khi Chạy Bộ Tự Động Định Tuyến

- Các lệnh Tự Động Định Tuyến nằm trongĐịnh tuyến » Tự Động Định Tuyến sub-menu.

- Cả hai lệnh Định tuyến » Tự động định tuyến » Tất cả và Định tuyến » Tự động định tuyến » Thiết lập đều mở hộp thoại Chiến lược Định tuyến Situs, sự khác biệt là khi bạn chọn Tất cả, hộp thoại bao gồm một nút Định tuyến Tất cả.

- Đừng ngần ngại thử nghiệm. Nếu kết quả không chấp nhận được, hãy làm gì đó để thay đổi cách tiếp cận của bộ định tuyến. Thêm các bước dọn dẹp và làm thẳng ở giữa, tạo thêm không gian xung quanh các khu vực dày đặc, hoặc thay đổi hướng của các lớp.

- Khi bạn thử nghiệm với bộ định tuyến - tạo ra các chiến lược của riêng mình để kiểm soát thứ tự của các bước, thay đổi số lượng vias với điều khiển Via, thay đổi hướng của các lớp định tuyến, hạn chế bộ định tuyến chỉ theo các tuyến đường vuông góc, và vân vân - hãy ghi chú lại các kết hợp mà bạn đã thử. Như vậy, bạn sẽ có thể xác định và tái sử dụng những cấu hình nào hoạt động tốt nhất với thiết kế của mình.

- Chạy các bước fanout một mình trước và đánh giá chất lượng. Bạn có thể cần phải fanout thủ công bất kỳ khu vực vấn đề nào.

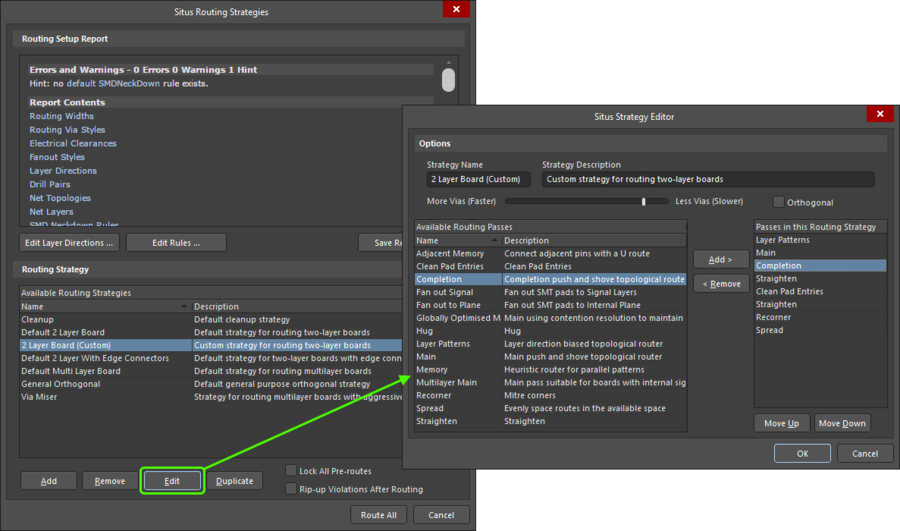

Các Bước Định tuyến và Chiến lược Định tuyến

Các chiến lược định tuyến hiện tại được liệt kê ở khu vực dưới cùng của hộp thoại Situs Routing Strategies. Nhấn vào nút Thêm để truy cập vào hộp thoại Situs Strategy Editor, từ đó bạn có thể chỉ định các bước cần bao gồm trong một chiến lược mới. Hoặc sử dụng nút Duplicate để sao chép một chiến lược hiện có, sau đó chỉnh sửa nó theo yêu cầu.

Ví dụ về chỉnh sửa một chiến lược đã được sao chép.

Chiến lược do người dùng định nghĩa có thể được chỉnh sửa bất cứ lúc nào, nhưng những chiến lược mặc định này không thể được chỉnh sửa:

- Dọn dẹp

- Mặc định 2 Lớp Board

- Mặc định 2 Lớp Với Kết Nối Cạnh

- Mặc định Đa Lớp Board

- Tổng Quát Orthogonal

- Keo Via

Các bước định tuyến sau đây có sẵn. Các bước có thể được sử dụng theo bất kỳ thứ tự nào, như một hướng dẫn xem xét một chiến lược hiện có để xem thứ tự của các bước.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ví dụ Kết quả Autorouter

Trong ví dụ này, chúng ta sẽ xem xét một bảng mạch giao diện đã được sử dụng trong một số video gần đây, và chúng ta sẽ áp dụng công cụ tự động định tuyến cho một số mạch. Mục tiêu là để xem khi nào công cụ tự động định tuyến mắc lỗi, cách công cụ xử lý các bộ quy tắc phức tạp (và có thể là tương phản) cũng như cách làm việc với công cụ nói chung.

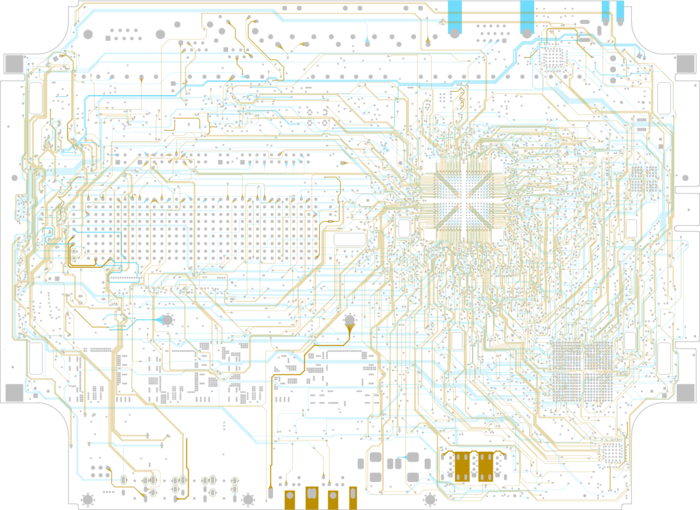

Để bắt đầu, tôi có một bảng mạch đã hoàn thành mà chúng ta sẽ sử dụng làm cơ sở trong ví dụ này; toàn bộ bảng mạch được định tuyến bằng tay. Hình ảnh dưới đây hiển thị điều này.

Bảng mạch này khá phức tạp, ít nhất là về các quy tắc cần thiết cho bố trí và định tuyến. Bảng mạch này là một bảng giao diện giữa một số kết nối SMD ở hai bên đối diện của bảng mạch. Các quy tắc bố trí bao gồm trở kháng kiểm soát cho các cặp vi sai, và bảng mạch bao gồm các lớp nội bộ cho nhiều đường ray nguồn, mặt đất, và một số kênh vi sai.

Trong ví dụ này, các cài đặt sau đã được sử dụng:

- Chiến lược định tuyến trực giao tổng quát (Trên và Dưới Ngang, SIG1 và SIG2 Dọc)

- Tất cả các tuyến đường đã được khóa

- Tất cả các mạch đều là kỹ thuật số tốc độ thấp (GPIOs và I2C), không yêu cầu kiểm soát trở kháng

- Tổng cộng, 27 mạch cần được định tuyến

Điểm cuối cùng và việc xây dựng cấu trúc chồng PCB cho phép chúng ta nói chung có thể thoát khỏi việc định tuyến các tín hiệu này được định tuyến qua nhiều lớp, qua nhiều via, và không có bất kỳ hạn chế chiều dài nào. Các bảng mạch phức tạp hơn hoặc dày đặc hơn có thể yêu cầu các thiết lập chuyên biệt hơn.

Kết quả cho các tuyến đường trong các lớp tín hiệu được hiển thị dưới đây.

Vậy kết luận là gì? Đối với trường hợp cụ thể này, các tuyến đường chỉ cần làm sạch một lỗi mạch ngắn trên lớp dưới. Đó là khá tốt khi xem xét sự sắp xếp của các chân trên kết nối ngang trên cùng. Tôi nghĩ điều này phù hợp

Suy nghĩ cuối cùng

Trong suốt bài hướng dẫn này, tôi nhận ra điều quan trọng: chiến lược sử dụng autorouter và cấu trúc định tuyến chấp nhận được trên bo mạch của bạn cần phải phù hợp. Chẳng hạn, giả sử bạn có một bo mạch đa lớp với số lượng lớn mạch, và bạn muốn thực hiện định tuyến tự động với các làn đường vuông góc; autorouter cụ thể của bạn sẽ phù hợp nhất để thực hiện chiến lược này chỉ khi có tùy chọn vuông góc được tích hợp sẵn trong autorouter của bạn. Liệu phương pháp này có phù hợp với bạn không? Tất cả phụ thuộc vào quy trình làm việc cụ thể và cách tiếp cận thiết kế của bạn.

Không phải tất cả các bo mạch đều phù hợp với điều này. Trong một số ví dụ, tôi đã chỉ ra các bo mạch nơi mà chiến lược vuông góc, chiến lược kết nối cạnh, hoặc định tuyến 2 lớp đơn giản không đáp ứng được yêu cầu hoạt động cho mọi mạch. Trong trường hợp này, việc định tuyến trước những đường mạch nhạy cảm nhất, sau đó thử định tuyến tự động cho các mạch còn lại là một ý tưởng tốt. Một ví dụ tốt tôi đã thảo luận gần đây là trong các mảng pha lớn; các đường dẫn cần phải có sự khớp pha rất chính xác, và thời gian thiết lập có thể sẽ dài hơn thời gian định tuyến và điều chỉnh thủ công của bạn. Bởi vì những đường mạch này quan trọng đến vậy, nên việc định tuyến chúng bằng tay là hợp lý.

Tôi nghĩ một công cụ tự động định tuyến chỉ tốt bằng kỹ năng của người sử dụng và mức độ cài đặt cần thiết. Nếu bạn dành thời gian để thiết lập các quy tắc cần thiết, bạn lên kế hoạch cho các nhóm mạch cụ thể để tự động định tuyến từng lần, và bạn nghĩ ra một chiến lược dọn dẹp, bạn có thể giảm thiểu công việc chỉnh sửa thủ công. Điều tuyệt vời về một công cụ tự động hóa là nó có thể được tái sử dụng cho các thiết kế khác. Một khi các hồ sơ quy tắc đã được tạo, chúng có thể được áp dụng cho việc tự động định tuyến trong các bố trí PCB khác.

Khi bạn cần truy cập vào các tiện ích tự động hóa tốt nhất cho thiết kế PCB, hãy sử dụng bộ công cụ đầy đủ về bố trí và định tuyến PCB trong Altium Designer®. Khi bạn đã hoàn thành thiết kế và muốn gửi các tệp cho nhà sản xuất của mình, nền tảng Altium 365™ giúp bạn dễ dàng hợp tác và chia sẻ các dự án của mình.

Chúng tôi chỉ mới khám phá bề mặt của những gì có thể thực hiện với Altium Designer trên Altium 365. Bắt đầu dùng thử miễn phí Altium Designer + Altium 365 ngày hôm nay.