Cấu hình một Dự án Phần cứng trong Vòng lặp

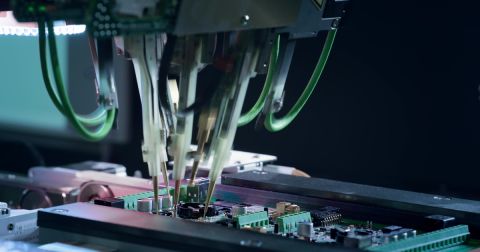

Bài viết này sẽ hướng dẫn qua một ví dụ dự án về một bảng mạch được thiết kế trong Altium Designer và thực hiện qua một luồng DevOps sử dụng kiểm thử phần cứng trong vòng lặp với firmware của nó.

Trong bài viết "Giới thiệu về Hardware in the Loop Testing", chúng tôi đã xem xét về khái niệm kiểm thử hardware in the loop (HIL) là gì, cách thiết lập như thế nào, và lý do tại sao chúng ta nên tích hợp nó vào thiết kế dự án. Bài viết này sẽ giới thiệu về một dự án ví dụ của một bảng mạch được thiết kế trong Altium Designer và chạy qua một quy trình DevOps sử dụng kiểm thử hardware in the loop đối với phần sụn của nó.

Thiết kế

Trước khi thiết lập bất kỳ cấu hình hardware in the loop nào, chúng ta cần một bảng mạch để làm việc. Một cách tốt để bắt đầu thiết kế trước khi tạo sơ đồ nguyên lý và bố cục là nguyên mẫu hóa với các bảng đánh giá. Bảng đánh giá mà chúng tôi sẽ sử dụng trong bài viết này là SAM4E XPlained Pro từ Microchip (trước đây là Atmel). Để bắt đầu, bạn sẽ cần bảng đánh giá này và cài đặt Atmel Studio. Khi bạn đã có phần cứng và phần mềm hoạt động, bạn có thể clone dự án mẫu từ Gitlab. Dự án mẫu này chứa một lượng mã tối thiểu - đủ để minh họa các khả năng của hardware in the loop testing. Dự án này cũng sử dụng một số thư viện từ Atmel Software Framework (nay được đổi tên thành “Advanced” Software Framework). ASF cung cấp các trình điều khiển cho phép giao tiếp qua USB, các hàm trì hoãn, và các thư viện khác để trừu tượng hóa nhiều triển khai phần cứng cấp thấp thường được viết cho các vi điều khiển khác. Sau khi bạn đã lấy được mã nguồn, biên dịch, và tải phần sụn, bạn đã sẵn sàng thiết lập và chạy kiểm thử hardware in the loop.

Cấu hình

Đối với quản lý phiên bản và tích hợp/triển khai liên tục (CI/CD), Gitlab đã được chọn làm nền tảng. Như được minh họa trong Cách tạo một CI/CD Pipeline cho thiết kế PCB của bạn, quản lý phiên bản và CI/CD được tích hợp thành một công cụ duy nhất trong Gitlab. Dự án này bao gồm nhiều giai đoạn CI/CD (còn được gọi là “Pipelines” trong Gitlab):

Giai đoạn đầu tiên tạo các tập tin nhị phân cần thiết để tải các tập tin lập trình lên vi điều khiển. Sau khi hoàn thành việc này, thiết bị đầu cuối (tức là bảng đánh giá) được bật nguồn. Thiết bị sau đó được lập trình và đã sẵn sàng để kiểm thử.

Kiểm thử

Kiểm thử hardware in the loop có thể đơn giản hoặc phức tạp tùy theo cách bạn thiết kế. Trong khi nhiều hệ thống HIL phức tạp yêu cầu thiết bị ngoại vi để mô phỏng các môi trường thực tế, ví dụ này sử dụng một cơ chế cơ bản để mô phỏng kích thích bên ngoài: giao tiếp nối tiếp. Giao diện USB Device CDC của Atmel tạo ra một cổng COM ảo để cho phép giao tiếp qua USB giống như bạn giao tiếp với UART qua RS-232. Trong bộ kiểm thử này chúng tôi:

- Thiết lập một thanh ghi bằng cách gửi một lệnh

- Đọc thanh ghi (để xác nhận lệnh của chúng ta)

- Xóa thanh ghi

- Đọc thanh ghi một lần nữa

Trong khi phần sụn cho vi điều khiển được viết bằng ngôn ngữ C, phần mềm kiểm thử (điều khiển các lệnh và đọc dữ liệu) được viết bằng Python sử dụng khung Pytest. Viết phần mềm bằng Python cho phép chúng ta tận dụng lợi thế của lập trình cấp cao và các thư viện, vốn sẽ đòi hỏi nhiều thời gian và công sức hơn nếu phát triển bằng ngôn ngữ biên dịch như C++. Ngoài ra, chúng ta có thể chạy các bài kiểm thử này trên bất kỳ loại máy nào mà không phụ thuộc vào hệ điều hành hoặc kiến trúc chip. Các bài kiểm thử chạy trên PC Windows (Windows, x86) cũng có thể chạy trên Raspberry Pi (Linux, ARM). Trừu tượng hóa việc phát triển, biên dịch, và kiểm thử khỏi máy của bạn là một nguyên tắc quan trọng trong quy trình làm việc DevOps. Chúng ta muốn có khả năng tái tạo một môi trường mới trong nháy mắt. Hơn nữa, chúng ta muốn tránh việc mất hàng giờ đồng hồ để thiết lập môi trường phát triển bằng cách đọc qua các hướng dẫn “Cách làm” hoặc “Bắt đầu”. Việc kịch bản hóa quy trình này (bao gồm cả kiểm thử), như đã được thực hiện trong tệp định nghĩa pipeline, đảm bảo một môi trường có thể tái tạo mà không gặp rắc rối. Để chạy các bài kiểm thử thủ công từ dòng lệnh, hãy xem tệp pipeline.

Sau khi bài kiểm thử hoàn tất, kết quả sẽ được ghi vào tệp XML của JUnit và sau đó được Gitlab phân tích và hiển thị trên giao diện web.

Bây giờ chúng ta đã minh họa đầy đủ một giải pháp từ đầu đến cuối của cấu hình hardware in the loop với Gitlab. Bạn có thể khám phá dự án để làm quen thêm với thiết lập và định dạng.

Kết luận

Trong bài viết này, chúng ta đã xem xét cách cấu hình dự án của bạn cho kiểm thử hardware in the loop. Điều này bao gồm một dự án mẫu được lưu trữ trên Gitlab mà người dùng có thể sao chép và cấu hình bằng tệp cấu hình pipeline (tức là tệp .gitlab-ci.yml). Chúng ta cũng đã đề cập đến việc chạy các bài kiểm thử bằng Python sử dụng khung Pytest và thảo luận về cách nó hiển thị trên giao diện web. Bây giờ người dùng có khả năng tạo thiết lập hardware in the loop của riêng mình bằng cách sử dụng hướng dẫn này và dự án mẫu được lưu trữ trên Gitlab.

Bạn có muốn tìm hiểu thêm về cách Altium có thể giúp bạn với thiết kế PCB tiếp theo của mình không? Hãy nói chuyện với một chuyên gia tại Altium và tìm hiểu thêm về việc đưa ra các quyết định thiết kế một cách dễ dàng và tự tin.