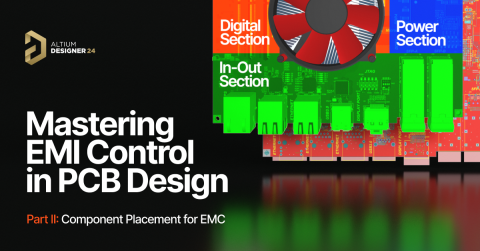

Kiểm soát EMI trong Thiết kế PCB: Phòng ngừa Crosstalk để cải thiện EMI

Chuỗi Kiểm Soát EMI Trong Thiết Kế PCB

Crosstalk Prevention for better EMI

| February 27, 2025Chào mừng bạn đến với bài viết thứ sáu trong loạt bài, Làm Chủ Kiểm Soát EMI Trong Thiết Kế PCB. Trong bài viết này, chúng ta sẽ khám phá cách mà nhiễu chéo có thể ảnh hưởng đến cả tính toàn vẹn tín hiệu và EMI, và thảo luận về các bước cần thực hiện để giải quyết vấn đề này trong thiết kế của chúng ta.

Hình 1 - Ví dụ về Thiết Kế PCB trong Altium Designer®

Nhiễu chéo là một trong những vấn đề thường gặp nhất trong thiết kế Bảng Mạch In (PCB) hiện đại. Khi mật độ của PCB tiếp tục tăng lên, hiện tượng này càng trở nên phổ biến hơn. Xu hướng tích hợp nhiều giao diện tốc độ cao vào những khu vực nhỏ hơn trên bảng mạch làm tăng thách thức, vì các bố cục gọn gàng dẫn đến khoảng cách giữa các đường dẫn gần nhau hơn, điều này đáng kể làm tăng khả năng xảy ra nhiễu chéo.

Về bản chất, nhiễu chéo tín hiệu đề cập đến sự chuyển giao không mong muốn của tín hiệu điện từ một mạng (hoặc đường dẫn) này sang một mạng khác. Điều này xảy ra khi trường điện từ được tạo ra bởi tín hiệu di chuyển dọc theo một đường dẫn tương tác với một đường dẫn liền kề. Trong bối cảnh này, đường dẫn mang tín hiệu gốc thường được gọi là "Kẻ Xâm Lược", trong khi đường dẫn nhận tín hiệu không mong muốn được biết đến là "Nạn Nhân".

Hình 2 - Ví dụ về cách nhiễu chéo có thể biểu hiện trong mạch

Trong lĩnh vực nhiễu điện từ (EMI), hiện tượng nhiễu chéo trở nên rất quan trọng bởi vì nó không chỉ là nguyên nhân gây ra sự can thiệp trong hệ thống, mà còn có thể trở thành nguồn của các bức xạ điện từ làm ảnh hưởng đến các thiết bị khác. Điều quan trọng cần nhìn nhận về nhiễu chéo là nó không chỉ xảy ra giữa các đường dẫn tín hiệu, nơi dòng điện tín hiệu lan truyền, mà còn xảy ra tại các dẫn trả về tham chiếu, nơi dòng điện trở về nguồn của nó. Đây là nơi xảy ra các hiện tượng như “bật nhảy mặt đất”, cũng là một trường hợp của nhiễu chéo xảy ra trên dẫn trả về tham chiếu.

Hiểu về Nhiễu Chéo và Ảnh Hưởng của Nó

Hiện tượng nhiễu chéo xảy ra chủ yếu vì hai lý do: sự ghép nối điện dung và ghép nối từ trường giữa các dẫn. Khi hai hoặc nhiều đường dẫn được đặt quá gần nhau, và khi điện áp và dòng điện tín hiệu thay đổi theo thời gian, các trường viền (trường điện và trường từ) ở các cạnh của đường dẫn tín hiệu (gọi là Kẻ Tấn Công) có thể ghép nối với các đường dẫn gần đó (Nạn Nhân), dẫn đến tiếng ồn không mong muốn trên các đường dẫn này.

Nhiệm vụ của nhà thiết kế PCB, về việc giảm nhiễu chéo và hiệu quả giảm EMI, là giảm thiểu ảnh hưởng của các trường viền này đối với các dẫn khác, sao cho tiếng ồn không lan truyền từ một đường dẫn này sang đường dẫn khác.

Hình 3 - Ví dụ về sự ghép nối cảm ứng và điện dung giữa các đường dẫn tín hiệu

Trong bối cảnh EMI, điều này trở thành vấn đề khi tiếng ồn tạo ra phát xạ từ các đường dẫn PCB, hoặc từ các dây nối với các đường dẫn này, hoặc các dẫn điện.

Các Loại Nhiễu Chéo

Khi xử lý nhiễu chéo, cũng quan trọng phải phân biệt giữa hai loại: Nhiễu Chéo Đầu Gần (NEXT) và Nhiễu Chéo Đầu Xa (FEXT).

Nhiễu Chéo Đầu Gần, còn được gọi là NEXT, là loại nhiễu chéo xảy ra ở cùng một đầu của đường truyền mà tín hiệu được truyền đi. Cơ bản, đó là sự can thiệp được thu nhận bởi một dẫn điện gần đó ở đầu phát của mạch.

Nhiễu Chéo Đầu Xa, hay FEXT, là nhiễu chéo xảy ra ở đầu đối diện của đường truyền từ nơi tín hiệu được truyền đi. Đó là sự can thiệp được thu nhận bởi một dẫn điện gần đó ở đầu nhận của mạch. Điểm khác biệt chính là NEXT xảy ra gần đầu nguồn, trong khi FEXT xảy ra gần đầu đích. NEXT xảy ra theo hướng ngược lại với hướng truyền tín hiệu (hướng ngược), trong khi FEXT xảy ra theo hướng của sự truyền tín hiệu (hướng tiến).

Ví dụ thực tế và chiến lược bố trí trong Altium Designer®

Không đi sâu vào các phức tạp của nhiễu chéo tín hiệu, có thể lấp đầy cả một loạt bài, có một số cách để giảm bớt hiệu ứng của nó. Hầu hết các kỹ thuật này phụ thuộc vào cách chúng ta thiết kế bố trí PCB, điều này có nghĩa là cách chúng ta thiết kế hình học PCB trở nên rất quan trọng. Các cách hiệu quả nhất để giảm nhiễu chéo, thực tế, liên quan đến cách chúng ta sắp xếp các dẫn điện so với nhau trên PCB.

Một trong những chiến lược đầu tiên chúng ta có thể sử dụng là tăng khoảng cách giữa các dẫn điện để trường điện và từ không kết hợp với nhau.

Hình 4 - Ví dụ về khoảng cách giữa các đường tín hiệu trước và sau khi cải thiện

Một kỹ thuật khác mà chúng ta có thể sử dụng là giảm khoảng cách giữa các đường tín hiệu và mặt phẳng tham chiếu trở lại. Điều này sẽ kết hợp chặt chẽ các trường tín hiệu với các mặt phẳng tham chiếu trở lại của chúng, giảm sự lan truyền của các trường này sang các dẫn điện khác.

Ngoài ra, giảm chiều dài của cả hai dẫn điện, dẫn điện tín hiệu và dẫn điện tham chiếu trở lại, sẽ giảm lượng kết hợp giữa các mạng khác nhau. Điều này cũng là trực giác, vì càng ít dẫn điện tiếp xúc, càng ít cơ hội nhiễu kết hợp với các dẫn điện khác.

Hình 5 - Hình ảnh 3D của các mặt phẳng tín hiệu và mặt phẳng tham chiếu trở về được ghép chặt với Altium Designer®

Một phương pháp phổ biến khác để giảm nhiễu chéo, được áp dụng hiệu quả cho IC, bộ kết nối, và đường dẫn PCB, là cung cấp nhiều dẫn điện cho đường trở về của các tín hiệu khác nhau.

Điều này có nghĩa, ví dụ, sử dụng nhiều đường trở về khi sử dụng cáp dải hoặc các bộ kết nối khác, thay vì sử dụng một dẫn trở về duy nhất cho nhiều mạch tín hiệu.

Chiến lược mô phỏng với Altium Designer®

Thay vì dựa vào những phỏng đoán có căn cứ về nhiễu chéo trong bố cục mạch của chúng ta, việc sử dụng các công cụ tiên tiến để tính toán chính xác là rất quan trọng.

Tính năng Tính toán Tín hiệu được tích hợp trong Altium Designer® là một công cụ mạnh mẽ cho mục đích này. Tính năng này cho phép chúng ta mô phỏng và phân tích nhiễu chéo trên các đường dẫn PCB, cho phép dự đoán chính xác và hiểu biết sâu sắc hơn về mức độ nhiễu chéo. Bằng cách sử dụng công cụ này, chúng ta có thể tinh chỉnh và tối ưu hóa thiết kế của mình với độ chính xác cao hơn.

Hình 6 - Ví dụ về mô phỏng nhiễu chéo sử dụng Altium Designer®

Công cụ Tính toán Tính toán Tín hiệu cung cấp các mô phỏng chi tiết giúp chúng tôi đánh giá các sự lựa chọn thiết kế khác nhau. Việc hiểu rõ những sự lựa chọn này là cần thiết để giảm thiểu sự can thiệp và đạt được hiệu suất tối ưu. Những hiểu biết thu được từ công cụ này đáng tin cậy hơn nhiều so với việc chỉ dựa vào đoán mò.

Hình 7 - Ví dụ về đánh giá nhiễu chéo sử dụng công cụ Tính toán Tín hiệu trong Altium Designer®

Việc tận dụng công cụ tiên tiến này giúp chúng tôi đưa ra quyết định thông minh, cân bằng nhu cầu về hiệu suất với các hạn chế về bố cục. Cách tiếp cận này nâng cao cả độ tin cậy và chức năng của mạch của chúng tôi, cải thiện tính toàn vẹn tín hiệu và hiệu suất EMI đồng thời tăng hiệu quả thiết kế tổng thể.

Kết luận

Kết luận, để giảm hiệu quả nhiễu chéo tín hiệu và cải thiện hiệu suất EMI của các bảng mạch PC của chúng tôi, chúng tôi có một số chiến lược có sẵn. Việc sử dụng công cụ Tính toán Tín hiệu tích hợp trong Altium Designer là không thể thiếu để dự đoán và giảm thiểu nhiễu chéo trong bố cục PCB của chúng tôi một cách chính xác. Công cụ này trao quyền cho chúng tôi đưa ra quyết định dựa trên dữ liệu, đảm bảo rằng các thiết kế của chúng tôi đáp ứng các yêu cầu đặc tả và hoạt động đáng tin cậy dưới các điều kiện khác nhau.

Nếu bạn đã bỏ lỡ bất kỳ bài viết nào trong loạt bài "Làm chủ Kiểm soát EMI trong Thiết kế PCB" toàn diện, chúng tôi khuyến khích bạn truy cập các trang của Altium để cập nhật tất cả nội dung sâu sắc.

Hãy chắc chắn theo dõi Altium trên các nền tảng truyền thông xã hội khác nhau để cập nhật những tin tức, bài viết và thông tin mới nhất liên quan đến thiết kế PCB.

Nếu bạn đang tìm cách nâng cao và cải thiện các dự án thiết kế PCB của mình, và nếu bạn muốn tận dụng tối đa các công cụ tiên tiến giúp đơn giản hóa và tối ưu hóa quy trình thiết kế, chúng tôi rất khuyến khích bạn xem xét bắt đầu dùng thử miễn phí Altium Designer® và Altium 365™.

Những công cụ tiên tiến này cung cấp một loạt các tính năng mạnh mẽ được thiết kế để cải thiện hiệu quả và hiệu suất của quy trình thiết kế của bạn, giúp bạn dễ dàng đạt được kết quả chất lượng cao trong các dự án PCB của mình.