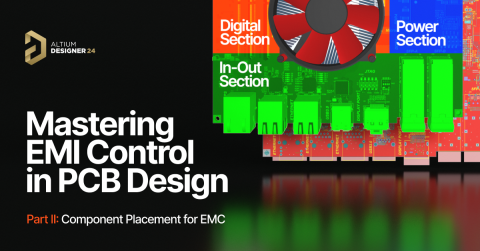

Làm chủ kiểm soát EMI trong Thiết kế PCB: Cách chọn Stackup cho Thiết kế EMC

Mastering EMI Control in PCB Design Series

How to Choose the Stackup for EMC Design

| December 3, 2024Một trong những khái niệm quan trọng nhất cần nắm vững khi thiết kế PCB có khả năng vượt trội về Khả năng Tương thích Điện từ (EMC) là lựa chọn cấu trúc các lớp của PCB.

Hình 1 - Công cụ Quản lý Cấu trúc Lớp trong Altium Designer

Điều này trở thành một trong những khía cạnh quan trọng nhất vì nó liên quan chặt chẽ đến việc giữ các trường điện từ trong thiết kế PCB của chúng ta.

Trong bài viết thứ ba của loạt bài Làm chủ Kiểm soát EMI trong Thiết kế PCB, chúng ta sẽ khám phá thêm về những khái niệm này, và chúng ta cũng sẽ xem xét các khái niệm EMC quan trọng khác.

Để một tín hiệu có thể lan truyền trong mạch, nó đòi hỏi hai dẫn truyền để tạo thành một vòng lặp dòng điện hoàn chỉnh. Một dẫn truyền mang tín hiệu, và dẫn truyền kia cung cấp đường trở về, đảm bảo rằng dòng điện có thể chảy, và tín hiệu có thể được truyền đi một cách hiệu quả. Một trong những dẫn truyền chúng ta gọi là dẫn truyền tín hiệu, và dẫn truyền kia chúng ta gọi là dẫn truyền trở về và dẫn truyền tham chiếu. Dẫn truyền tham chiếu trở về được đặt tên như vậy bởi vì nhiệm vụ của nó không chỉ là cung cấp tham chiếu (hoặc điện áp không) cho tín hiệu, mà còn bởi vì nó phải cung cấp đường dẫn có trở kháng thấp nhất cho dòng điện tín hiệu trở về nguồn phát ra nó. Để đạt được đường dẫn có trở kháng thấp nhất, cấu hình tốt nhất sẽ là chọn một mặt phẳng, thay vì một đường dẫn, và mặt phẳng này không nên có bất kỳ đứt gãy, cắt, hoặc phân đoạn nào có thể tạo ra sự không liên tục về trở kháng cho các tín hiệu.

Từ khái niệm cơ bản này, chúng ta có thể thấy rằng cho mỗi lớp mà chúng ta có một tín hiệu, chúng ta cần phải có dẫn truyền thứ hai, mặt phẳng tham chiếu trở về, cung cấp đường trở và tham chiếu. Bằng cách tuân theo quy tắc đơn giản này, chúng ta sau đó có thể quyết định cách thiết kế các cấu trúc xếp chồng của mình, chỉ đơn giản bằng cách ghép mỗi lớp tín hiệu với Mặt Phẳng Tham Chiếu Trở Về (RRP) liền kề.

Dưới đây là một số ví dụ về cách xếp chồng các lớp sẽ giúp giảm thiểu nhiễu điện từ tối đa.

Ví dụ về xếp chồng 2 lớp

Đối với xếp chồng 2 lớp, chúng ta có thể có một cấu hình nơi một lớp được dành riêng cho các tín hiệu và đường dẫn nguồn, trong khi lớp thứ hai là một mặt phẳng tham chiếu trả về liền mạch.

Hình 2 - Ví dụ về xếp chồng 2 lớp với công cụ Layer Stack Visualizer trong Altium Designer

Mặt phẳng này không nên có các đường cắt hoặc các khoảng trống lớn khác. Điều này cũng quan trọng để tránh đặt tín hiệu qua các khoảng trống, có thể tạo ra sự không liên tục về trở kháng và làm tăng đường dẫn vòng dòng điện, cuối cùng làm tăng phát xạ bức xạ. Nếu chúng ta có các đường dẫn cần phải chuyển từ lớp này sang lớp khác, chúng ta muốn đảm bảo rằng việc chuyển giao là ngắn nhất có thể và không được thực hiện dưới các đường dẫn tín hiệu khác.

Ví dụ cho xếp chồng 4 lớp

Cùng một cách tiếp cận có thể được sử dụng cho xếp chồng 4 lớp. Xếp chồng này phù hợp khi mật độ thành phần và đường dẫn tăng lên và cần một lớp thứ hai để định tuyến các đường dẫn tín hiệu. Mặc dù xếp chồng 3 lớp có thể đạt được cấu hình tương tự, nhưng nó thường không phải là lựa chọn tốt nhất cho mục đích sản xuất, vì các nhà sản xuất thường cung cấp xếp chồng lớp theo cặp.

Đối với cấu hình 4 lớp, có hai cấu hình hiệu quả:

-

Cấu hình đầu tiên có các mặt phẳng tham chiếu trả về được nhúng vào trong cấu hình. Điều này có nghĩa là lớp 1 và lớp 4 sẽ là các lớp tín hiệu, trong khi lớp 2 và 3 sẽ cung cấp trả về và tham chiếu cho các tín hiệu trên lớp 1 và 4, tương ứng.

-

Cấu hình thứ hai có các mặt phẳng tham chiếu trả về ở lớp 1 và 4, hoạt động như một loại lá chắn cho mạch, trong khi các lớp tín hiệu nằm ở lớp 2 và 3, được nhúng vào trong cấu hình. Trong cấu hình này, chúng ta muốn tăng khoảng cách giữa lớp 2 và 3 để các trường của cả hai tín hiệu không gây nhiễu lẫn nhau. Thay vào đó, mỗi lớp tín hiệu sẽ kết hợp với các mặt phẳng tham chiếu trả về.

Trong cả hai cấu hình, vias nối cũng nên được thực hiện giữa các mặt phẳng tham chiếu trả về. Mục đích chính của việc này là:

-

Tạo ra một loại lá chắn Faraday để giảm bức xạ và nhiễu từ bên ngoài;

-

Giữ cho các mặt phẳng càng đồng điện thế càng tốt và giảm điện áp chế độ chung;

-

Cung cấp trả về và tham chiếu cho các tín hiệu chuyển đổi theo chiều dọc từ lớp này sang lớp khác.

Trong trường hợp này, nguồn điện cũng sẽ được định tuyến trên các lớp tín hiệu.

Hình 3 - Ví dụ về cấu trúc 4 lớp với công cụ Layer Stack Visualizer trong Altium Designer

Trường hợp có một lớp hoàn toàn dành riêng cho nguồn trong cấu trúc 4 lớp được cố ý bỏ qua, vì điều này không được khuyến nghị cho mục đích thiết kế EMC do nó có thể tạo ra tiếng ồn điện áp chung nếu không thực hiện đúng cách. Chủ đề này đòi hỏi nhiều kỹ thuật chuyên sâu hơn, chúng tôi sẽ để dành cho một lần khác.

Ví dụ cho cấu trúc 6 lớp

Cấu trúc 6 lớp cung cấp một mức độ tự do cao hơn trong cách chúng ta phân bổ các lớp tín hiệu và nguồn.

Hình 4 - Ví dụ về cấu trúc 6 lớp với công cụ Layer Stack Visualizer trong Altium Designer

Hai cấu trúc rất hiệu quả có thể cung cấp hiệu suất xuất sắc về mặt EMC:

-

Xếp chồng 1: Tín hiệu được định tuyến trên các lớp 1 và 6, với các lớp tham chiếu trả về trên các lớp 2 và 5, và các lớp tín hiệu bổ sung trên các lớp 3 và 4. Cấu hình này cho phép các lớp 2 và 5 đóng vai trò là các lớp tham chiếu và trả về cho tất cả bốn lớp tín hiệu, thay vì chỉ hai lớp. Điều này được làm cho khả thi bởi hiệu ứng bề mặt, cho phép các dòng điện khác nhau trên mỗi bên của các lớp mà không bị trộn lẫn. Hiệu ứng bề mặt cơ bản là xu hướng của dòng điện xoay chiều (AC) phân bố chính nó trong một dẫn truyền sao cho mật độ dòng điện lớn nhất gần bề mặt của dẫn truyền, giảm dần về phía trung tâm. Hiện tượng này xảy ra bởi vì từ trường thay đổi được tạo ra bởi AC gây ra các dòng điện xoáy chống lại dòng điện chảy ở trung tâm của dẫn truyền, buộc dòng điện chảy nhiều hơn ở phía ngoại vi. Trong loại xếp chồng này, các mạng điện có thể được định tuyến cùng với các lớp tín hiệu.

-

Xếp chồng 2: Tín hiệu được định tuyến trên các lớp 1 và 6, với các lớp 2 và 5 đóng vai trò là các lớp tham chiếu trả về. Trong cấu hình này, các lớp 3 và 4 được sử dụng làm mặt phẳng nguồn. Xếp chồng này rất hiệu quả, đặc biệt là khi cần nhiều nguồn điện hơn hoặc cần một mạng lưới cung cấp điện có trở kháng thấp. Nên sử dụng các mặt phẳng đồng nhất, đặc cho cả các lớp tham chiếu trả về và các lớp nguồn. Không nên sử dụng các đa giác khác nhau trên một lớp duy nhất, vì điều này có thể tạo ra tiếng ồn chế độ chung và dẫn đến phát xạ bức xạ khi kết nối cáp. Dành riêng một mặt phẳng cho mỗi điện áp để tránh những vấn đề này và cải thiện mạng lưới cung cấp điện (PDN) của bảng mạch.

Như với xếp chồng 4 lớp, hãy đảm bảo có khoảng cách đủ giữa các lớp tín hiệu và nguồn nội bộ để tránh sự kết hợp giữa chúng, trong khi tối đa hóa sự kết hợp với các lớp tham chiếu trả về. Cũng nên thực hiện việc may vias giữa các mặt phẳng tham chiếu trả về khi có thể.

Ví dụ về Xếp chồng Đa lớp Đơn giản với Altium Designer

May mắn thay, việc chọn xếp chồng PCB trở nên dễ dàng hơn với Altium Designer®.

Với công cụ Quản lý Xếp lớp tích hợp, bạn có thể tạo các xếp lớp tùy chỉnh cho PCB của mình hoặc sử dụng các xếp lớp có sẵn, làm cho công việc của nhà thiết kế PCB trở nên dễ dàng hơn nhiều. Công cụ Quản lý Xếp lớp cũng cho phép bạn tạo các loại xếp lớp nâng cao hơn, nơi bạn cũng có thể tính toán trở kháng đặc trưng cho tín hiệu của mình mà không cần đến các máy tính bên thứ ba.

Đây là một trong số nhiều tính năng của Altium Designer® giúp việc tạo dự án PCB trở nên mượt mà và chính xác, làm cho quá trình thiết kế không chỉ dễ dàng hơn mà còn thú vị hơn.

Trong bài viết tiếp theo, chúng tôi sẽ khám phá cách thiết kế và tối ưu hóa PCB cho EMI thấp. Hãy chắc chắn theo dõi các trang và mạng xã hội của chúng tôi để bạn không bỏ lỡ.

Trong thời gian chờ đợi, bạn có thể bắt đầu dùng thử miễn phí Altium Designer® + Altium 365™ ngay hôm nay và nâng cấp dự án thiết kế PCB của mình lên một tầm cao mới.