Dự án Pi.MX8 - Phần Sắp xếp Bảng mạch 3

Chương

Board Layout Part 3

| Created: June 24, 2024PCB Assembly

| Coming soonChào mừng bạn đến với phần mới của dự án mô-đun máy tính mã nguồn mở Pi.MX8! Trong loạt bài này, chúng tôi sẽ đi sâu vào thiết kế và kiểm thử một hệ thống trên mô-đun dựa trên bộ xử lý i.MX8M plus từ NXP.

Trong bản cập nhật trước, chúng tôi đã hoàn thành các bước chuẩn bị bố trí. Điều này bao gồm việc tạo các hồ sơ trở kháng, thêm các quy tắc thiết kế theo thông số kỹ thuật của nhà sản xuất bảng mạch và xác định các khu vực nơi các quy tắc thiết kế đặc biệt nên được áp dụng. Chúng tôi cũng đã hoàn thành việc định tuyến giao diện LPDDR4 nhưng chưa điều chỉnh chiều dài (tạm thời).

Trước khi chúng tôi bắt đầu điều chỉnh chiều dài của giao diện DRAM, chúng tôi sẽ xem xét việc định tuyến của các giao diện còn lại trên mô-đun Pi.MX8. Có khá nhiều bus tốc độ cao và thấp trên bảng mạch, một số trong số đó là các bus song song rộng lớn chiếm nhiều không gian định tuyến. Để cung cấp đủ không gian cho mỗi giao diện, trước tiên chúng tôi sẽ tạo một kế hoạch sơ bộ cho mỗi lớp định tuyến trên mô-đun.

Kế hoạch định tuyến

Kế hoạch định tuyến sẽ giúp chúng ta xác định cách phân phối tất cả các giao diện tốc độ cao và thấp trên các lớp tín hiệu có sẵn. Bằng cách thiết lập một hướng dẫn sơ bộ trước, chúng ta có thể đảm bảo rằng mình có đủ không gian định tuyến trên lớp mà chúng ta đang làm việc. Điều này cũng giúp chúng ta giảm thiểu việc chuyển lớp và giảm lượng công việc chỉnh sửa phải làm trong quá trình định tuyến.

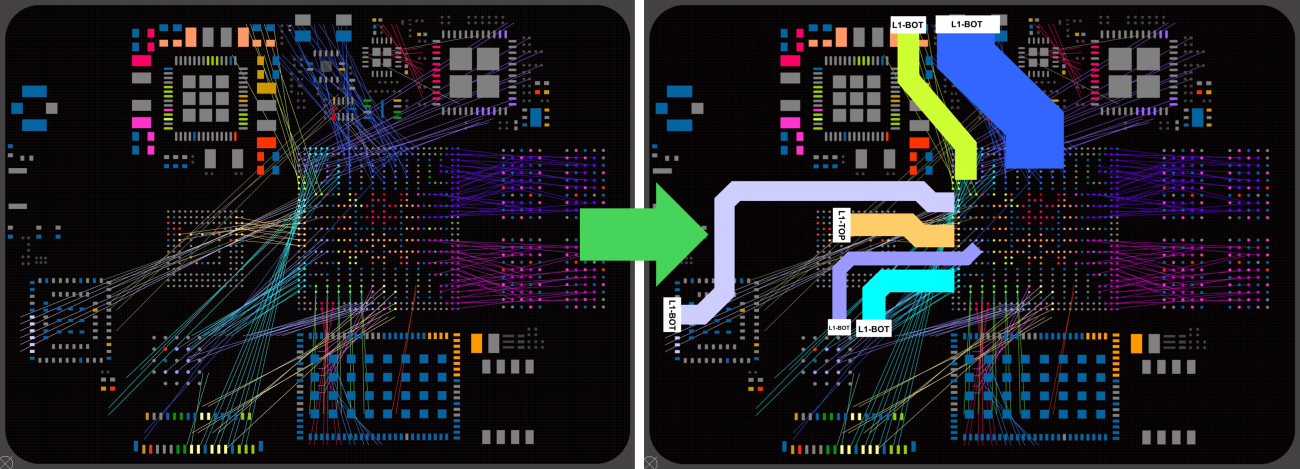

Có một số cách để thiết lập kế hoạch bố trí, chủ yếu phụ thuộc vào các công cụ có sẵn. Chúng ta chỉ cần một công cụ vẽ cơ bản cho phép chúng ta phác thảo trên một hình ảnh hiện có. Trong ví dụ này, chúng ta sẽ sử dụng Inkscape.

Trong Inkscape, chúng ta có thể thêm một hình ảnh nền hiển thị vị trí đặt các linh kiện và các giao diện chưa được định tuyến dưới dạng các dây không màu. Lưu ý rằng các mạng điện được ẩn trong ảnh chụp màn hình này vì chúng ta chỉ tập trung vào các mạng sẽ được định tuyến trên các lớp tín hiệu. Trong sơ đồ, chúng ta đã đặt một chỉ thị lớp mạng trên mỗi mạng điện, giúp dễ dàng xác định các mạng nào được định tuyến trên các lớp mặt bằng chỉ bằng cách kích hoạt hoặc ẩn lớp mạng liên quan trong trình biên tập bố trí.

Đối với quá trình định tuyến thực tế, chúng tôi chỉ cần thêm các đường vào trong Inkscape để đại diện cho các giao diện mà chúng tôi muốn định tuyến trên lớp tương ứng. Chúng tôi có thể điều chỉnh độ rộng của những đường này để thể hiện số lượng tín hiệu sẽ được định tuyến trong giao diện. Màu sắc của đường có thể được chọn từ hình ảnh nền để dễ dàng xác định giao diện nào đang được đại diện.

Do các chuyển đổi lớp cũng cần không gian được phân bổ trên tất cả các lớp, chúng tôi có thể thêm một khối ở cuối mỗi đường chi tiết về sự chuyển đổi lớp.

Lập kế hoạch bố trí trong Inkscape với ảnh nền là ảnh chụp màn hình của Altium Designer

Một khi chúng tôi đã lặp lại quá trình trên cho mỗi lớp định tuyến, chúng tôi có thể tiến hành bắt đầu quá trình định tuyến thực tế.

Định tuyến lớp trên cùng

Với một chiến lược định tuyến đã được đặt ra, hãy bắt đầu bằng việc định tuyến các giao diện trên lớp trên cùng. Vì chúng ta đã thực hiện định tuyến phân phối cho các thành phần trên lớp trên cùng, chúng ta có thể sử dụng tất cả không gian còn lại cho việc định tuyến tín hiệu. Không còn nhiều không gian, nhưng những gì chúng ta có vẫn có thể được sử dụng để làm cho việc định tuyến trên các lớp tín hiệu bên trong dễ dàng hơn bằng cách đặt các VIA một cách chiến lược ở những khu vực không gây cản trở việc định tuyến trên các lớp bên trong sau này. Đây là một lợi ích khác của việc lên kế hoạch bố trí trước, nếu không những khu vực này sẽ không được xác định ở giai đoạn này.

Định tuyến lớp trên cùng của mô-đun PiMX8

Khi đặt các đường dẫn trên lớp trên cùng, chúng ta cũng nên xem xét rằng chúng ta cần một số không gian để thêm các tính năng như fiducials hoặc nhãn trên lớp trên cùng. Mã ma trận dữ liệu khắc bằng laser cũng có thể yêu cầu một khu vực đồng rắn hoặc một khu vực không có đường dẫn để cung cấp độ tương phản đồng nhất, nghĩa là những khu vực này không thể được sử dụng cho việc định tuyến.

Định tuyến Lớp Tín hiệu Bên trong

Hầu hết các kết nối sẽ được đặt trên hai lớp tín hiệu bên trong mà chúng tôi đã định nghĩa trong trình quản lý xếp lớp. Hãy bắt đầu bằng việc định tuyến tất cả các giao diện đồng bộ tốc độ cao. Trong trường hợp của chúng tôi, đó có thể là các giao diện MIPI-CSI, MIPI-DSI và LVDS. Các giao diện này đều sử dụng tín hiệu chênh lệch điện áp thấp và mang theo một dòng clock chuyên dụng và ít nhất hai dòng dữ liệu. Chúng đòi hỏi nhiều không gian định tuyến vì chiều dài của mỗi dòng dữ liệu phải được khớp với dòng clock trong một khoảng thời gian nhất định. Việc khớp chiều dài của nhiều cặp chênh lệch có thể yêu cầu nhiều không gian, vì rất có thể một hoặc nhiều cặp trong giao diện sẽ gây ra độ trễ đáng kể cần phải được tính toán. Bằng cách định tuyến các giao diện này trước, chúng tôi có thể đảm bảo rằng sẽ có đủ không gian cho việc điều chỉnh chiều dài sau này.

Việc đặt các VIA đường trở về gần với các chuyển tiếp lớp của các cặp chênh lệch tốc độ cao này cũng quan trọng để đảm bảo tính toàn vẹn tín hiệu. Các VIA đường trở về có thể chiếm không gian trên nhiều lớp, vì vậy các VIA này nên được đặt ngay khi một chuyển tiếp tín hiệu được đặt.

Tiếp theo, chúng ta có thể định tuyến các giao diện tốc độ cao khác như PCIe, USB, HDMI và Ethernet. Những giao diện này có yêu cầu không nghiêm ngặt về việc khớp chiều dài giữa các cặp, vì vậy chúng ta không cần phải dành nhiều không gian cho việc khớp chiều dài. Tuy nhiên, việc quản lý đường trả về chắc chắn và áp dụng các phương pháp thiết kế tốc độ cao cơ bản trên những tín hiệu này vẫn rất quan trọng mặc dù đặt chúng ở vị trí thứ hai trong danh sách ưu tiên định tuyến.

Cuối cùng nhưng không kém phần quan trọng, chúng ta có thể định tuyến các giao diện tốc độ thấp còn lại như SDIO, GPIO, RGMII và các bus khác như UART hoặc I2C và SPI. Những giao diện này vẫn hoạt động ở tốc độ cạnh cao, điều này có nghĩa là chúng ta vẫn cần xử lý chúng như các tín hiệu tốc độ cao.

Định tuyến lớp tín hiệu bên trong 1

Định tuyến lớp tín hiệu bên trong 2

Định tuyến lớp dưới cùng

Trong trường hợp của bảng mạch PiMX8, chúng ta có thể xem lớp dưới cùng như một lớp định tuyến bên trong về mặt không gian sẵn có. Hầu hết các thành phần hoạt động được đặt trên lớp trên cùng của mô-đun, chỉ để lại một số ít các bộ điều chỉnh điện áp và các thành phần bị động như tụ bù và điện trở cấu hình trên lớp dưới cùng.

Ưu tiên định tuyến trên lớp dưới cùng giống như đối với các lớp bên trong, vì vậy chúng ta sẽ bắt đầu với các giao diện MIPI-CSI, MIPI-DSI và LVDS. Trên mô-đun PiMX8, một bộ đa hợp tốc độ cao có thể chọn giữa các cổng DSI và LVDS. Thành phần này được đặt trên lớp dưới cùng gần với kết nối giữa các bảng mạch. Do bố trí chân của bộ đa hợp, có một độ trễ đáng kể trên một trong những đường tín hiệu kết nối với bộ đa hợp. Chúng ta sẽ phải xem xét kỹ lưỡng hơn trong quá trình khớp chiều dài, nhưng chúng ta cần dành một ít không gian trên lớp dưới cùng để cho phép một độ trễ lớn hơn.

Bố trí chân của bộ đa hợp với một đường dài trong giao diện

Định tuyến lớp dưới cùng mô-đun PiMX8

Có một số tình huống trên mô-đun PiMX8 yêu cầu sự chú ý đặc biệt trong quá trình điều chỉnh độ trễ. Chúng ta sẽ sử dụng rộng rãi X-signals để vượt qua một số thách thức này. Những thách thức cụ thể là gì, và làm thế nào chúng ta có thể triển khai X-signals để cung cấp việc điều chỉnh độ trễ chính xác trên một thành phần được chia sẻ bởi nhiều giao diện, sẽ là một phần của bản cập nhật tiếp theo. Hãy chờ đón!