PCB Design ⚯ 支持

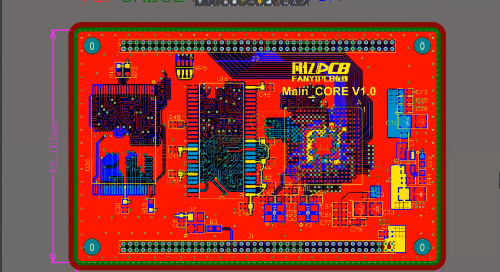

欢迎来到充满灵感和创新的 PCB 设计世界。我们非常感激我们出色的社区帮助我们在电子开发领域培养合作与增长。我们希望与您分享我们在几十年的研究和创新过程中积累的知识和经验,包括创建 Altium Designer,PCB 设计软件 和 Altium 365,敏捷的电子开发平台。

探索我们的资源,以拓展您的 PCB 开发技能,并了解前沿技术以及成功的客户实践。我们的资讯文章和实用资源旨在帮助电子工程师和开发者比以往任何时候都更快地将更成功的产品推向市场。快来潜入其中,激发灵感吧!

CoDesign and CoEngineering (ECAD/MCAD Collaboration)

With helpful guides and productivity tips for using that latest features, you can learn straight from the engineers behind Altium Designer, the electronic industry's most advanced PCB Design Software.

Component Management and Libraries

Discover the latest resources and guides for Altium 365, the collaborative cloud-based electronics development platform connecting product designers, procurement teams, electrical engineers, mechanical engineers, and electronics design companies.

沪公网安备 31010502006411号

沪公网安备 31010502006411号