什么是芯片组件以及它们在封装中如何使用?

芯片是具有专门功能的小型集成电路(IC)芯片。这些设计用于组合成一个更大的集成电路,遵循半导体行业的异构集成趋势。从一系列小型、高度专业化的芯片中进行选择,然后将这些芯片混合匹配以产生所需的整体功能,这是从传统的片上系统(SoC)方法到半导体封装的一大进步。主要供应商已经生产了计算机处理器,这些处理器结合了选定数量的芯片,而不是走传统的单片半导体制造路线,在这种路线中,设备是在单片硅上制造的。

尽管芯片的概念已经存在了几十年,基于芯片的封装正在推动专门应用的新型组件、产品和系统的发展。这些组件针对特定应用进行了定制,越来越多的公司开始参与芯片设计游戏,以芯片作为其核心处理器。基于你在网上找到的研究论文、专利申请和技术文章的数量,很明显,基于芯片的组件将持续存在。

如果你是一名系统设计师,并且你在权衡处理器选项,你可能没有意识到芯片构成了你系统的基础。然而,芯片是支持现代芯片中发现的多样化功能的骨干,封装概念正在继续推动新功能的集成到芯片设计中。示例包括将FPGA块和AI加速器块与存储器、CPU甚至RF组件集成到同一封装中。

为什么选择芯片?

成本和性能是芯片设计和制造中最紧迫的两个问题。近年来,Dennard缩放和摩尔定律放缓,导致工艺技术节点之间的时间跨度变长。此外,随着设备缩放的可选项越来越少,单片芯片上的晶体管集成变得越来越具有挑战性。这些挑战由于制造过程成本更高而降低了单片半导体的投资回报率。

在相同晶体管尺寸的情况下,增加集成功能单元的唯一方法是扩大芯片面积,无论是在设备平面还是垂直方向上。增加芯片面积的问题在于,更大的芯片更容易受到制造缺陷的影响,这限制了晶圆产量并增加了交付给客户的产品价格。因此,随着计算需求的增加,单片芯片越来越无法提供所需的性能。

因此,为了支持像设备上的AI/ML、超快网络、传感器融合和下一代移动设备等高计算应用,我们已经看到了基于芯片组的系统的出现,这对于成本有效地开发高性能电子产品至关重要。这已经从高级SoC扩展到桌面/服务器处理器和GPU。

攀越“面积墙”

“面积墙”问题是由于高性能计算系统对大面积芯片的需求与半导体制造的低产量之间的不匹配造成的。面积墙指的是在单片半导体制造中的这一挑战,其中使用更大的芯片来增加特性密度,但缺陷计数也随之增加。随着制造处理能力转向更先进的节点,过程产量减少,因此最终客户的成本增加。因此,通过消除缺陷的机会来降低这些产品的制造风险始终是一个动力。

解决面积墙问题将通过在制造过程中减少浪费来降低最终产品的总成本。芯片组本质上通过将风险分散到多个半导体模块上来多样化产品的风险概况。最终结果是成本降低,并且与单片组件相比,功能的多样化程度大大提高。

成本降低

多个芯片组通过特殊的封装技术组合成一个更大的IC,作为单片结构的替代方案。由于芯片组在较小的区域上制造,通常在圆形晶圆上,制造缺陷的影响减少,面积利用率增加。因此,成本降低,因为当使用芯片组创建组件时,晶圆产量显著提高。

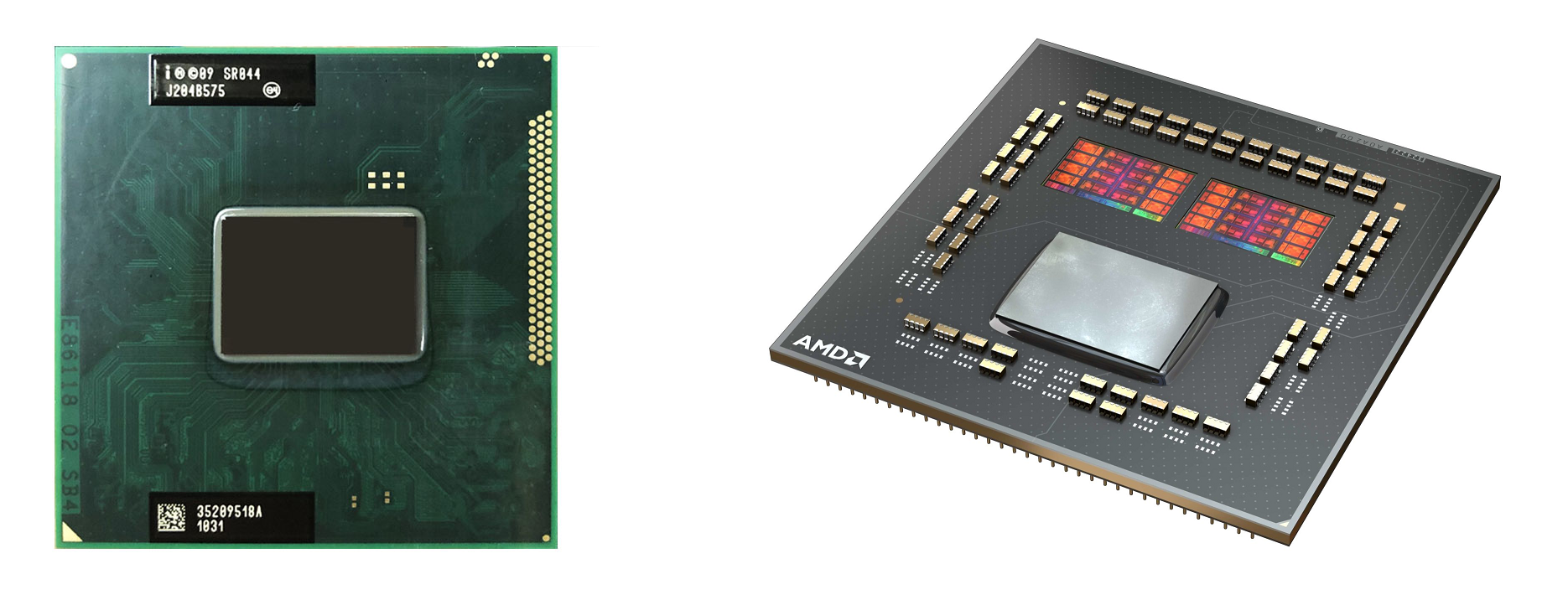

异构集成是芯片组的另一个显著优势,特别是在降低IC设计和生产成本方面。每个芯片组可以使用不同的工艺节点制造,这是AMD透露其Ryzen 7产品所采用的方法。AMD的另一个例子是最近针对基于芯片组的GPU的专利;该系统的架构在下面的原始艺术作品中显示:

这种方法还可以将多种材料(例如,GaN和Si芯片组)组合到同一个封装中。使用不同的工艺技术节点降低了产品内置的总体风险;最高风险仅限于在最先进的工艺节点生产的芯片组,而不是整个芯片。

设计复用

一旦开发了芯片组,就可以重复使用,从而降低了测试和验证的成本。通过使用芯片组模块,芯片设计过程的成本效率显著提高,因为它们可以被重复使用。芯片组重用的一个场景是,只设计和制造IC的核心芯片组,而包装中的其余芯片组则从另一个供应商处获得。采用这种方法,使用来自多个供应商的现成芯片组,或者在新设计中重用IP,大大降低了产品的总体设计和验证成本。

如果系统需要任何更新,可以在包装内将一个芯片组更换为另一个芯片组。请注意,包装本身可能需要更新,但这比重新设计整个单片组件要容易得多。系统的一小部分也可以重新设计,而不会产生在单片半导体封装中出现的新的验证成本。这种芯片组重用方法被称为“异构重用”。

芯片组重用的另一个场景是将多个相同的芯片组集成到同一系统中。这种方法非常适合可扩展系统,并在降低成本的同时显著提高其效率。这被称为同质重用方法,其主要优势是,增加架构中的芯片组数量就可以满足各种性能和功耗要求。

芯片组封装技术

要制造基于芯片组的产品,你需要设计技能、芯片、芯片之间的连接以及生产策略。芯片组封装技术的性能、价格和成熟度对芯片组的应用有着重大影响。根据连接介质和方法的不同,用于芯片组互连的封装技术可以分为三类:

-

基板封装

-

硅中介层封装

-

再分配层(RDL)封装

-

嵌入式多芯片互连桥(EMIB)

基于基板的封装

在基于基板的封装中,流行的基板选择是有机材料,因为这些材料容易获得。类似于传统的PCB,通过蚀刻过程进行布线连接,该过程独立于半导体制造中使用的其他过程。这被认为是2D异构集成的最早形式。

通过翻转芯片设计或堆叠,可以轻松地将几个芯片连接到具有高密度的基板上。此外,与之相关的材料和制造成本最小,因为这项技术不依赖于芯片制造过程。使用这项技术的主要缺点是I/O引脚的密度低,导致这些封装中的互连带宽受到限制。

硅中介层封装

这项技术涵盖了2.5D和3D封装技术,其中芯片在互连器(2.5D)上横向构建或垂直堆叠(3D)。为了实现芯片间的互连和通信,硅互连器层被放置在基板和芯片之间。互连器就像一个微型的印刷电路板,本质上提供了一个用于芯片间电连接的基底。互连织物由金属接触(称为微凸点)和贯穿硅的通孔(TSV)构成,这些内部在封装中运行。这些用于将芯片连接到互连器,以及将互连器连接器连接到具有BGA焊盘图案的封装基板。

这些产品具有更高的I/O密度,功耗降低且传输延迟更低。这得益于微凸点和TSV之间的痕迹长度和间距更小。这项技术唯一的显著缺点是制造成本增加。

RDL封装

重新分布层(RDL)封装技术不使用基板,而是直接在晶圆的顶表面直接沉积介电质和金属。这项技术也被称为“扇出”技术。为了承载线路设计,构建一个重新分布层,使得每个芯片上的I/O端口围绕设备形状。通过缩短电路长度,RDL提供了更好的信号完整性(损失和失真更低)。

嵌入式多芯片互连桥

EMIB是一种技术,使用薄硅晶圆片段嵌入有机材料作为芯片间互连的基底。在高级产品中的高成本问题可以通过使用具有多样芯片的桥接封装来解决。这种混合封装技术是基于基板和基于互连器封装的结合。薄硅层,通常小于75微米,涂覆在基板上用于形成芯片间连接,这些层嵌入在有机基底层中。

这个概念遵循在HDI PCB中使用的ELIC中的相同理念,其中每层互连织物将多个芯片连接到绝缘(有机)基底的内层。EMIB部分的封装是一个硅桥,提供了芯片间的高带宽连接。

结论

预计芯片将继续革新需要高计算组件以及单一封装中的多样功能的应用。这些产品目前针对高级技术,如5G、物联网、汽车、边缘计算、医学成像、边缘计算、人工智能、移动设备等等。

如今,像英特尔、Marvell 和 AMD 这样的主要半导体制造商已经涉足芯片组技术,我们可以预期更多公司将探索这一选项。随着芯片组 IP 市场的发展,类似于许多其他组件市场的发展方式,更多的无晶圆厂半导体公司可能会采取定制半导体方法,而不是使用离散组件构建系统。

现在英特尔、AMD 和 TSMC 已经就芯片组互连的通用标准达成一致,我们是否会看到其他公司更广泛地推广这些设计?人们可以希望这些组件的市场得到发展,因为这将鼓励在大型半导体制造商之外的封装层面上进行更多创新。

随着基于芯片组的具有先进封装的组件进入市场,系统设计师可以使用 Octopart 中的高级搜索和过滤功能找到他们需要的所有先进组件进行先进设计。当您使用 Octopart 的电子元件搜索引擎时,您将能够访问最新的分销商定价数据、零件库存和零件规格,而且所有这些都可以通过用户友好的界面免费访问。查看我们的集成电路页面以找到您需要的组件。

通过订阅我们的新闻通讯,随时了解我们的最新文章。

Back

Back