Design für Testbarkeit (DFT)

Die Gesamtkosten für die Herstellung einer fertigen Leiterplatte (PCB) lassen sich in mehrere grundlegende Kategorien unterteilen: Die Kosten für die Herstellung der blanken PCB, die Kosten für Komponenten, die Montagekosten und die Kosten für Tests. Dieser letzte Punkt, die Kosten für das Testen der fertigen Platine, kann bis zu 25% bis 30% der Gesamtkosten für die Produktion des Produkts ausmachen.

ZUSAMMENFASSUNG

Das Design für Testbarkeit in einem PCB-Design (DFT) ist ein kritischer Schritt im Prozess des Designs für die Fertigbarkeit (DFM). Dieses entscheidende Konzept läuft darauf hinaus, ein konsistentes Produkt zu den niedrigstmöglichen Herstellungskosten zu entwickeln, während eine akzeptable Fehlerquote beibehalten wird. Die Berücksichtigung der Testbarkeit während des PCB-Designs beinhaltet die Ausarbeitung des Erstellungsprozesses, um Testpunktanforderungen zu verstehen und Fehler schnell zu isolieren. Sowohl für Herstellungsfehler als auch für Komponentenausfälle ist DFT von größter Bedeutung beim Design für Rentabilität. In diesem Dokument werden wir DFT ausführlich untersuchen und uns speziell das In-Circuit-Testing (ICT) ansehen.

DFM- UND DFT-RICHTLINIEN

Bei der Auswahl eines Auftragsfertigers (CM) sollten diese immer Richtlinien für Design for Manufacturability (DFM) und Design for Testability (DFT) bereitstellen. Stellen Sie sicher, dass Sie diese Richtlinien für jeden in Betracht gezogenen CM erhalten und lesen. Die Überprüfung der DFM- und DFT-Richtlinien verschiedener CMs kann Einblicke in deren jeweiliges Expertiseniveau, Wissen und Fähigkeiten geben. Folglich sind diese Richtlinien ein nützliches Werkzeug bei der Entscheidung, welcher CM am besten geeignet ist, die Produkte Ihres Unternehmens herzustellen.

VORAUSPLANUNG

Die ersten Fragen, die man sich bei der Planung eines Designs für Testbarkeit stellen sollte, sind:

- Wer wird die Punkte der Montage testen?

- Was sind ihre Fähigkeiten?

Die ersten Fragen, die man sich bei der Planung eines Designs stellen sollte, sind 1.) wer wird die Montage testen und 2.) über welche Fähigkeiten verfügen sie? Die DFT-Richtlinie wird bei der anfänglichen Planung des Layouts hilfreich sein. Es ist jedoch eine gute Idee, direkt den CM zu kontaktieren und mit einem erfahrenen Testingenieur über Ihre spezifischen Bedürfnisse zu sprechen. Der Testingenieur wird in der Lage sein, über ihre Fähigkeiten zu diskutieren und Sie über die verschiedenen Testmethoden, die sie anbieten können, zu informieren. Eine Kombination aus Boundary-Scan (JTAG), automatisierten ICT-Testpunkten, Röntgenlaminographie (AXI) und visueller Inspektion (manuell und maschinelle Sichtprüfung) wird die umfassendste Testabdeckung bieten. Dies wird Ihnen auch Zugang zu sofortigem Feedback über den Fertigungsprozess geben, sodass der Arbeitsablauf bei Bedarf schnell angepasst werden kann und defekte Komponenten erkannt und aussortiert werden können.

Als Nächstes sollten Sie überlegen, welche Testpunktanforderungen notwendig sind, um ein qualitativ hochwertiges Endprodukt zu garantieren. Es kann sein, dass die Nutzung des vollen Arsenals an verfügbaren Testmöglichkeiten für Ihre Anwendung nicht erforderlich ist und tatsächlich kostenprohibitive sein könnte. Wenn Sie beispielsweise ein PCB-Layout für einen einmaligen Satelliten, der die Erde umkreist, erstellen, werden Sie jede verfügbare Testart durchführen wollen, um sicherzustellen, dass das fertige Produkt jahrelang zuverlässig in einer Umgebung funktioniert, in der eine Reparatur keine Option ist. Wenn Sie jedoch musikalische Grußkarten herstellen, könnte ein einfacher, funktionaler Test alles sein, was erforderlich ist.

ICT-TEST

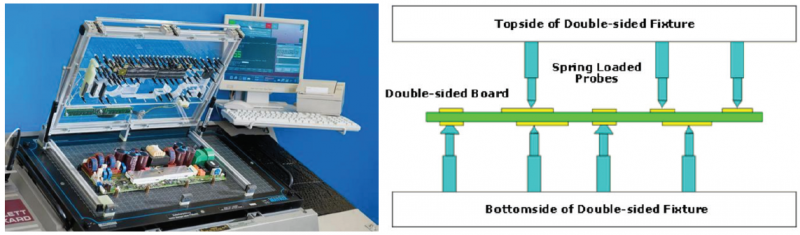

ICT-Tests können eine Reihe von Defekten auf gedruckten Schaltkarten, sowohl auf der Herstellungs- als auch auf der Komponentenebene, erkennen. Es gibt zwei Arten von ICT-Testsystemen. Ein System verwendet eine Testvorrichtung, die die zu testende gedruckte Schaltungsbaugruppe (PCA) umschließt und verschiedene Netze abtastet, um den Test durchzuführen. Das zweite ist ein Flying-Probe-Test, bei dem die Sonden von einem Computersystem gesteuert werden, um elektrischen Kontakt mit spezifischen Netzen der zu testenden PCA herzustellen.

Einige Beispieltests für PCB-Designs prüfen auf Kurzschlüsse/Unterbrechungen, fehlende Komponenten, falsch polarisierte oder sogar falsch bewertete Komponenten und eine Reihe anderer Aspekte. ICT-Tester können auch die PCA unter Test mit Strom versorgen und analoge sowie digitale Schaltkreise durchlaufen, um die ordnungsgemäße Funktion zu überprüfen. ICT-Testpunkt-Systeme können dieses Testregime mit einem hohen Durchsatz bewältigen.

PCB-DESIGNÜBERLEGUNGEN FÜR DIE PRÜFUNG VON GEDRUCKTEN LEITERPLATTEN MIT ICT

Altium Designer bietet optimierte PCB-Layoutfunktionen, sodass Sie sich auf detaillierte, aber kritische Aspekte der DFT konzentrieren können. Beispielsweise unterscheiden sich die Testbarkeitsanforderungen leicht bei Testpunkten für ICT-Tester, die Prüfköpfe verwenden, im Vergleich zum Flying-Probe-Test. Diese Details können Zeit und Geld kosten, wenn sie übersehen werden.

Für Testsyteme, die einen Prüfkopf verwenden, gibt es DFT-Richtlinien, die die Merkmale eines Testpunkts vorschreiben. Wenn Sie die Platzierung und das PCB-Layout planen, stellen Sie sicher, dass Sie eine Kopie dieser DFT-Richtlinie zur Hand haben, vom CM, der die abschließenden Montagetests durchführen wird.

Der ICT-Prüfadapter wird verschiedene Merkmale auf der Platine abtasten, um Messungen durchzuführen und Strom, Stimuli sowie Signale auf der zu testenden PCA zu liefern und zu messen. Testsysteme können beide Seiten der PCA abtasten. Das Beschränken der Testpunkte auf eine Seite der Platine wird jedoch die Komplexität des Prüfgeräts verringern, was zu niedrigeren Kosten und einer höheren Rendite für das Produkt führt.

ICT-Prüfadapter

Sobald ein Prüfpunkteadapter für eine PCA entwickelt wurde, werden alle zusätzlichen Modifikationen am Prüfadapter, um Änderungen am Produkt zu erleichtern, zusätzliche Kosten verursachen. Diese zusätzlichen Kosten können sich summieren. Daher muss sorgfältig darauf geachtet werden, bei jeglichen Modifikationen an der PCA keine der bestehenden Testpunkte zu versetzen.

Viele Merkmale einer PCA können als ICT-Testpunkt genutzt werden. Es gibt verschiedene Arten von federbelasteten Sonden (Pins), um eine ordnungsgemäße elektrische Verbindung zu einem Netz auf der PCA herzustellen.

ICT-Testsonden

Durchkontaktierte Pads, aus denen ein Anschluss herausragt, können oft abgetastet werden, wie zum Beispiel Steckerstifte, die auf die Sekundärseite (Unterseite) der Platine herausragen. Vias können oft als Testpunkte verwendet werden. Jedoch dürfen SMT-Pads mit angelöteten Bauteilen nicht als gültiger Testpunkt angesehen werden, wenn eine Testvorrichtung verwendet wird.

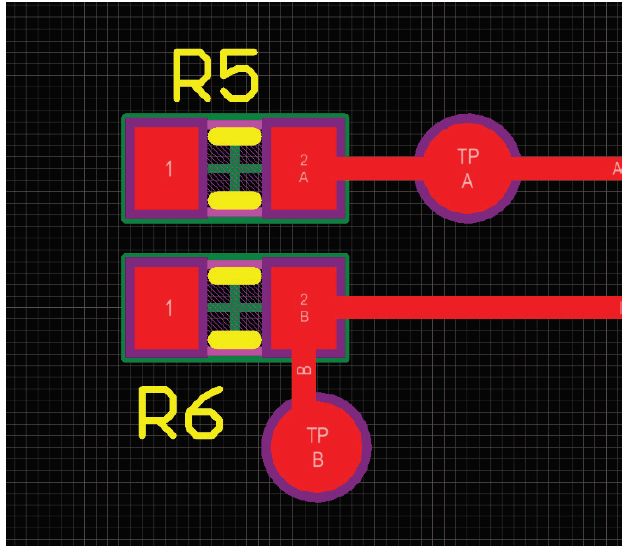

ICT-Testpunkte - TP

Wo SMT-Technologie angewendet wird, ist die Testbarkeit begrenzt, da keine verfügbaren Vias als Testpunkte genutzt werden können; daher müssen Testpunktpads in das Design integriert werden. Die Geometrie und der Freiraum des ICT-Testpads sollten zu den Punkten gehören, die in den DFT-Richtlinien abgedeckt sind, die vom CM, der die Tests durchführt, bereitgestellt werden.

Weitere relevante Informationen, die das DFT-Dokument bereitstellen wird, umfassen Abstände zwischen Testpunkten, Abstand zum Rand der Platine und was als Testpunkt verwendet werden kann.

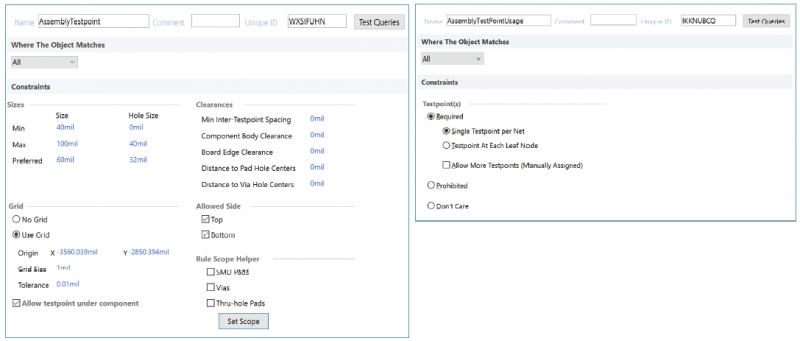

Das EDA-Tool, das für das Layout der Platine verwendet wird, wird einen Satz von Testbarkeits- und Designregeln haben, um zu definieren, was einen Testpunkt ausmacht, zusammen mit der erforderlichen Testabdeckung. Durch das korrekte Konfigurieren dieser Regelsätze (entsprechend den DFT-Richtlinien) in den Planungsphasen des Layouts wird die Erstellung der Testdokumentation ein automatisierter Prozess.

ICT-Testregeln für Eigenschaften eines Testpunkts und Testpunktabdeckung

Automatisierter Testpunkt-Manager

Generierung von Testpunktdateien

Nachdem die Testpunkt- und Entwurfsregeln konfiguriert wurden, verfügt das EDA-Tool über automatisierte Funktionen, um die Testpunkte im Design zuzuweisen. Allgemein gesprochen wird die erstellte Dokumentation eine Testpunktdatei oder einen Bericht umfassen, der die Koordinaten jedes Testpunkts enthält. Dieser Bericht kann in verschiedenen Dateiformaten generiert werden, einschließlich des IPC-D-356A-Formats. Andere Dateiformate können vom CM, der den Test durchführt oder die Vorrichtung erstellt, erforderlich sein. Konsultieren Sie Ihren Test-CM, um zu überprüfen, welche Daten erforderlich sind, um die Testvorrichtung herzustellen.

FLYING PROBE TEST

Der Flying Probe Tester benötigt keine Werkzeuge für eine Testvorrichtung und wird daher die kostengünstigste ICT-Testlösung sein. Zusätzlich können gelötete SMT-Komponentenanschlüsse auf der PCA auch geprüft werden. Wenn Sie den CM für die Durchführung von ICT-Tests evaluieren, kann es klug sein zu fragen, ob sie über Flying Probe ICT-Testfähigkeiten verfügen. Dies erfordert nur die Programmierung des Testsytems und keine Werkzeugkosten für die Herstellung der Testvorrichtung. Zusätzlich werden technische Änderungen (ECO) an der PCA keine Vermeidung von Änderungen an den Testpunkten erfordern, da Unterschiede zwischen der alten und neuen Baugruppe nur Programmieränderungen benötigen.

Flying Probe ICT-Testsystem [3

SCHLUSSFOLGERUNG

Da die Testphase einer fertiggestellten Leiterplatte bis zu 30% der Gesamtkosten ausmachen kann, ist das Design für Testbarkeit in der PCB-Entwicklung wichtiger denn je. Dies beginnt zunächst mit der Kenntnis der Fähigkeiten Ihres Herstellers und welcher Testumfang als notwendig erachtet wird, um ein qualitativ hochwertiges Endprodukt zu garantieren. Sobald Ihre Planungsphase festgelegt ist, ermöglicht Ihnen ein umfassender ICT-Test, eine Reihe von Defekten zu erkennen, bevor Ihre Platine vollständig hergestellt ist. Altium Designer wird Sie in jedem Schritt dieses Prozesses unterstützen und den Designprozess erleichtern, sodass Sie besser für die Testbarkeit planen können. Konzentrieren Sie sich auf das, was im Designprozess wichtig ist, und schauen Sie sich Altium Designer heute noch an.

ZITIERUNGEN

- ICT-Testvorrichtung. Digitales Bild. N.p., n.d. Web.

- ICT-Testsonden. Digitales Bild. Peak Test. N.p., n.d. Web.

- Flying Probe ICT-Testsystem. Digitales Bild. Acdi. N.p., 2. Juli 2011. Web.