Hardware-Entwicklung bei Speicherknappheit: Ein Praxisleitfaden für Entwicklungs- und Beschaffungsteams

Im ersten Teil dieser Serie, Wie KI den Speichermarkt aus dem Gleichgewicht brachte, haben wir uns angesehen, wie die Nachfrage aus KI-Rechenzentren Speicher zum Engpass gemacht hat und warum sich die Preise für DRAM und NAND voraussichtlich nicht so schnell normalisieren werden. Jetzt betrachten wir, wie man in diesem Umfeld operiert. Wenn Sie 2026 Hardware entwickeln oder beschaffen, müssen Sie weiterhin Entscheidungen treffen: welche Bauteile spezifiziert werden sollen, wie Sie Ihre Designs für mehr Flexibilität strukturieren und wie Sie Risiken in der Lieferkette managen.

Wir behandeln zunächst Speicherkomponenten der „nächsten Welle“, die sich bereits in der Pipeline befinden, und gehen dann auf einige bewährte DRAM- und Flash-Komponenten ein. Anschließend stellen wir praxisnahe Vorgehensweisen sowohl für Engineering als auch für den Einkauf vor.

Für einen breiten Überblick über Speicherkomponenten sind die Kategorieseiten von Octopart für Speicher-ICs und Flash-Speicher gute Ausgangspunkte, um herstellerübergreifend nach Herstellern, Gehäusen und Verfügbarkeit zu suchen.

Zentrale Erkenntnisse

- Wissen, was kommt, und was verfügbar ist. Komponenten der nächsten Welle wie LPDDR6 und HBM4 zeigen, wohin sich Plattformen entwickeln, aber Ihre Designs für 2026 werden mit DDR5, LPDDR5X und ausgereiftem NAND ausgeliefert, das heute auf Lager ist.

- Für Austauschbarkeit und Flexibilität entwickeln. Standardisieren Sie auf Mainstream-Schnittstellen, qualifizieren Sie Bauteilfamilien und unterstützen Sie mehrere Speicherdichten in der Firmware. Verwenden Sie nach Möglichkeit Sockel und Module und planen Sie heruntergestufte Speicheroptionen ein, die die UX-Ziele dennoch erfüllen.

- Behandeln Sie Lieferrisiken wie ein Engineering-Problem. Erstellen Sie AVLs mit mehreren Bezugsquellen, sichern Sie Zuteilungen für kritische Produktlinien und verfolgen Sie den Lebenszyklus sowie Alternativen mit Tools wie Octopart.

Komponenten der nächsten Welle, die die Richtung vorgeben

Samsungs mobiles LPDDR6-DRAM

Samsungs LPDDR6 wurde für On-Device-KI, Automotive sowie mobile und PC-Plattformen der nächsten Generation entwickelt und bietet gegenüber LPDDR5X deutliche Effizienzgewinne, eine erweiterte I/O-Architektur und eine anfängliche Geschwindigkeit von bis zu 10,7 Gbit/s; der LPDDR6-Standard ist darauf ausgelegt, mit zunehmender Reife des Ökosystems weiter zu skalieren. LPDDR6 wird man noch nicht in den Regalen der Distributoren finden, aber wenn Sie rund um führende SoCs oder Flaggschiff-Geräte entwickeln, sollten Sie damit rechnen, darauf zu stoßen.

HBM4

Am oberen Ende der Leistungsskala versprechen die 16-lagigen HBM4-Bausteine mit 48 GB von SK Hynix mehr als 2 TB/s Bandbreite; die Massenproduktion ist für etwa Q3 2026 vorgesehen. Samsung verfolgt einen anderen Ansatz und nutzt 4-nm-Logik sowie 1c-DRAM, um die thermische Performance zu verbessern. Ingenieure, die an KI-Hardware arbeiten, werden diese Bauteile in der Regel nicht über Katalogdistributoren beziehen, aber HBM4 ist für alle relevant, weil es einen großen Anteil der fortschrittlichen DRAM-Kapazität bindet – ein Grund dafür, warum konventionelles DRAM weiterhin knapp bleibt.

Samsung V-NAND der 10. Generation

Mit über 400 Layern und einer 5,6-GT/s-Schnittstelle zielt Samsungs V-NAND der 10. Generation auf PCIe-5.0- und künftige PCIe-6.0-SSDs für Rechenzentren und KI-Workloads. Es ist zu erwarten, dass hochdichtes TLC auf Basis dieses Siliziums in den kommenden Jahren viele Enterprise- und High-End-Client-Laufwerke tragen wird.

Kioxia/Sandisk BiCS10 NAND

Dieses 332-Layer-BiCS10 mit Toggle-DDR-6.0-Schnittstelle liefert 4,8 Gbit/s pro Pin und zielt auf KI- und Hyperscale-Speicher ab. Laut EE Times hat Kioxia erklärt, dass die gesamte NAND-Produktion für 2026 bereits in KI-bezogene Anwendungen verkauft ist, und das Hochfahren von BiCS10 von H2 2027 auf 2026 vorgezogen wurde, um die Nachfrage zu bedienen.

Weniger eingeschränkte Speicherprodukte als bewährte Arbeitspferde

Diese Bauteile waren Anfang März 2026 bei großen Distributoren bestellbar. Die Verfügbarkeit ändert sich schnell, daher sollten Sie Lagerbestand und Lebenszyklusstatus auf Octopart prüfen, bevor Sie eine BOM festschreiben.

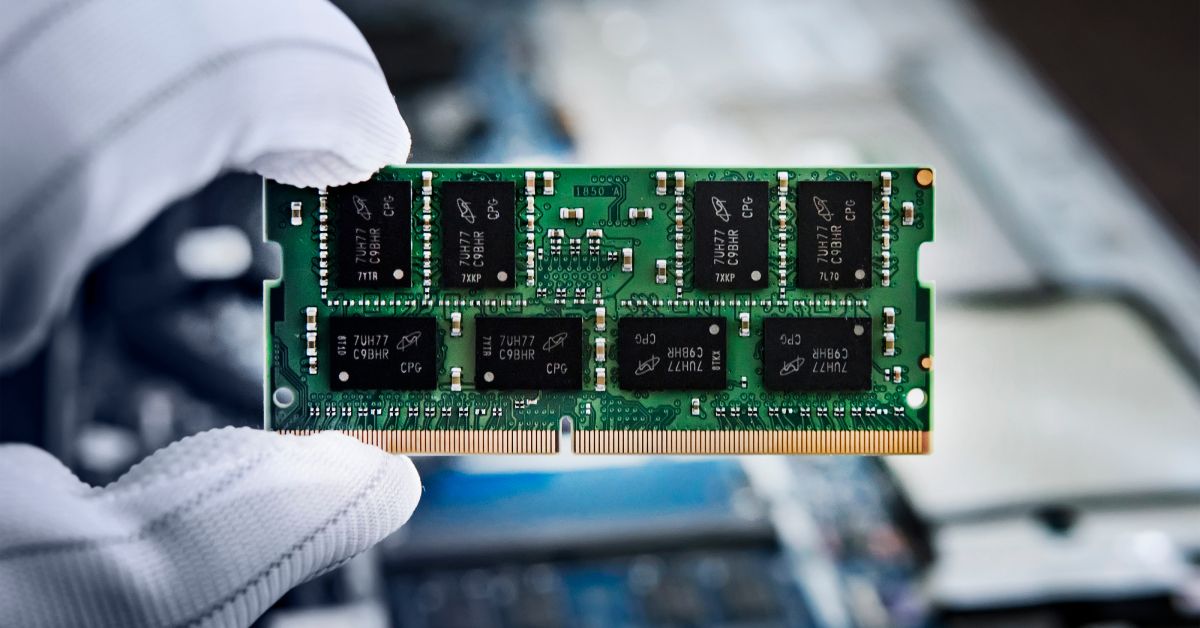

- Apacer D22.31491S.001, 8 GB DDR5-4800 SO-DIMM. Eine praktische DRAM-Option für „Late Binding“-Designs, die ein gesockeltes Modul verwenden können und dem Einkauf bei Substitutionen mehr Spielraum geben.

- MT60B2G8RZ-56B IT:D, 16-Gbit-DDR5-SDRAM (2G x 8), 78-Ball-VFBGA. Ein Mainstream-DRAM-IC der Klasse x8 DDR5-5600, der sich für kundenspezifische Speicherdesigns auf Leiterplattenebene eignet und mehr praktische Flexibilität bei Second Sources bietet als eine einmalige Modul-SKU.

- Macronix MX30LF4G28AD-XKI-TR, 4-Gbit-SLC-NAND (VFBGA-63). Gut geeignet für industrielle und Embedded-NAND-Designs, die Ausdauer und vorhersehbares Verhalten in einem kompakten BGA-Footprint benötigen.

- Macronix MX60LF8G28AD-TI-T, 8-Gbit-SLC-NAND (TSOP-48). Eine praktische Wahl, wenn Sie einen breit unterstützten parallelen NAND-Footprint für ausgereifte Controller-Ökosysteme und einfachere Leiterplatten-Nacharbeit als bei Fine-Pitch-BGAs benötigen.

- Macronix MX52LM04A11XSI, 4 GB eMMC 5.1 (BGA-153). Eine unkomplizierte Managed-NAND-Option, wenn Sie weniger Controller-Abhängigkeiten und eine sauberere Substitution als bei Raw-NAND plus kundenspezifischem Flash-Stack wünschen.

- Macronix MX52LM08A11XVW, 8 GB eMMC 5.1 (BGA-153). Ein praktischer Kapazitätspunkt für viele Embedded-Linux- und HMI-Systeme, mit denselben Schnittstellen- und Integrationsvorteilen wie kleinere eMMC-Bauteile.

- Micron MT40A2G8SA-062E:F, 16-Gbit-DDR4-DRAM (2G x 8). Nach wie vor ein volumenstarkes Arbeitspferd für viele Plattformen und eine pragmatische „Jetzt ausliefern“-Option, wenn DDR5 nicht erforderlich ist.

Design-Playbook: Wie Ingenieure Flexibilität einbauen

Vor diesem Hintergrund gibt es weiterhin viele Maßnahmen, mit denen Hardwareingenieure Designs robuster machen können.

- Auf Mainstream-Schnittstellen und -Familien standardisieren. DDR5, LPDDR5X, e.MMC, UFS und SPI-/QSPI-Flash verfügen über tiefe Ökosysteme und viele Second Sources. Wenn Sie bei gängigen Spannungen und Gehäusen bleiben, maximieren Sie den Pool kompatibler Bauteile.

- Flexibilität in Firmware und Speicherabbild integrieren. Vermeiden Sie es, eine einzelne DRAM-Dichte oder SPI-Flash-Größe fest zu codieren. Unterstützen Sie mehrere Geometrien in Ihrem Initialisierungscode, damit Alternativen ausgetauscht werden können.

- Bevorzugen Sie gemanagten nichtflüchtigen Speicher, wenn er passt. e.MMC und UFS verbergen Details des NAND-Managements hinter stabilen Schnittstellen und bieten oft klarere Substitutionspfade als Raw-NAND, das an einen bestimmten Controller gebunden ist.

- Planen Sie Varianten mit heruntergestufter Bin-Klasse ein. Entwerfen Sie Ihre Software so, dass Konfigurationen mit weniger Speicher weiterhin eine akzeptable User Experience liefern, etwa durch geringere Standard-Parallelität, kleinere Asset-Sets oder abgestufte Funktionsumfänge.

- Verwenden Sie nach Möglichkeit modulare Speicher- und Storage-Lösungen. Sockel für SO-DIMMs, UDIMMs und M.2-SSDs ermöglichen ein spätes Festlegen der Konfiguration und geben dem Einkauf mehr Hebelwirkung. Reservieren Sie verlöteten Speicher für eingeschränkte Formfaktoren, in denen er wirklich erforderlich ist.

Sourcing-Playbook: Wie der Einkauf Risiken managen kann

Die Situation erfordert Ihre Aufmerksamkeit. Ende Februar 2026 warnte Lenovo seine Channel-Partner, Bestellungen noch vor Monatsende aufzugeben, um Preiserhöhungen im März zuvorzukommen, während TrendForce prognostizierte, dass gemischte PC-DRAM-Preise (DDR4/DDR5) allein in Q1 gegenüber dem Vorquartal um 105–110 % steigen würden. Das folgende Playbook spiegelt diese neue Realität wider.

- Sichern Sie Zuteilungen und langfristige Vereinbarungen für kritische DRAM- und NAND-Linien, insbesondere für Server, KI-Systeme und High-End-Notebooks. Marktinformationen von Unternehmen wie TrendForce können helfen zu bestimmen, wann man sich festlegen sollte.

- Erstellen Sie freigegebene Lieferantenlisten rund um Familien, nicht um einzelne SKUs. Definieren Sie akzeptable Klassen von Modulen, NAND und e.MMC und arbeiten Sie mit dem Engineering zusammen, um mehrere Optionen im Voraus zu validieren.

- Segmentieren Sie Produkte nach ihrer Speichersensitivität. Lenken Sie knappen, teuren Speicher auf SKUs, bei denen er Leistung und Marge am stärksten beeinflusst; wenden Sie bei weniger speichersensitiven Geräten strengere Kostenkontrollen an.

- Nutzen Sie Speicherbestände als strategische Absicherung für Produkte mit langem Lebenszyklus. Ein Pufferbestand wichtiger DRAM- oder NAND-Bauteile kann günstiger sein, als mitten im Produktlebenszyklus Leiterplatten neu zu entwickeln oder Firmware umzuschreiben, wenn ein Bauteil knapp wird.

Flexibilität ist die Strategie

Im ersten Teil dieser Serie haben wir das Warum hinter der Speicherknappheit behandelt. Hier haben wir das „Was jetzt?“ betrachtet. Die Antwort ist dieselbe, egal ob Sie Ingenieur sind oder im Einkauf arbeiten: Flexibilität ist die beste Absicherung. Entwickeln Sie für Austauschbarkeit, qualifizieren Sie breit und nutzen Sie Tools wie Octopart, um Ihre Optionen sichtbar und aktuell zu halten. Die Teams, die am besten durch diesen Zyklus kommen, sind diejenigen, die frühzeitig Optionalität in ihre Designs und Lieferketten eingebaut haben und sich weiter anpassen, wenn sich Versorgungslage und Preise verändern.

Häufig gestellte Fragen

Warum sind DRAM und NAND 2026 immer noch schwer zu beschaffen?

Die aktuelle Knappheit wird durch die Wafer-Zuteilung verursacht, nicht durch technologische Grenzen. Speicherhersteller priorisieren die margenstarke KI-Nachfrage, insbesondere HBM und Rechenzentrums-DRAM, im Rahmen mehrjähriger Verträge. Da HBM pro Bit deutlich mehr Wafer-Kapazität verbraucht als konventionelles DRAM, bleibt weniger Kapazität für DDR5, LPDDR und NAND übrig, was die Verfügbarkeit knapp hält.

Sollten Ingenieure heute bereits mit Speicher der nächsten Generation wie LPDDR6 oder HBM4 entwickeln?

LPDDR6 und HBM4 zeigen, wohin sich Plattformen entwickeln, aber die meisten Produkte im Jahr 2026 werden mit DDR5, LPDDR5X und ausgereiftem NAND ausgeliefert, das jetzt verfügbar ist. Ingenieure sollten mit Blick auf Vorwärtskompatibilität entwickeln und gleichzeitig Bauteile auswählen, die sich während der Produktion zuverlässig beschaffen lassen, anstatt auf Teile zu setzen, die noch nicht im Vertrieb verfügbar sind.

Wie können Hardwaredesigns widerstandsfähiger gegenüber Speicherengpässen gemacht werden?

Widerstandsfähige Designs setzen auf Flexibilität und Austauschbarkeit. Dazu gehören die Standardisierung auf Mainstream-Schnittstellen, die Qualifizierung mehrerer Dichten und Anbieter, das Vermeiden fest codierter Speicherannahmen in der Firmware sowie der Einsatz von Sockeln oder Modulen, wo immer möglich. Die Unterstützung heruntergestufter Speicheroptionen stellt sicher, dass Produkte auch dann noch ausgeliefert werden können, wenn Bauteile mit höherer Kapazität knapp sind.

Was ist der beste Weg für Einkaufsteams, das Risiko in der Speicherlieferkette zu managen?

Der Einkauf sollte Speicher als strategische Ressource und nicht als Commodity behandeln. Zu den Best Practices gehören, langfristige Zuteilungen für kritische SKUs zu sichern, AVLs um Produktfamilien statt um einzelne Bauteile herum aufzubauen, den Lebenszyklus und Alternativen mit Tools wie Octopart zu überwachen und für Produkte mit langem Lebenszyklus gezielt Lagerbestände vorzuhalten, um erzwungene Redesigns zu vermeiden.