Wie KI den Speichermarkt aus dem Gleichgewicht brachte: Einblick in die DRAM- und NAND-Knappheit 2024–2026

Kernaussagen

- KI-Rechenzentren sind zum wichtigsten Kunden für Speicher-Silizium geworden und treiben gleichzeitig Veränderungen bei der Wafer-Zuteilung über DRAM, HBM und NAND hinweg voran.

- Dieser Angebots-Nachfrage-Zyklus ist anders. Begrenzte Fab-Erweiterungen, eine weitgehend ausverkaufte NAND-Produktion und mehrjährige HBM-Verträge bedeuten, dass der Engpass wahrscheinlich bis Ende 2027–2028 anhalten wird.

- Legacy- und Embedded-Designs sind Kollateralschäden. DDR3, frühes DDR4 und SLC-NAND sind einem steigenden EOL-Risiko, längeren Lieferzeiten und unvorhersehbaren Preisen ausgesetzt, da Anbieter margenstarken KI-Speicher priorisieren.

Die überraschende Wendung beim Speicher: Vom Hintergrundbauteil zum Engpass

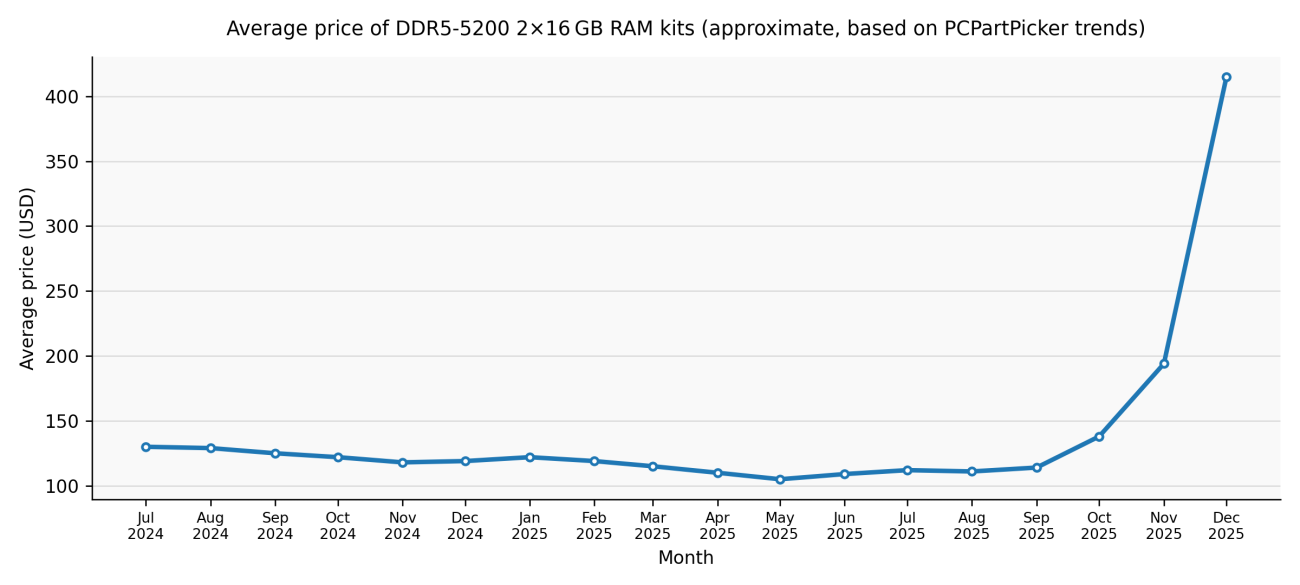

Während des größten Teils der PC-Ära spielte Speicher eher eine Nebenrolle. Zwischen 2024 und 2026 hat sich diese Dynamik umgekehrt. Speicher wurde zum limitierenden Faktor im Systemdesign, und die Kosten dafür, „einfach mehr RAM hinzuzufügen“, stiegen innerhalb weniger Quartale stark an.

Die Preise sind gestiegen, die Verfügbarkeit hat sich verschlechtert, und Produkte werden zunehmend mit dem absoluten Minimum an Speicher ausgeliefert statt mit dem komfortablen Puffer, an den wir uns gewöhnt haben. Es findet eine strukturelle Neuverteilung statt, wer die Wafer bekommt und warum.

Was hat sich also tatsächlich verändert, und warum fühlt sich dieser Engpass anders an als die vorherigen? Das erläutern wir hier im ersten Teil einer zweiteiligen Serie über die Kräfte, die die Speicherlieferkette vom Cloud-Server bis hinunter zu Embedded-Systemen stören. Teil zwei, Hardwareentwicklung bei Speichermangel, baut darauf auf und bietet einen tiefen Einblick in Speicherkomponenten der nächsten Generation, die gerade anlaufen, führende Standardprodukte, die Sie heute bei Ihrem Distributor bestellen können, Designmuster und Beschaffungsstrategien.

Wie KI-Rechenzentren die Nachfragelandschaft neu verdrahten

In früheren Zyklen war die Speichernachfrage breit über PCs, Smartphones, Server und Unterhaltungselektronik verteilt. Angebot und Nachfrage gerieten aus dem Takt, Preise stiegen oder fielen, und dann normalisierte sich die Lage wieder, sobald die Fabs nachjustierten. Der Engpass von 2024–2026 folgt diesem Muster nicht.

Der Unterschied liegt darin, wer kauft. KI-zentrierte Rechenzentren dominieren inzwischen das Nachfragebild, und ihre Trainingscluster und Inferenzfarmen benötigen enorme Mengen an High-Bandwidth Memory (HBM) und konventionellem DRAM pro GPU oder Beschleuniger. HBM verbraucht pro Bit deutlich mehr Wafer-Kapazität als Standard-DRAM und ist daher für Hersteller äußerst attraktiv, die mehrjährige, margenstarke Verträge mit Anbietern von KI-Infrastruktur abschließen wollen.

Einige Analysten schätzen inzwischen, dass Rechenzentren bis zu 70 % aller High-End-Speicherchips verbrauchen werden, die 2026 produziert werden – eine deutliche Umkehr gegenüber der Zeit, als Consumer-Geräte den Großteil solcher Chips ausmachten. In diesem Umfeld werden PC- und Mobile-Speicher zum Nebengeschäft, während KI-Rechenzentren zum Hauptthema werden.

Die HBM4-Generation, vorgestellt auf der CES 2026, veranschaulicht das Ausmaß dieses Wandels. SK Hynix zeigte ein 16-lagiges 48-GB-Bauelement, das mehr als 2 TB/s liefert und damit die Leistung des frühen HBM3, das in den ersten Gen-AI-Beschleunigern eingesetzt wurde, deutlich steigert. Jeder Wafer, der in diese Stapel fließt, produziert kein DDR5 für Ihren nächsten PC und kein LPDDR5X für ein Smartphone.

Embedded- und Legacy-Designs: Seitlich unter Druck

Embedded- und Industrie-Designs, die häufig auf ältere DRAM-Standards oder ausgereiftes SLC-NAND angewiesen sind, stehen vor eigenen Herausforderungen. Viele dieser Produkte verwenden DDR3- oder frühe DDR4-Bausteine sowie parallelen NAND-Flash, die nicht mehr im Zentrum der Roadmaps der Anbieter stehen.

Da Hersteller margenstarkes HBM und servertaugliches DRAM priorisieren, reduzieren oder streichen sie Legacy-Linien. Was übrig bleibt, ist trotz ausgereifter Technologie mit unerwartet hohen Preisen und längeren Lieferzeiten verbunden.

Den Lebenszyklusstatus von Bauteilen mit Tools wie Octopart genau im Blick zu behalten, hilft Teams dabei, EOL-Ankündigungen und eine sich verschärfende Versorgungslage zu erkennen, bevor daraus Notfälle werden.

Fortschritt unter Druck: DDR5, LPDDR6, NAND und HBM4

Dieselben Technologiewechsel, die älteren Designs die Versorgung entziehen, bringen echte technische Durchbrüche hervor. Beide Seiten dieser Dynamik zu verstehen, ist relevant, weil Fortschritte verändern, womit entwickelt werden kann, während die dahinterstehenden Wafer-Ökonomien erklären, warum Commodity-Speicher auf absehbare Zeit nicht günstiger wird.

DRAM

Samsung fertigt das dünnste LPDDR5X-DRAM der 12-nm-Klasse in Massenproduktion für Mobilgeräte der nächsten Generation und kombiniert hohe Leistung mit Energieeffizienz und einer dünnen Gehäusebauform, die sich für Premium-Smartphones und ultraportable Geräte eignet. Erste LPDDR6-Bauteile steigern Bandbreite und Energieeffizienz noch weiter und zielen auf On-Device-KI- und Automotive-Anwendungen. Samsungs LPDDR6-Implementierung erhält zunehmend Anerkennung auf Branchenveranstaltungen und signalisiert, wohin sich High-End-Mobile-Speicher entwickelt.

HBM

Am HBM-Ende des Spektrums zeigt die CES-2026-Berichterstattung zu HBM4, dass Speicherstapel zu hochintegrierten Subsystemen werden. Die 16-High-Stacks von SK Hynix nutzen MR-MUF und ultradünne DRAM-Wafer, um innerhalb der JEDEC-Höhenlimits zu bleiben, während Samsung auf seine 4-nm-Logik blickt (deren Massenproduktion im Februar 2026 begann), um Thermik und Energieeffizienz zu verbessern. Dieser gesamte Entwicklungsaufwand und diese gesamte Wafer-Kapazität sind klar auf KI-Beschleuniger ausgerichtet.

NAND

Im NAND-Bereich stapeln Anbieter immer mehr Schichten. V-NAND der 10. Generation mit über 400 Schichten und Schnittstellen um 5,6 GT/s wird in PCIe-5.0- und künftige PCIe-6.0-SSDs für Rechenzentrums- und KI-Anwendungsfälle integriert. Das NAND BiCS der 10. Generation mit 332 Schichten von Kioxia und Sandisk, das die Toggle-DDR-6.0-Schnittstelle mit bis zu 4,8 Gb/s pro Pin nutzt, zeigt, wie weit sich NAND mit hoher Bandbreite für SSDs der Rechenzentrums- und Enterprise-Klasse entwickelt hat.

Die Technologie entwickelt sich weiter, aber die Kapazität hält nicht Schritt. Laut EE Times haben Samsung und SK Hynix ihre NAND-Wafer-Produktion 2024–2025 reduziert, während sie HBM und DRAM priorisierten, und trotz eines Marktanteils von mehr als der Hälfte des Marktes keine neue NAND-Kapazität angekündigt. Daten von Omdia zeigen, dass Samsungs NAND-Wafer von 4,9 Millionen (2024) auf 4,68 Millionen (2025) zurückgehen und die von SK Hynix von 1,9 Millionen auf 1,7 Millionen.

Gleichzeitig ist NAND für KI-Inferenz kritisch geworden. Da sich KI von Training zu Bereitstellung verlagert, werden SSDs auf Basis von NAND mit hoher Layer-Zahl zunehmend zum Hauptspeicher für Modellgewichte und Arbeitsdaten. Das Management von Kioxia hat erklärt, dass die gesamte NAND-Produktion für 2026 bereits ausverkauft ist, dass BiCS10 von der zweiten Jahreshälfte 2027 auf 2026 vorgezogen wird und dass künftig fast die Hälfte der NAND-Nachfrage aus KI-Anwendungen kommen könnte. NAND-Spezialisten wie Kioxia und das nun unabhängige Unternehmen Sandisk, die einst als Außenseiter in einem commoditisierten Markt galten, sind plötzlich als Gewinner des KI-SSD-Booms positioniert.

Warum die übliche Erholung ausbleibt

Branchenanalysten verweisen auf ein im historischen Vergleich relativ moderates Wachstum des DRAM- und NAND-Angebots bis 2026. Gleichzeitig lässt die Nachfrage nicht nach. Neue Modellarchitekturen, Inferenz-Workloads und Edge-AI-Deployments treiben den Speicherbedarf weiter nach oben, statt ihn auf einem Plateau einpendeln zu lassen. HBM4-Anbieter reservieren erhebliche Wafer-Kapazitäten für die Anforderungen von Nvidia- und anderen Beschleunigern, und wie wir im vorherigen Abschnitt erwähnt haben, sind NAND-Anbieter wie Kioxia für 2026 ausverkauft.

Im Dezember 2025 demonstrierte Micron die strukturelle Natur dieses Wandels, indem das Unternehmen seinen Ausstieg aus dem Consumer-Geschäft von Crucial ankündigte, um „größere, strategische Kunden“ besser bedienen zu können. Einige Anbieter, darunter Micron, haben öffentlich erklärt, dass sie nicht erwarten, dass sich der RAM-Mangel für Verbraucher vor etwa 2028 wesentlich entspannt, wenn neue Kapazitäten und Prozessumstellungen vollständig hochgefahren sein sollen. Dieselbe Logik gilt zunehmend auch für NAND: KI-Inferenz bindet künftige SSD-Kapazitäten so schnell, wie Anbieter sie überhaupt bereitstellen können.

Im Dezember 2025 charakterisierte IDC den Engpass als „nicht nur einen zyklischen Mangel, sondern eine potenziell dauerhafte, strategische Neuverteilung der weltweiten Silizium-Wafer-Kapazität“. Im Februar 2026 korrigierte TrendForce seine Prognose für die Vertragspreise von konventionellem DRAM im ersten Quartal 2026 deutlich nach oben – von einer früheren Schätzung von 55–60 % auf 90–95 % gegenüber dem Vorquartal. Darin enthalten war für PC-DRAM (gemischtes DDR4/DDR5) ein prognostizierter Anstieg von 105–110 % QoQ, ein neuer Quartalsrekord.

Wie es weitergeht: Vom Verständnis zum Handeln

In Hardwareentwicklung bei Speichermangel betrachten wir sieben Speicherkomponenten der nächsten Welle, die in OEM- und Rechenzentrumsdesigns hochgefahren werden, acht bewährte DRAM- und Flash-Produkte, die bei großen Distributoren sofort verfügbar sind, sowie konkrete Vorgehensweisen für die Arbeit unter diesen Rahmenbedingungen.

Häufig gestellte Fragen

Warum gibt es einen Speichermangel, obwohl sich DRAM- und NAND-Technologien ständig verbessern?

Der aktuelle Mangel wird nicht durch technologische Grenzen verursacht, sondern durch die Ökonomie der Wafer-Zuteilung. Ein wachsender Anteil der weltweiten Wafer-Kapazität für Speicher wird auf margenstarken KI-Speicher umgelenkt, insbesondere auf HBM für Rechenzentrums-Beschleuniger. Da HBM pro nutzbarem Bit deutlich mehr Wafer-Fläche verbraucht als konventionelles DRAM, reduziert jeder Wafer, der für die HBM-Produktion reserviert wird, die Ausbringung von DDR4, DDR5, LPDDR und NAND. Bei begrenztem Ausbau neuer Fabs und langfristigen KI-Lieferverträgen, die Kapazitäten binden, führen Verbesserungen bei der Speicherdichte nicht zu einer höheren Verfügbarkeit für Mainstream- oder Embedded-Märkte.

Warum fühlt sich dieser Speichermangel anders an als frühere Zyklen?

Anders als frühere Boom-Bust-Zyklen wird dieser Mangel durch eine strukturelle Konzentration der Nachfrage geprägt und nicht durch vorübergehenden Überkonsum. KI-Training und KI-Inferenz treiben den Speicherbedarf weiter nach oben, während Anbieter das Kapazitätswachstum bewusst begrenzt haben. Mehrjährige HBM-Verträge, eine für 2026 ausverkaufte NAND-Produktion und explizite Aussagen von Anbietern, die erst nach 2027–2028 Entlastung in Aussicht stellen, bedeuten, dass es sich um eine langfristige Neuverteilung handelt und nicht um ein kurzfristiges Ungleichgewicht, das sich allein über Preise selbst korrigiert.

Welche Risiken entstehen dadurch für Embedded- und Legacy-Designs mit DDR3, frühem DDR4 oder SLC-NAND?

Legacy-Speicherprodukte werden von großen Lieferanten zunehmend als nicht strategisch eingestuft. Da Anbieter fortschrittliche DRAM- und HBM-Produkte priorisieren, sehen sich ältere Prozessknoten mit schrumpfenden Produktionsläufen, steigenden Mindestbestellmengen, längeren Lieferzeiten und einem höheren EOL-Risiko konfrontiert. Selbst wenn Bauteile technisch gesehen weiterhin „in Produktion“ sind, werden die Preise volatiler und die Verfügbarkeit unvorhersehbarer. Für Embedded-Teams steigt damit die Bedeutung von Lifecycle-Monitoring, Multi-Sourcing und Redesign-Planung deutlich früher im Produktlebenszyklus als in früheren Generationen.

Wann sollten Ingenieure damit rechnen, dass sich Speicherpreise und Verfügbarkeit normalisieren?

Auf Grundlage von Aussagen der Lieferanten und Prognosen von Analysten ist vor Ende 2027 oder 2028 kaum mit einer spürbaren Entlastung zu rechnen. Neue Kapazitäten, Prozessumstellungen und erweiterte Packaging-Linien für HBM und fortschrittlichen NAND sind geplant, benötigen jedoch mehrere Jahre, bis sie verfügbar sind. Gleichzeitig treiben KI-Inferenz-Workloads die Nachfrage sowohl nach DRAM als auch nach NAND der SSD-Klasse weiter an und binden damit einen großen Teil dieser künftigen Kapazitäten. Ingenieure sollten ihre Designs unter der Annahme planen, dass Speicher für den Rest dieses Jahrzehnts ein begrenzter und kostenkritischer Systemfaktor bleiben wird.