Pi.MX8 Projekt - Layout des Boards Teil 3

Kapitel

Board Layout Part 3

| Created: June 24, 2024PCB Assembly

| Coming soonWillkommen zu einer neuen Folge des Pi.MX8 Open-Source-Computermodul-Projekts! In dieser Serie beschäftigen wir uns mit dem Design und dem Testen eines System-on-Module, das auf einem i.MX8M Plus Prozessor von NXP basiert.

In der letzten Aktualisierung haben wir die Vorbereitungen für das Layout abgeschlossen. Dies umfasste das Erstellen der Impedanzprofile, das Hinzufügen der Designregeln gemäß den Spezifikationen des Platinenherstellers und das Definieren von Bereichen, in denen spezielle Designregeln gelten sollen. Wir haben auch das Routing der LPDDR4-Schnittstelle abgeschlossen, allerdings noch ohne Längenabstimmung (vorerst).

Bevor wir mit der Längenabstimmung der DRAM-Schnittstelle beginnen, werden wir uns das Routing der verbleibenden Schnittstellen auf dem Pi.MX8-Modul ansehen. Es gibt einige Hoch- und Niedriggeschwindigkeitsbusse auf der Platine, von denen einige breite parallele Busse sind, die viel Routingplatz beanspruchen. Um jedem Interface genügend Platz zuweisen zu können, werden wir zunächst einen groben Grundriss für jede Routingebene auf dem Modul erstellen.

Routingplanung

Der Routingplan wird uns helfen zu bestimmen, wie wir alle Hoch- und Niedriggeschwindigkeitsschnittstellen über die verfügbaren Signallagen verteilen. Indem wir im Voraus einen groben Leitfaden erstellen, können wir sicherstellen, dass wir genügend Routing-Fläche auf der Schicht zur Verfügung haben, an der wir gerade arbeiten. Dies hilft uns auch, Schichtübergänge zu minimieren und die Menge an Nacharbeit während des Routingprozesses zu reduzieren.

Es gibt mehrere Möglichkeiten, die Layoutplanung einzurichten, die hauptsächlich von den verfügbaren Werkzeugen abhängen. Wir benötigen lediglich ein einfaches Zeichenwerkzeug, das es uns erlaubt, über ein vorhandenes Bild zu skizzieren. In diesem Beispiel werden wir Inkscape verwenden.

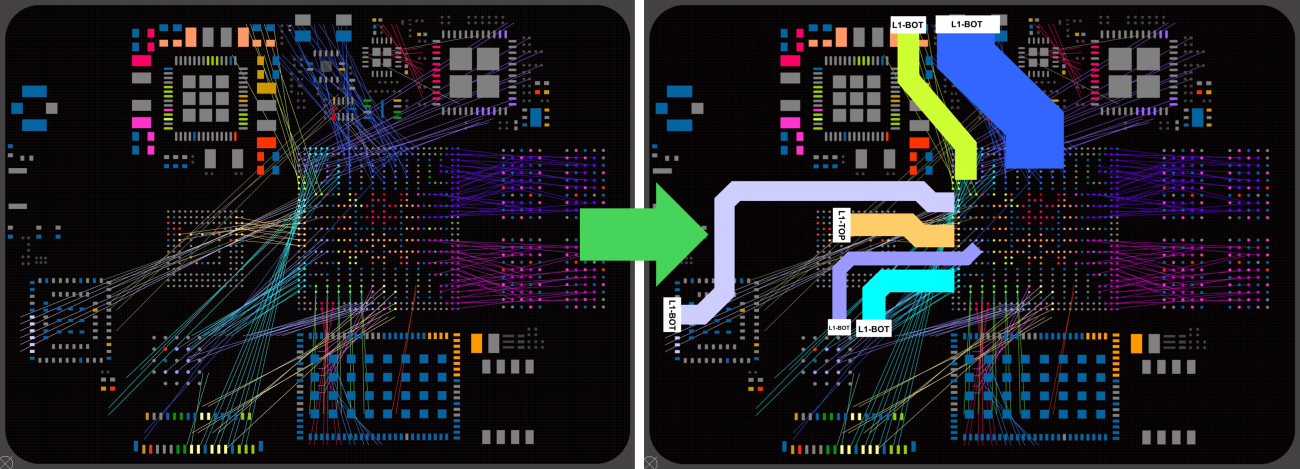

In Inkscape können wir ein Hintergrundbild hinzufügen, das die Komponentenplatzierung und die ungerouteten Schnittstellen in Form von farbigen Luftdrähten zeigt. Beachten Sie, dass die Stromnetze in diesem Screenshot ausgeblendet sind, da wir uns nur auf die Netze konzentrieren werden, die auf den Signallagen geroutet werden. Im Schaltplan haben wir auf jedem Stromnetz eine Netzklassendirektive platziert, was es einfach macht zu identifizieren, welche Netze auf den Ebenen geroutet werden, indem einfach die zugehörige Netzklasse im Layout-Editor ein- oder ausgeblendet wird.

Für das eigentliche Routing fügen wir einfach Linien in Inkscape hinzu, um die Schnittstellen darzustellen, die wir auf der entsprechenden Ebene routen möchten. Wir können die Breite dieser Linien anpassen, um darzustellen, wie viele Signale in der Schnittstelle geroutet werden. Die Farbe der Linie kann aus dem Hintergrundbild ausgewählt werden, um leichter zu identifizieren, welche Schnittstelle dargestellt wird.

Da auch für die Ebenenübergänge Platz auf allen Ebenen zugewiesen werden muss, können wir am Ende jeder Linie einen Block hinzufügen, der den Ebenenübergang detailliert.

Layoutplanung in Inkscape mit einem Altium Designer Screenshot als Hintergrundbild

Sobald wir den oben beschriebenen Prozess für jede Routingebene wiederholt haben, können wir mit dem eigentlichen Routingprozess beginnen.

Routing der obersten Ebene

Mit einer Routing-Strategie an Ort und Stelle, beginnen wir damit, die Schnittstellen auf der obersten Schicht zu verlegen. Da wir das Fanout-Routing für die Komponenten auf der obersten Schicht bereits erledigt haben, können wir den gesamten verbleibenden Platz für das Signalrouting verwenden. Es ist nicht viel Platz übrig, aber was wir haben, kann immer noch genutzt werden, um das Routing auf den inneren Signallagen durch strategisches Platzieren von VIAs in Regionen, die das Routing auf den inneren Lagen später nicht stören werden, zu erleichtern. Dies ist ein weiterer Vorteil der Planung eines Layouts im Voraus, sonst wären diese Regionen in diesem Stadium nicht definiert.

Routing der obersten Schicht des PiMX8-Moduls

Beim Platzieren von Leiterbahnen auf der obersten Schicht sollten wir auch berücksichtigen, dass wir etwas Platz benötigen, um Funktionen wie Fiducials oder Beschriftungen auf der obersten Schicht hinzuzufügen. Mit Laser geätzte Datenmatrix-Codes können ebenfalls entweder eine solide Kupferfläche oder ein Bereich ohne Leiterbahnen erfordern, um einen homogenen Kontrast zu bieten, was bedeutet, dass diese Bereiche nicht für das Routing verwendet werden können.

Routing der inneren Signallagen

Die meisten Verbindungen werden auf den beiden inneren Signallagen platziert, die wir im Layer-Stack-Manager definiert haben. Beginnen wir mit dem Verlegen aller hochgeschwindigkeits-synchronen Schnittstellen. In unserem Fall könnten dies die MIPI-CSI, MIPI-DSI und LVDS Schnittstellen sein. Diese Schnittstellen verwenden alle eine Niederspannungsdifferenzsignalübertragung und führen eine dedizierte Taktleitung sowie mindestens zwei Datenleitungen. Sie benötigen viel Routingplatz, da die Länge jeder Datenleitung innerhalb eines bestimmten Zeitfensters an die Taktleitung angeglichen werden muss. Das Anpassen der Länge mehrerer Differenzialpaare kann viel Platz erfordern, da es sehr wahrscheinlich ist, dass eines oder mehrere Paare innerhalb der Schnittstelle eine signifikante Verzögerung einführen, die berücksichtigt werden muss. Indem wir diese Schnittstellen zuerst verlegen, können wir sicherstellen, dass später genügend Raum für die Längenanpassung zur Verfügung steht.

Das Platzieren von Rücklaufpfad-VIAs in der Nähe der Lagenübergänge dieser Hochgeschwindigkeits-Differenzialpaare ist ebenfalls wichtig, um die Signalintegrität zu gewährleisten. Die Rücklaufpfad-VIAs können Platz auf mehreren Lagen beanspruchen, daher sollten diese VIAs platziert werden, sobald ein Signalübergang erfolgt ist.

Als Nächstes können wir die anderen Hochgeschwindigkeitsschnittstellen wie PCIe, USB, HDMI und Ethernet routen. Diese Schnittstellen haben weniger strenge Anforderungen an die Längenabgleichung zwischen den Paaren, sodass wir nicht so viel Platz für den Längenabgleich aufwenden müssen. Eine solide Rückwegverwaltung und grundlegende Ansätze für das Hochgeschwindigkeitsdesign bei diesen Signalen sind dennoch sehr wichtig, auch wenn sie auf der Prioritätenliste für das Routing an zweiter Stelle stehen.

Zuletzt können wir die verbleibenden Schnittstellen mit niedrigerer Geschwindigkeit wie SDIO, GPIO, RGMII und andere verschiedene Busse wie UART oder I2C und SPI routen. Diese Schnittstellen arbeiten immer noch mit hohen Flankenraten, was bedeutet, dass wir sie immer noch als Hochgeschwindigkeitssignale behandeln müssen.

Routing der inneren Signallage 1

Routing der inneren Signallage 2

Routing der unteren Lage

Im Falle des PiMX8-Boards können wir die untere Lage in Bezug auf den verfügbaren Platz als eine innere Routinglage behandeln. Die meisten aktiven Komponenten sind auf der oberen Lage des Moduls platziert, wobei nur eine Handvoll Spannungsregler und passive Komponenten wie Entkopplungskondensatoren und Konfigurationswiderstände auf der unteren Lage verbleiben.

Die Routingpriorität auf der Unterseite entspricht der der inneren Lagen, daher beginnen wir mit den MIPI-CSI, MIPI-DSI und LVDS-Schnittstellen. Auf dem PiMX8-Modul kann ein Hochgeschwindigkeits-Multiplexer zwischen den DSI- und LVDS-Ports wählen. Dieses Bauteil wird nahe dem Board-zu-Board-Steckverbinder auf der Unterseite platziert. Aufgrund des Pinouts des Multiplexers gibt es eine signifikante Verzögerung auf einer der Signalleitungen, die mit dem Mux verbunden sind. Wir müssen dies während des Längenabgleichs genauer betrachten, aber wir müssen etwas Platz auf der Unterseite reservieren, um eine größere Verzögerung zuzulassen.

Multiplexer-Pinbelegung mit einer langen Leitung in der Schnittstelle

Routing auf der Unterseite PiMX8-Modul

Es gibt einige Szenarien auf dem PiMX8-Modul, die während der Verzögerungsabstimmung besondere Aufmerksamkeit erfordern. Wir werden intensiv X-Signale nutzen, um einige dieser Herausforderungen zu bewältigen. Was genau diese Herausforderungen sind und wie wir X-Signale einsetzen können, um eine präzise Verzögerungsabstimmung über ein von mehreren Schnittstellen geteiltes Bauteil zu ermöglichen, wird Teil des nächsten Updates sein. Bleiben Sie dran!