Was sind Chiplets und wie werden sie in der Verpackung verwendet?

Chiplets sind kleine IC-Dies mit spezialisierter Funktionalität. Sie sind dafür konzipiert, kombiniert zu werden, um einen größeren integrierten Schaltkreis zu bilden, was dem Trend der Halbleiterindustrie zur heterogenen Integration folgt. Die Möglichkeit, aus einer Auswahl kleiner, hochspezialisierter Chips auszuwählen und diese dann zu mischen und zu kombinieren, um eine gewünschte Gesamtfunktionalität zu erzeugen, ist ein großer Fortschritt gegenüber dem traditionellen System-on-Chip (SoC)-Ansatz für Halbleiterverpackungen. Große Anbieter haben Computerprozessoren produziert, die eine ausgewählte Anzahl von Chiplets kombinieren, anstatt den traditionellen Weg der monolithischen Halbleiterfertigung zu gehen, bei dem das Gerät auf einem einzigen Siliziumstück hergestellt wird.

Obwohl die Idee von Chiplets seit Jahrzehnten existiert, treibt die auf Chiplets basierende Verpackung neue Arten von Komponenten, Produkten und Systemen für spezialisierte Anwendungen voran. Diese Komponenten sind für spezifische Anwendungen maßgeschneidert, und mehr Unternehmen steigen mit einem Fokus auf Chiplets als ihren Kernprozessor in das Chip-Design-Spiel ein. Basierend auf der Anzahl von Forschungsarbeiten, Patentanmeldungen und technischen Artikeln, die Sie online finden, ist klar, dass auf Chiplets basierende Komponenten hier bleiben werden.

Wenn Sie ein Systemdesigner sind und Prozessoroptionen abwägen, ist Ihnen möglicherweise nicht bewusst, dass Chiplets die Grundlage für Ihr System bilden. Chiplets sind jedoch das Rückgrat, das vielfältige Funktionalitäten in modernen Chips ermöglicht, und das Verpackungskonzept treibt weiterhin die Integration neuer Funktionen in Chip-Designs voran. Beispiele hierfür sind die Integration von FPGA-Blöcken und AI-Beschleunigerblöcken in dasselbe Paket wie Speicher, eine CPU und sogar RF-Komponenten.

Warum Chiplets?

Kosten und Leistung sind die beiden drängendsten Probleme im Chip-Design und in der Fertigung. In den letzten Jahren haben sich das Dennard-Scaling und Moores Gesetz verlangsamt, was zu längeren Zeiträumen zwischen den Prozesstechnologieknoten führt. Darüber hinaus wird die Transistorintegration auf einem monolithischen Chip zunehmend herausfordernder, da es nur wenige Optionen für die Skalierung von Geräten gibt. Diese Herausforderungen haben den ROI für monolithische Halbleiter aufgrund kostspieligerer Herstellungsprozesse verringert.

Der einzige Weg, die Anzahl der integrierten Funktionseinheiten bei gleicher Transistorgröße zu erhöhen, besteht darin, die Chipfläche entweder in der Geräteebene oder vertikal zu erweitern. Das Problem bei der Vergrößerung der Chipfläche ist, dass die größeren Chips anfälliger für Herstellungsfehler sind, was die Waferausbeute begrenzt und den Preis der an die Kunden gelieferten Produkte erhöht. Folglich werden monolithische Chips zunehmend unfähig, die gewünschte Leistung angesichts der steigenden Rechenanforderungen zu liefern.

Um Hochleistungsanwendungen wie AI/ML auf dem Gerät, ultraschnelle Netzwerke, Sensorfusion und Mobilgeräte der nächsten Generation zu unterstützen, haben wir das Aufkommen von chiplet-basierten Systemen für die kosteneffektive Entwicklung von Hochleistungselektronik beobachtet. Dies reicht von fortschrittlichen SoCs bis hin zu Desktop-/Serverprozessoren und GPUs.

Überwindung der „Flächenmauer“

Das Problem der "Flächenmauer" resultiert aus einem Missverhältnis zwischen dem Bedarf an großen Chips in Hochleistungscomputersystemen und der geringen Ausbeute in der Halbleiterfertigung. Die Flächenmauer bezieht sich auf diese Herausforderung in der monolithischen Halbleiterfertigung, wo größere Chips verwendet werden, um die Funktionsdichte zu erhöhen, aber auch die Fehleranzahl steigt. Da die Fertigungskapazitäten zu fortschrittlicheren Knoten übergehen, sinkt die Ausbeute des Prozesses und somit steigen die Kosten für den Endkunden. Daher besteht immer die Motivation, die Fertigung dieser Produkte durch die Eliminierung von Fehlerquellen zu entrisiken.

Eine Lösung für die Flächenmauer würde die Gesamtkosten eines Endprodukts durch die Reduzierung von Abfall während der Fertigung senken. Chiplets diversifizieren im Wesentlichen das Risikoprofil eines Produkts, indem sie es auf mehrere Halbleiterdies verteilen. Das Endergebnis sind reduzierte Kosten und die Fähigkeit, die Funktionalität in viel größerem Umfang als bei einem monolithischen Bauteil zu diversifizieren.

Reduzierte Kosten

Mehrere Chiplets werden mit speziellen Verpackungstechniken kombiniert, um einen größeren IC als Alternative zu einer monolithischen Struktur zu bilden. Da Chiplets auf einer kleineren Fläche hergestellt werden, normalerweise auf runden Wafern, wird die Auswirkung von Fertigungsfehlern reduziert und die Flächennutzung erhöht. Folglich werden die Kosten gesenkt, weil die Waferausbeute deutlich höher ist, wenn Chiplets verwendet werden, um eine Komponente zu erstellen.

Heterogene Integration ist ein weiterer bedeutender Vorteil von Chiplets, insbesondere im Hinblick auf die Reduzierung von IC-Design- und Produktionskosten. Jedes Chiplet kann unter Verwendung verschiedener Prozessknoten hergestellt werden, etwas, das AMD mit ihrem Ryzen 7 Produkt offenbarte. Ein weiteres Beispiel von AMD ist ein kürzlich erteiltes Patent für eine chiplet-basierte GPU; die Architektur für dieses System wird in der ursprünglichen Grafik unten gezeigt:

Mehrere Materialien (z.B. GaN und Si Chiplets) können auch mit diesem Ansatz in dasselbe Paket kombiniert werden. Die Verwendung verschiedener Prozesstechnologieknoten reduziert das Gesamtrisiko, das in das Produkt eingebaut ist; das höchste Risiko ist nur auf das Chiplet beschränkt, das im fortschrittlichsten Prozessknoten hergestellt wird, anstatt über den gesamten Chip verteilt zu sein.

Design-Wiederverwendung

Sobald ein Chiplet entwickelt wurde, kann es wiederverwendet werden, was die Kosten für Tests und Verifizierung reduziert. Die Kosteneffizienz des Chip-Designprozesses ist durch die Verwendung von Chiplet-Modulen deutlich höher, da diese wiederverwendet werden können. Ein Szenario der Chiplet-Wiederverwendung besteht darin, nur das Kern-Chiplet für einen IC zu entwerfen und herzustellen, während die restlichen Chiplets im Paket von einem anderen Anbieter bezogen werden. Durch diesen Ansatz mit fertigen Chiplets von mehreren Anbietern oder durch die Wiederverwendung von IP in einem neuen Design werden die gesamten Design- und Verifizierungskosten des Produkts erheblich reduziert.

Falls ein Update des Systems erforderlich ist, kann ein Chiplet innerhalb der Verpackung durch ein anderes Chiplet ausgetauscht werden. Beachten Sie, dass die Verpackung selbst aktualisiert werden muss, aber dies ist eine viel weniger schwierige Designaufgabe als das Neudesign einer gesamten monolithischen Komponente. Ein kleiner Teil des Systems könnte auch ohne die neuen Verifizierungskosten, die bei monolithischen Halbleiterpaketen entstehen würden, neu gestaltet werden. Diese Methode der Chiplet-Wiederverwendung wird als „heterogene Wiederverwendung“ bezeichnet.

Ein weiteres Szenario der Chiplet-Wiederverwendung ist die Integration mehrerer identischer Chiplets in dasselbe System. Diese Methode ist ideal für skalierbare Systeme und verbessert deren Effizienz erheblich, während sie die Kosten senkt. Dies wird als die homogene Wiederverwendungsmethode bezeichnet und der Hauptvorteil ist, dass die Erhöhung der Anzahl der Chiplets in der Architektur alles ist, was benötigt wird, um die verschiedenen Leistungs- und Energieanforderungen zu erfüllen.

Chiplet-Verpackungstechnologien

Um chiplet-basierte Produkte herzustellen, benötigen Sie Designfähigkeiten, Dies, Verbindungen zwischen den Dies und eine Produktionsstrategie. Die Leistung, der Preis und die Reife der Chiplet-Verpackungstechnologien haben einen erheblichen Einfluss auf die Anwendung von Chiplets. Entsprechend den Unterschieden im Verbindungsmedium und den Methoden können die Verpackungstechnologien, die für die Verbindung von Chiplets verwendet werden, in drei Gruppen eingeteilt werden:

-

Substratverpackung

-

Silizium-Interposer-Verpackung

-

Redistribution-Layer (RDL)-Verpackung

-

Embedded Multi-Die Interconnect Bridge (EMIB)

Substratbasierte Verpackung

Bei der substratbasierten Verpackung ist die beliebte Wahl des Substrats ein organisches Material, da diese leicht verfügbar sind. Ähnlich wie bei herkömmlichen PCBs werden Verdrahtungsverbindungen durch einen Ätzprozess hergestellt, der unabhängig von anderen in der Halbleiterfertigung verwendeten Prozessen ist. Dies ist als die früheste Inkarnation der 2D-heterogenen Integration bekannt.

Durch Flip-Chip-Design oder Stapelung können mehrere Dies leicht mit einem Substrat mit hoher Dichte verbunden werden. Darüber hinaus sind die Material- und Herstellungskosten damit minimal, da diese Technologie nicht vom Chip-Herstellungsprozess abhängt. Der Hauptnachteil der Verwendung dieser Technologie ist die geringe Dichte der I/O-Pins und die daraus resultierende Begrenzung der Bandbreite der Verbindungen in diesen Paketen.

Silizium-Interposer-Verpackung

Diese Technologie umfasst 2,5D- und 3D-Packaging-Technologien, bei denen Chips seitlich auf einem Interposer (2,5D) aufgebaut oder vertikal gestapelt (3D) werden. Um Verbindungen und Kommunikation zwischen den Dies zu implementieren, wird die Silizium-Interposer-Schicht zwischen dem Substrat und den Dies platziert. Der Interposer ist wie eine Miniatur-Platine, die im Wesentlichen ein Substrat für elektrische Verbindungen zwischen Chiplets bereitstellt. Das Verbindungsnetzwerk wird aus metallischen Kontakten (sogenannten Mikrobumps) und durch Silizium verlaufenden Vias (TSV) im Inneren des Pakets aufgebaut. Diese werden verwendet, um das Die mit dem Interposer zu verbinden, und die Interposer-Verbinder mit einem Paket-Substrat mit einem BGA-Landmuster.

Diese Produkte haben eine höhere I/O-Dichte mit reduziertem Energieverbrauch und geringerer Übertragungsverzögerung. Dies wird durch die kleinere Spurlänge und den geringeren Abstand zwischen Mikrobumps und TSVs ermöglicht. Der einzige bedeutende Nachteil dieser Technologie sind die erhöhten Fertigungskosten.

RDL-Packaging

Die Redistribution-Layer-(RDL-)Packaging-Technologie verwendet kein Substrat, sondern beinhaltet die direkte Abscheidung des Dielektrikums und des Metalls direkt auf der Oberfläche des Wafers. Diese Technologie wird auch als „Fanout“-Technologie bezeichnet. Um das Drahtdesign zu tragen, wird eine Redistributionsschicht so konstruiert, dass die I/O-Ports auf jedem Chiplet um das Gerät herum angeordnet sind. Durch die Verkürzung der Länge des Stromkreises bietet RDL eine bessere Signalintegrität (geringerer Verlust und Verzerrung).

Eingebettete Multi-Die-Interconnect-Brücke

EMIB ist eine Technologie, die dünne Silizium-Waferschnitte, die in organische Materialien als Substrate für Die-zu-Die-Verbindungen eingebettet sind, verwendet. Das Problem höherer Kosten bei fortschrittlichen Produkten kann durch die Verwendung von Bridge-Packaging mit verschiedenen Chiplets angegangen werden. Diese Hybrid-Packaging-Technologie ist eine Kombination aus Substrat-basiertem und Interposer-basiertem Packaging. Dünne Siliziumschichten, in der Regel weniger als 75 Mikrometer, werden auf das Substrat aufgetragen und verwendet, um Verbindungen zwischen den Dies zu bilden, und diese Schichten sind in einer organischen Substratschicht eingebettet.

Das Konzept folgt den gleichen Ideen wie ELIC, die bei HDI-PCBs verwendet werden, wo ein Verbindungsnetzwerk jeder Schicht mehrere Dies mit internen Schichten in einem isolierenden (organischen) Substrat verbindet. Der EMIB-Teil des Pakets ist eine Siliziumbrücke, die Hochbandbreitenverbindungen zwischen Chiplets bereitstellt.

Fazit

Es wird erwartet, dass Chiplets weiterhin Anwendungen revolutionieren, die hochleistungsfähige Komponenten sowie vielfältige Funktionalitäten in einem einzigen Paket erfordern. Diese Produkte zielen derzeit auf fortschrittliche Technologien wie 5G, IoT, Automobiltechnik, Edge Computing, medizinische Bildgebung, Edge Computing, KI, mobile Geräte und vieles mehr ab.

Heute haben sich große Halbleiterhersteller wie Intel, Marvell und AMD der Chiplet-Technologie zugewandt, und wir können erwarten, dass mehr Unternehmen diese Option erkunden. Wenn sich ein Markt für Chiplet-IP entwickelt, ähnlich wie sich ein Markt für viele andere Komponenten entwickelt hat, könnten mehr fabless Halbleiterunternehmen einen kundenspezifischen Halbleiteransatz wählen, anstatt Systeme mit diskreten Komponenten zu bauen.

Jetzt, da sich Intel, AMD und TSMC auf einen gemeinsamen Standard für Chiplet-Verbindungen geeinigt haben, werden wir eine größere Verbreitung dieser Designs durch andere Unternehmen sehen? Man kann hoffen, dass sich ein Markt für diese Komponenten entwickelt, da dies mehr Innovation auf der Verpackungsebene über die großen Halbleiterhersteller hinaus fördern wird.

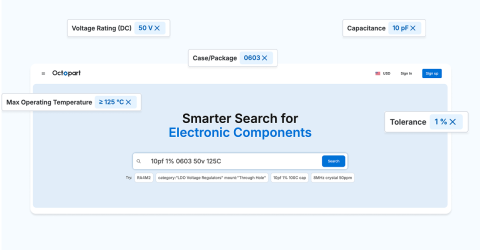

Wenn chiplet-basierte Komponenten mit fortschrittlicher Verpackung auf den Markt kommen, können Systemdesigner die fortgeschrittenen Such- und Filterfunktionen in Octopart nutzen, um alle fortschrittlichen Komponenten zu finden, die sie für fortschrittliche Designs benötigen. Wenn Sie die Elektroniksuchmaschine von Octopart verwenden, haben Sie Zugang zu aktuellen Distributorenpreisdaten, Teilebeständen und Teilespezifikationen, und das alles ist frei zugänglich in einer benutzerfreundlichen Schnittstelle. Schauen Sie sich unsere Seite mit integrierten Schaltkreisen an, um die Komponenten zu finden, die Sie benötigen.

Bleiben Sie mit unseren neuesten Artikeln auf dem Laufenden, indem Sie sich für unseren Newsletter anmelden.