Längenanpassung in High Speed Signalen

Mit den immer weiter steigenden Übertragungsgeschwindigkeiten in High-Speed Designs gehen einige Herausforderungen im Leiterplattenlayout einher. High-Speed Bussysteme wie DDR, VME, PCIe, um nur Einige zu nennen, erreichen Geschwindigkeiten, die ein Design mit sehr engen Toleranzen in Bezug auf die Laufzeitverzögerungen erfordern, und somit auch kaum Kompromisse beim Layout. Nehmen Sie an diesem Webinar teil um zu sehen, was erforderlich ist, um Laufzeitverzögerungen und Längenanpassungen in High-Speed Designs, auch mit differentiellen Paaren, zu realisieren. Wir werden Ihnen auch zeigen, wie Sie die passenden Design-Regeln erstellen und dann darauf basierend interaktiv Ihr Design mit Altium Designer® routen können.

Folgende Themen werden besprochen:

-

Wieso ist es wichtig,in High-Speed Designs eine Längenanpassung vorzunehmen?

-

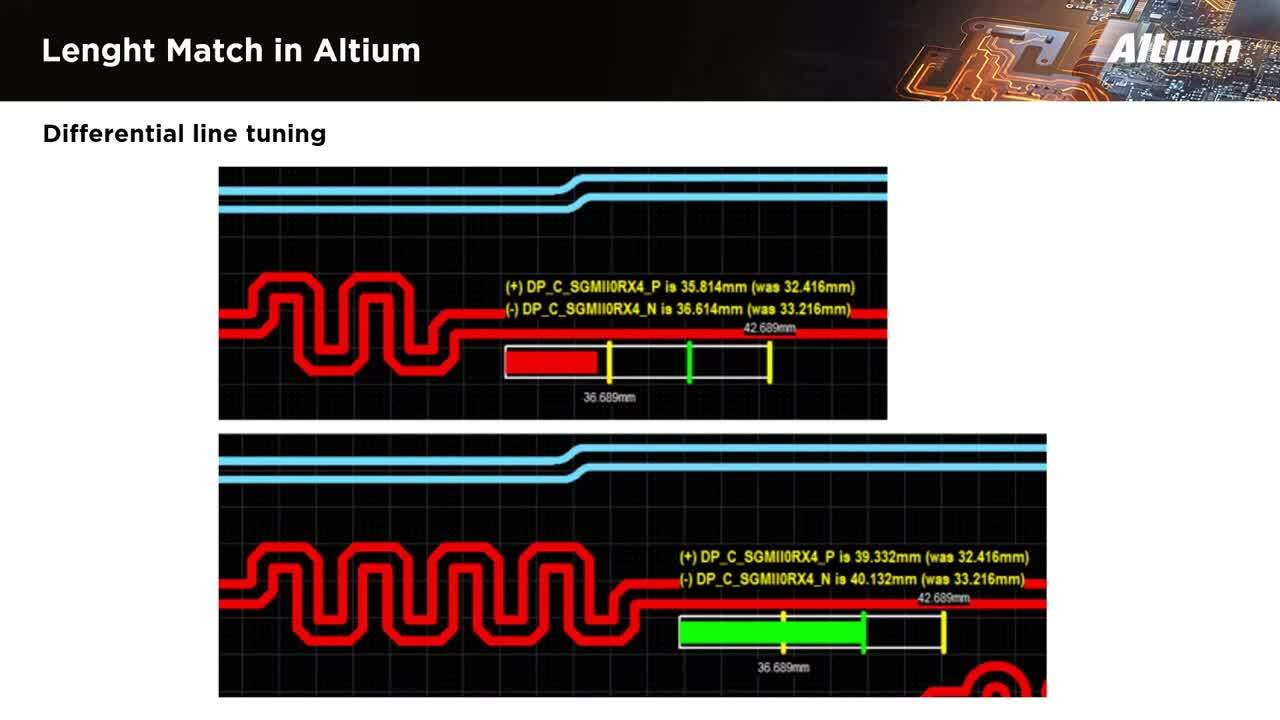

Längenanpassung und Laufzeitverzögerungen anpassen in High-Speed Bus-Systemen und differentiellen Paaren

-

Wie erstellt man High-Speed Design-Regeln im Schaltplan oder PCB?

-

Wie stimmt man Einzelsignale und differentielle Paare ab?

Ähnliche Resourcen

Vom Entwurf bis zur Freigabe – ganz ohne Reibungsverluste

- Prüfungen an die richtige Version binden

- Verwirrung bei Übergaben und Nacharbeit reduzieren

- Beschaffungs- und Freigaberisiken früher erkennen

- Allein arbeiten, bei Bedarf teilen

Erste Schritte