Un breve estudio de los stubs en un conector PCIe

Los stubs son un tema importante en el diseño de PCBs de alta velocidad, y existe una directriz de larga data que indica que los stubs siempre deben eliminarse de todas las vías en interconexiones digitales de alta velocidad. Aunque los stubs son perjudiciales para las líneas de alta velocidad, no siempre necesitan ser eliminados. Lo que es más importante es predecir el perfil de pérdida y las frecuencias, y planificar el diseño de manera adecuada para intentar prevenir dichas pérdidas.

En este artículo, examinaré algunos resultados de simulación con el enrutamiento PCIe en un PCB de alta velocidad usando el ejemplo del proyecto MiniPC que viene incluido en Altium Designer. La simulación en cuestión involucrará el cálculo de parámetros S para las pistas PCIe que salen de un conector. Mirar estos resultados de simulación debería ayudar a los diseñadores no familiarizados a comprender mejor cómo los stubs en las transiciones de vía y conector influyen en la integridad de la señal desde una perspectiva de simulación, lo que puede ayudarte a tomar las decisiones correctas de selección de componentes, colocación y enrutamiento.

Problemas Potenciales con Stubs y el Enrutamiento PCIe

En el enrutamiento PCIe, las pistas se enrutan como pares diferenciales con capacitores de acoplamiento AC. Es típico enrutar estos pares diferenciales a través de un conector para alcanzar un periférico, como una tarjeta de expansión. En el proceso de enrutamiento a través de estos conectores de ranura de expansión, puede haber un pequeño sobrante en la línea que puede limitar el ancho de banda máximo. Esto puede evaluarse en simulación para obtener resultados muy precisos y para identificar el ancho de banda exacto de un canal PCIe.

Los sobrantes en cualquier línea de transmisión de alta velocidad pueden crear pérdidas o reflexiones ya que pueden actuar como transformadores de impedancia de alta frecuencia en una pista PCIe. Lea más sobre el análisis de sobrantes en este artículo.

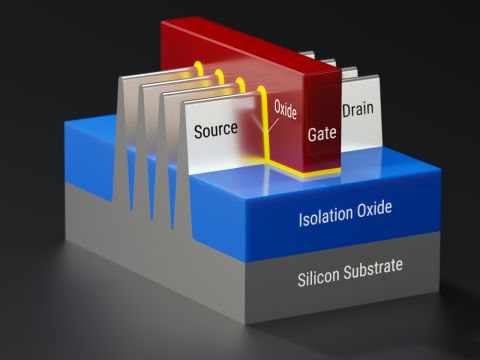

Aunque se recomienda limitar los sobrantes en una pista PCIe, podrían estar presentes en el conector utilizado para enrutar hacia una tarjeta de expansión o módulo. Como ejemplo, el conector de borde utilizado para una tarjeta de expansión PCIe montada verticalmente podría ser un componente pasante, y esos sobrantes pueden jugar un papel en la limitación del ancho de banda de señal utilizable cuando se enruta en la misma capa que el conector. Enrutar en la capa opuesta puede ser preferible, particularmente al considerar la colocación del capacitor.

Un Ejemplo con Pérdidas por Sobrantes de Conector en una Pista PCIe

Debido a los efectos de interferencia conocidos que ocurren cuando una señal atraviesa un vía stub, así como la necesidad de capacitores para eliminar el desplazamiento de CC a lo largo de una línea PCIe, vale la pena estudiar en qué medida los vía stubs pueden afectar las pérdidas al enrutar a través de un conector.

La placa MiniPC en cuestión utiliza un FPGA Arria 10 con una interfaz PCIe, que se enruta a un conector de ranura, como se muestra a continuación.

Las otras especificaciones importantes que necesitamos conocer para el análisis a continuación son el grosor de la placa y la constante dieléctrica:

- Grosor de la placa = 2.028 mm

- Dk = 3.6 en todas las capas

Aunque el diseño no se creó con un FPGA que tenga la generación más nueva de PCIe, evaluaremos las pérdidas en estos canales comparándolas con los requisitos de ancho de banda en diferentes generaciones de PCIe.

Resultados Iniciales de la Simulación

Los resultados de la simulación de pérdida de inserción para las redes Tx se capturaron usando Ansys SIwave; estos resultados se muestran a continuación. Para introducir la placa en Ansys SIwave, utilizamos la utilidad EDB Exporter dentro de Altium Designer. En los resultados a continuación, vemos una caída justo alrededor de 14-15 GHz alcanzando hasta -25 dB, y luego recuperándose a niveles de pérdida más bajos en frecuencias más altas.

¿Cómo sabemos que esta pérdida extrema se debe a un stub? Simplemente mirando el gráfico no se prueba que el problema sea causado por stubs, pero hay dos buenas razones para concluir que esto podría ser un stub:

- Si calculas la primera resonancia de longitud de onda cuarto en estos stubs, encontrarás que la primera caída se esperaría en alrededor de 13 GHz. Eso está bastante cerca de las resonancias de 14-15 GHz que se ven arriba.

- El perfil de pérdida alrededor de 14-15 GHz tiene un ancho de banda estrecho, que es exactamente lo que esperarías de la interferencia destructiva en un resonador de Q moderada.

- Todas las curvas tienen la forma típica de un gráfico de pérdida de inserción que presenta comportamiento de stub, y todas las redes consideradas tienen stubs en el diseño del PCB.

La caída en este gráfico limita la tasa de transferencia de datos a cualquier valor correspondiente a una frecuencia de Nyquist de aproximadamente 8 GHz (o 16 Gbps para señalización de 2 niveles/NRZ). Esto estaría bien para PCIe Gen4 pero no para Gen5. Si quisiéramos eliminar totalmente esta pérdida o reutilizar este diseño con una interfaz Gen5, entonces el diseño necesitaría ser modificado.

Investigación y Cambios Adicionales

Algunas opciones para cambiar el diseño incluyen:

- Conecte los pines del conector a los capacitores en la capa trasera a través de vías: Aunque hay algunas transiciones de vía adicionales, la conexión saldría de la capa trasera y a través de las vías hacia los capacitores, eliminando efectivamente los muñones sin necesidad de taladrado posterior.

- Reemplace el conector por un equivalente SMD: Esto eliminaría totalmente los muñones sin requerir transiciones de dos capas a través de los pines del conector y las vías. Esta es también la solución más simple ya que no requiere ningún cambio de componentes, aunque sí requiere algo de reenrutamiento.

- Taladre todos los muñones: Esto requiere algunos costos adicionales y dejará una pequeña cantidad de muñón restante (generalmente alrededor de 10 mil), por lo que es mejor usarlo cuando los muñones son muy largos.

Si el diseño ya está completo, las opciones #1 y #2 suelen ser las mejores ya que podrían requerir la menor cantidad de retrabajo, aunque #2 dependerá de lo que haya en las capas inferiores. Para la opción #1, aquí hay un ejemplo de conector con montaje SMD. La opción #3 es apropiada si está dispuesto a pagar los costos de taladrado de profundidad controlada durante la fabricación.

Se podría esperar este tipo de comportamiento, donde se observa un problema de integridad de señal como pérdida alta o alta reflexión en frecuencias específicas, que provenga de stubs que resuenan fuertemente cuando se excitan. Para evaluar por qué esto podría suceder en un canal diferencial, es necesario calcular el conjunto de resonancias estructurales en la estructura del stub de vía. Una guía que muestra cómo se hace esto se puede encontrar en el video a continuación.

Cuando necesite evaluar su diseño en un flujo de trabajo integral impulsado por simulación, utilice el conjunto completo de características de diseño, disposición y simulación de PCB en Altium Designer®. Cuando necesite examinar problemas de integridad de señal y extraer parámetros S de sus sistemas, puede usar la extensión EDB Exporter para importar un diseño a los solucionadores de campo de Ansys y realizar una gama de simulaciones SI/PI. Cuando haya terminado su diseño y quiera liberar archivos a su fabricante, la plataforma Altium 365™ facilita la colaboración y el compartir sus proyectos.

Solo hemos arañado la superficie de lo que es posible con Altium Designer en Altium 365. Comienza tu prueba gratuita de Altium Designer + Altium 365 hoy.