FPGAs: Creando Pipelines de Integración Continua para Sistemas Embebidos o PCBs

En este artículo, Ari Mahpour te guía a través de la creación de pipelines de Integración Continua dirigidos para FPGAs

Las Field Programmable Gate Arrays, o FPGAs, se han vuelto omnipresentes en los sistemas digitales en tiempo real y de alta velocidad. Se pueden utilizar para aplicaciones críticas en tiempo, procesamiento de señales digitales o incluso minería de criptomonedas. Su eficiencia en velocidad y potencia los hace perfectos para aplicaciones reutilizables de alta velocidad. La velocidad a la que operan las FPGAs sigue aumentando a un ritmo vertiginoso, pero su adopción en los pipelines de Integración Continua (CI) no parece estar a la par. En este artículo, revisaremos el concepto de pipelines de CI, su aplicación a las FPGAs, y veremos ejemplos de cómo configurarlos.

Integración Continua y FPGAs

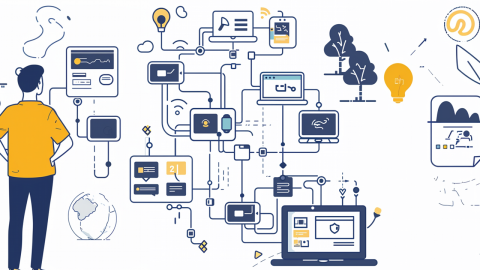

Si no lo has notado aún, prácticamente vivo y respiro Integración Continua. Ya sea CI para diseño de PCB o CI para sistemas embebidos, siempre busco maneras de mejorar y automatizar continuamente las compilaciones para cualquier tipo de sistema. Algunos comentarios recientes que he recibido es que no se ha avanzado mucho con las FPGAs y los sistemas de CI. El verdadero principio detrás de CI y FPGAs sigue la misma lógica que todos los demás sistemas de CI: crear un entorno de compilación repetible que pueda hacer todo el trabajo pesado por nosotros. En un sistema CI basado en FPGA, típicamente veríamos las siguientes tres etapas:

Figura 1: Etapas de un pipeline de CI de FPGA

Cada etapa es importante en sí misma y todas requieren su propia configuración. Veamos cada etapa para comprender lo que representan y cómo implementarlas.

Simulación

La simulación es una parte integral del diseño de FPGA. Crear una imagen de FPGA para cargar en un objetivo puede llevar mucho tiempo. En lugar de escribir código, compilarlo y probarlo en hardware, la simulación nos permite probar rápidamente nuestro código, o Register-Transfer Level (RTL), dentro de un entorno que simula el comportamiento de un FPGA. Generalmente, esto se realiza a nivel de usuario, pero está siendo cada vez más popular integrar la simulación de FPGA en los pipelines de CI. Esto significa que alguien subiría su código a su repositorio y se iniciaría un pipeline para ejecutar la simulación (autoverificante) en algún lugar de la nube. Para hacer esto realmente "en algún lugar de la nube", se necesita crear un entorno que pueda encapsularse o containerizarse en un entorno autosuficiente. Hacemos esto utilizando algo llamado contenedores Docker. Estos actúan casi como máquinas virtuales que se pueden ejecutar en cualquier lugar. Este contenedor Docker en particular, por ejemplo, crea un entorno containerizado que permite a un usuario ejecutar Icarus Verilog en cualquier sistema Linux. Luego tomamos ese contenedor y lo usamos para crear nuestro pipeline de simulación de FPGA. En este ejemplo, puedes ver un simple pipeline de “Hello World” sucediendo en la nube utilizando Icarus Verilog. Ten en cuenta que esto se puede hacer con cualquier herramienta de simulación de FPGA.

Figura 2: Ejecución del pipeline de simulación de FPGA utilizando Gitlab CI

Construcción

Una segunda etapa, también muy importante, dentro de la canalización de FPGA es la etapa de construcción. Queremos poder sintetizar, colocar y enrutar, y generar un bitstream para nuestro diseño de FPGA. Esto también suele hacerse por los usuarios dentro de la herramienta proporcionada por el proveedor (por ejemplo, Xilinx, Intel, Microchip, etc.). En lugar de realizar esta construcción localmente, nos gustaría que ocurriera en otro lugar. Sin embargo, esto puede ser un poco complicado ya que las herramientas de FPGA suelen ser muy grandes. Un enfoque que muchos usuarios adoptan es tener una "máquina de construcción" dedicada que ejecute todas las canalizaciones de construcción. Este enfoque no está mal, pero tampoco escala y puede convertirse en un punto único de falla. Otros han intentado contenedorar herramientas de FPGA, pero esas imágenes pueden superar los 100 GB, lo que esencialmente las hace inutilizables para aplicaciones en la nube. Un término medio que he encontrado que funciona bien es el método de instalación en red. Como ejemplo, he creado un contenedor que ejecuta Vivado 2019.1, pero la herramienta en sí no está instalada en la imagen (por lo tanto, el tamaño de la imagen es inferior a 300 MB). Lo que he hecho es instalar Vivado en una unidad de red (en este caso EFS en AWS) y luego montarlo dentro de mi contenedor Docker. Como estoy ejecutando mi canalización en AWS, la latencia entre el EFS y la instancia EC2 (nodo de Kubernetes) es insignificante.

En este ejemplo, estoy usando un dispositivo Arty A7 de Digilent para crear un filtro digital. Estoy utilizando un script de construcción automatizado para generar el archivo bitstream para mi dispositivo en cada envío a mi repositorio. Como puedes ver en la salida, llamo con éxito a Vivado, aunque no existe dentro del contenedor Docker (es decir, está montado como una unidad externa).

Figura 3: Ejecución de la canalización de construcción de FPGA usando Gitlab CI

Pruebas

La fase de pruebas realmente va a depender de cada individuo y proyecto. El objetivo de las pruebas dentro de una canalización de CI es automatizar tanto como sea posible. Así como automatice mi ejemplo de DSP para Arduinos con mi Analog Discovery 2, también podría hacer lo mismo aquí. Cubrir una solución de pruebas automatizada para FPGAs estaría un poco fuera del alcance de este artículo. El principio principal aquí es asegurarse de que sea repetible y se ejecute dentro de un entorno encapsulado o contenedorizado. Es importante recordar que las pruebas son una pieza importante de la canalización de CI y deben implementarse en el nivel que el usuario pueda manejar.

Conclusión

En este artículo cubrimos el concepto de canalizaciones de CI para FPGAs. Revisamos las tres etapas críticas que componen las canalizaciones de FPGA: simulación, construcción y pruebas. Vimos ejemplos de canalizaciones de simulación y construcción y discutimos la importancia de las pruebas. Después de revisar este artículo y los ejemplos, el usuario debería poder comprender la composición básica de lo que se necesita para crear una canalización de CI basada en FPGA.

Cuando estés listo para construir tu placa FPGA personalizada para soportar tu sistema embebido, utiliza el conjunto completo de características de diseño y disposición de PCB en Altium Designer®. Una vez que hayas completado tu PCB y estés listo para compartir tus diseños con colaboradores o tu fabricante, puedes compartir tus diseños completados a través de la plataforma Altium 365™. Todo lo que necesitas para diseñar y producir electrónica avanzada se encuentra en un solo paquete de software.

Solo hemos arañado la superficie de lo que es posible hacer con Altium Designer en Altium 365. Comienza tu prueba gratuita de Altium Designer + Altium 365 hoy.