FPGA:組み込みシステムまたはPCBのための継続的インテグレーションパイプラインの作成

この記事では、Ari MahpourがFPGA向けの継続的インテグレーションパイプラインの作成方法を説明します

FPGA(Field Programmable Gate Arrays、フィールドプログラマブルゲートアレイ)は、高速かつリアルタイムなデジタルシステムにおいて、非常に広く普及しています。これらは、時間が重要なアプリケーションやデジタル信号処理、さらには暗号通貨のマイニングなどに使用されます。FPGAの速度と電力効率の高さにより、再利用可能な高速アプリケーションに最適です。FPGAの動作速度は目まぐるしい速さで向上していますが、そのCI(継続的インテグレーション)パイプラインへの導入はそれほど急速に進んでいないようです。この記事では、CIパイプラインの概念、それがFPGAにどのように適用されるか、そしてその設定方法の例について見ていきます。

継続的インテグレーションとFPGA

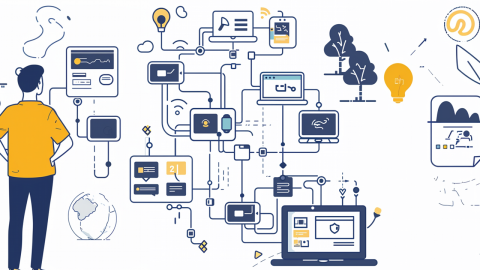

今まで気づかなかった方のために言うと、私はほぼ毎日CI(継続的インテグレーション)を考えています。PCB設計のためのCIであれ、組み込みシステムのためのCIであれ、どんなシステムでもビルドを継続的に改善し、自動化する方法を常に模索しています。最近得たフィードバックの中には、FPGAとCIシステムに関してあまり進展が見られていないというものがありました。FPGAとCIの背後にある基本原則は、他のすべてのCIシステムと同じ論理に従います。つまり、私たちのためにすべての重作業をこなす、繰り返し可能なビルド環境を作り出すということです。FPGAベースのCIシステムでは、通常、以下の3つのステージが見られます。

図1: FPGA CIパイプラインのステージ

各ステージはそれ自体で重要であり、それぞれに固有のセットアップが必要です。それらが何を意味し、どのように実装されるかを理解するために、各ステージを見ていきましょう。

シミュレーション

シミュレーションはFPGA設計の不可欠な部分です。ターゲットにロードするためにFPGAイメージをビルドするには多くの時間がかかることがあります。コードを書いてビルドし、ハードウェアでテストする代わりに、シミュレーションを使うことで、FPGAの動作を模倣する環境内でコード(RTL:レジスタ転送レベル)を迅速にテストすることができます。一般的にはユーザーレベルで行われますが、FPGAシミュレーションをCIパイプラインに統合することがますます一般的になっています。これにより、誰かがリポジトリにコードをプッシュすると、どこかのクラウドでパイプラインが開始され、自己検証型シミュレーションが実行されます。これを本当に「クラウドのどこかで」行うには、自己完結型の環境にカプセル化、またはコンテナ化できる環境を作成する必要があります。これを実現するために、Dockerコンテナを使用します。これらは、どこでも実行できる仮想マシンのようなものです。この特定のDockerコンテナは、ユーザーがどのLinuxシステムでもIcarus Verilogを実行できるコンテナ化された環境を作成します。次に、そのコンテナを使用して、FPGAシミュレーションパイプラインを作成します。この例では、Icarus Verilogを使用してクラウドで実行されるシンプルな「Hello World」パイプラインを見ることができます。これは、どのFPGAシミュレーションツールでも実行できます。

図2: GitLab CIを使用したFPGAシミュレーションのパイプライン実行

ビルド

FPGAパイプライン内のもう一つの重要なステージはビルドステージです。私たちはFPGA設計のために、合成、配置および配線、そしてビットストリームの生成を行いたいと考えています。これも通常、ベンダー(例:Xilinx、Intel、Microchipなど)によって提供されるツールでユーザーが行いますが、このビルドをローカルで行うのではなく、別の場所で行いたいと考えています。しかし、FPGAツールは通常非常に大きいため、これは少し難しい場合があります。多くのユーザーが取るアプローチの一つは、すべてのビルドパイプラインを実行する専用の「ビルドマシン」を持つことです。このアプローチは悪くはありませんが、スケールしにくく、単一障害点となる可能性があります。FPGAツールをコンテナ化しようとする人もいますが、それらのイメージは100GBを超えることが多く、クラウドアプリケーションにはほぼ使用不可能となります。私がうまく機能すると思う中間策は、ネットワークインストールメソッドです。例えば、私はVivado 2019.1を実行するコンテナを作成しましたが、ツール自体はイメージ上にインストールされておらず(そのため、イメージサイズは300MB未満です)。私はVivadoをネットワークドライブ(この場合はAWSのEFS)にインストールし、Dockerコンテナ内にマウントしました。私のパイプラインはAWSで実行されているため、EFSとEC2インスタンス(Kubernetesノード)間のレイテンシは無視できる程度です。

この例では、DigilentのArty A7デバイスを使用してデジタルフィルタを作成しています。自動ビルドスクリプトを使用して、リポジトリにプッシュするたびにデバイス用のビットストリームファイルを生成しています。出力に見られるように、Dockerコンテナ内に存在しないVivadoを正常に呼び出すことができています(つまり、外部ドライブとしてマウントされています)。

図3: Gitlab CIを使用したFPGAビルドのパイプライン実行

テスト

テストフェーズは、各個人やプロジェクトによって異なります。CIパイプライン内でのテストの目的は、できる限り自動化することです。私はArduino用DSPの例をAnalog Discovery 2を使って自動化したように、ここでも同じことができます。FPGA用の自動テストソリューションをカバーすることは、この記事の範囲外ですが、ここでの主な原則は、繰り返し実行可能で、カプセル化された環境またはコンテナ化された環境内で実行できることを確認することです。テストはCIパイプラインの重要な部分であり、ユーザーが対応できるレベルで実装することが重要です。

結論

この記事では、FPGA向けCIパイプラインの概念を取り上げました。FPGAパイプラインを構成する重要な3つのステージ(シミュレーション、ビルド、テスト)をレビューし、シミュレーションとビルドパイプラインの例を見て、テストの重要性について議論しました。この記事と例をレビューすることで、FPGAベースのCIパイプラインを作成するために必要な基本的な構成を理解できるようになるでしょう。

カスタムFPGAボードを構築して組み込みシステムをサポートする準備が整ったら、Altium Designer®の完全なPCB設計およびレイアウト機能を使用してください。PCBの設計が完了し、共同作業者や製造業者と設計を共有する準備が整ったら、Altium 365™プラットフォームを通じて設計を共有できます。高度な電子機器を設計および製造するために必要なすべての機能が1つのソフトウェアパッケージに収められています。

Altium DesignerとAltium 365を使用して可能なことは、まだほんの一部に過ぎません。Altium Designer + Altium 365の無料トライアルを開始しましょう。