Regole di progettazione PCB per il layout Chip-on-Board

Esiste un tipo semplice di confezionamento che non è realmente un imballaggio nel senso convenzionale: il chip-on-board.

La rivoluzione del packaging continua a procedere spedita e i progettisti di PCB si trovano in una posizione unica per trarne vantaggio. Esiste un tipo di packaging che sarà molto più familiare ai progettisti di PCB e che non richiede alcun software di packaging speciale per essere implementato. Questa tecnica di packaging è il chip-on-board, dove un die semiconduttore è attaccato direttamente a una scheda circuitale.

Come per qualsiasi approccio di design unico, ci sono alcune regole da seguire quando si inizia un progetto chip-on-board. Queste regole riguardano la disposizione e il posizionamento, così come il design dell'interconnessione e le regole di fanout per chip più avanzati.

Chip-on-Board in un Layout PCB

Nell'approccio chip-on-board, un die semiconduttore con contatti esposti viene saldato direttamente al PCB. In altre parole, non c'è un telaio di collegamento (per il wire bonding), nessun packaging in ceramica/epossidica, e nessun interposer/substrato. Una volta attaccato, il chip può essere incapsulato direttamente sul PCB utilizzando un incapsulante epossidico, che proteggerà il chip e qualsiasi pad collegato con filo da danni.

Ci sono due metodi comuni per posizionare e montare il chip-on-board in un PCB standard:

- Collegamento diretto da PCB al die

- Assemblaggio flip-chip, dove il chip si attacca in modo simile a un BGA

Dopo l'attacco e l'assemblaggio, il chip è tipicamente incapsulato in un materiale epossidico o in una vernice conformale, ciascuno dei quali può essere indurito termicamente o con UV. Nel layout del PCB, il punto di design più importante è l'impronta che consentirà l'attacco del die al PCB.

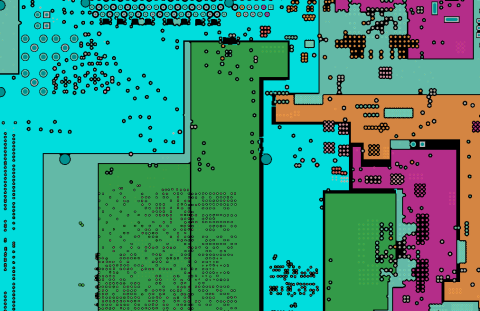

Esempio di Flip-Chip

Un esempio con un flip-chip (a volte chiamato flip-chip on board (FCOB)) è mostrato nell'immagine sottostante. Questo mostra un chip non incapsulato che è stato saldato direttamente a un PCB, in modo simile a quanto si farebbe con un fanout BGA. Un materiale importante qui è l'underfill, che incapsula le giunzioni saldate e le protegge da eccessivi stress meccanici. Il laminato del PCB potrebbe essere un materiale standard di grado FR4 o qualche materiale più specializzato (flex, PTFE, ecc.).

In questo approccio, l'impronta deve essere progettata in modo simile a un'impronta BGA, ma il processo di assemblaggio sarà diverso. In FCOB, la saldatura sarà flussata direttamente sul PCB, non è attaccata al die. Il chip verrà poi posizionato come qualsiasi altro componente SMD e verrà rifuso insieme agli altri componenti. Pertanto, è necessaria una certa DFA in termini di impronta per garantire un assemblaggio affidabile.

Consiglierei di seguire linee guida simili per la dimensione del pad BGA, ma basandosi sulla dimensione del bump invece che sulla dimensione della sfera. La maschera di saldatura e la maschera di pasta devono poi essere utilizzate per impostare la dimensione del pad esposto entro l'intervallo che normalmente sarebbe utilizzato in un BGA. Se il passo dei bump è abbastanza grande da lasciare grandi frammenti di maschera di saldatura, allora usare la maschera di saldatura per agire come una diga (pad SMD). Altrimenti, usare un pad NSMD per prevenire la sfaldatura dei frammenti di maschera di saldatura tra i bump.

Esempio di Wire Bonding

L'immagine sottostante mostra un esempio di wire bonding. In questo esempio, un pad di attacco del die è saldato direttamente sul PCB, e i collegamenti a filo sono attaccati tra i pad di terra intorno al chip e i contatti sul die. In questo design, è fortemente consigliato incapsulare con un'epossidica al fine di proteggere i collegamenti a filo e il die dall'esposizione ambientale. Ciò preverrà principalmente la corrosione, oltre a proteggere i fili da danni meccanici.

Quando si crea l'impronta per i pad di wire bonding sul PCB, i pad sono tipicamente sovradimensionati, cosa che può essere chiaramente vista nell'immagine sopra. I parametri da considerare per l'impronta includono:

- Dimensione del pad di contatto

- Passo del pad di contatto

- Forma del pad di contatto

I pad quadrati sono accettabili, sebbene i pad rettangolari possano replicare la dimensione del pad usata nel componente una volta che il die è confezionato (come in un pacchetto QFN o LQFP). Le sfere di contatto usate per connettere un filo al PCB saranno molto sottili, raggiungendo i 20 ai 30 micron di larghezza. La corrispondente larghezza del pad di contatto potrebbe essere di 50 a 150, con lo stesso valore utilizzato per il passo del pad. Utilizzando il passo del pad e i numeri di dimensionamento, puoi quindi disporre un array di pad nell'impronta del PCB per i collegamenti a filo.

Chip-on-Board più avanzati

I chip-on-board più avanzati utilizzeranno contatti a bump sulla parte inferiore del die (ad esempio, l'esempio flip-chip mostrato sopra).

L'idea dietro al design chip-on-board che diventa più avanzato è legata a due aree: il passo tra i contatti o i bump sulla parte inferiore del die, e la velocità a cui questi sistemi devono operare. Proprio come per i BGAs a passo molto fine, dove il passo dei pad può richiedere via-in-pad e vie cieche/interrotte, il packaging chip-on-board potrebbe richiedere lo stesso. Inoltre, la velocità a cui questi die e le loro interfacce operano esclude qualsiasi standardizzazione, eccetto per le interfacce di calcolo come USB, PCIe, ecc.

Perché dovremmo usare questi die più avanzati in un approccio chip-on-board invece di progettare un substrato o un interposer? Ci sono diverse ragioni per questo, ed è difficile generalizzare per ogni situazione. Le schede per veicoli di test, la sperimentazione di interconnessioni tra chip e la semplice mancanza di accesso alla capacità produttiva di substrato/interposer sono tutti motivi per utilizzare il packaging chip-on-board.

Per assicurarti di raggiungere gli obiettivi di prestazione con design chip-on-board più avanzati, sfrutta queste risorse:

- Utilizza un calcolatore dell'impedenza delle vie per qualsiasi fanout delle vie dal die

- Assicurati di conoscere l'impedenza e usa un calcolatore di impedenza basato sulle equazioni di Wadell

- Consulta il tuo fabbricante e determina i limiti di dimensionamento delle vie o la necessità di foratura laser

- Per eliminare la necessità di caratteristiche più fini sullo strato superficiale, usa un laminato a basso Dk per supportare il die

- Assicurati di applicare un adeguato rivestimento superficiale che accomodi la saldatura dei fili

Se stai iniziando a progettare imballaggi chip-on-board e layout PCB, assicurati di utilizzare il set completo di strumenti di progettazione di prodotto in Altium Designer®. Quando hai terminato il tuo progetto e vuoi rilasciare i file al tuo produttore, la piattaforma Altium 365™ rende facile collaborare e condividere i tuoi progetti. Dai un'occhiata agli aggiornamenti mensili delle funzionalità in Altium Designer.

Abbiamo appena iniziato a scoprire cosa è possibile con Altium Designer su Altium 365. Richiedi una prova gratuita per testare in prima persona l'offerta Altium o segui uno dei webinar on-demand.