Progettazione del Power Delivery System (PDS)

In quest'articolo, parleremo delle nuove sfide legate alla progettazione del Power Delivery System (PDS) e forniremo alcune indicazioni utili per ottimizzare la sua progettazione in funzione delle esigenze tecnologiche attuali.

Lo sviluppo della tecnologia dei circuiti integrati ha consentito il posizionamento di miliardi di transistor su un singolo IC, portando alla creazione di sistemi estremamente potenti su un unico chip. Supercomputer che in passato occupavano stanze intere oggi possono essere contenuti all'interno di console, telefoni cellulari e in una miriade di altri prodotti di uso comune. Questa stessa tecnologia IC ha permesso la creazione di segnali d'uscita nella gamma multi-gigahertz, una volta possibile solo con circuiti a microonde estremamente costosi. Ma tutta questa tecnologia deve essere supportata da una solida progettazione del Power Delivery System, o PDS design.

Questo incredibile avanzamento tecnologico ha portato con sé una serie di sfide e conseguenze che andranno inevitabilmente affrontate. Questi circuiti integrati molto grandi spesso necessitano di diverse tensioni operative, la maggior parte delle quali non è di molto superiore a 1 volt, con correnti che possono superare i cento ampere. Inoltre, e lo vedremo meglio in seguito, le frequenze richieste dalle piste di alimentazione possono salire fino a un gigahertz. Soddisfare tutti questi requisiti è un compito difficile, che sta costringendo i progettisti ad acquisire competenze ingegneristiche molto più avanzate di quelle precedentemente richieste. Sfortunatamente, le tecniche attualmente disponibili nelle note applicative non offrono sufficiente supporto. In quest'articolo, parleremo delle nuove sfide legate al PDS design e forniremo alcune indicazioni utili per l'ottimizzazione della sua progettazione in funzione delle esigenze tecnologiche attuali.

L’alimentazione ideale

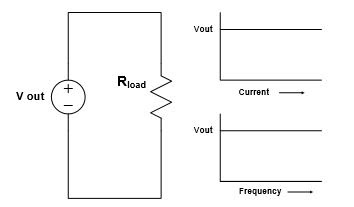

La Figura 5.1 mostra un alimentatore ideale, anche noto come sorgente di tensione. Le sorgenti di tensione del PDS hanno un'impedenza di uscita zero in modo che, indipendentemente dalla quantità di carico (corrente) richiesta dall'alimentatore, la tensione di uscita rimanga costante. Questo vuol dire il meno possibile tra la presa d'alimentazione USB e il punto di assorbimento. Inoltre, indipendentemente dalla frequenza di corrente richiesta, la tensione di uscita rimane costante. Sfortunatamente, gli alimentatori reali non sono così. L'impedenza di uscita non è mai zero, né in DC, né alle frequenze richieste dalla logica moderna.

Figura 5.1 Un alimentatore ideale

L’alimentazione reale

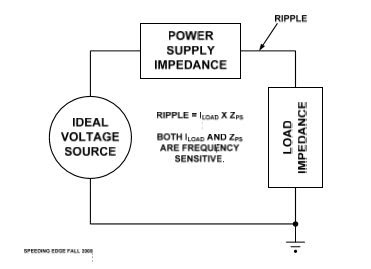

La Figura 5.2 mostra un alimentatore reale. Come si può vedere, è presente un'impedenza di uscita in serie alla sorgente di tensione. Questo diagramma illustra uno dei problemi principali nella progettazione del PDS.

L'impedenza d'uscita dell'alimentazione varia con la frequenza, determinando impedenze elevate ad alcune frequenze e basse ad altre. Laddove l'impedenza di uscita è elevata, le variazioni dell’assorbimento di corrente comportano variazioni della tensione di uscita. Questo fenomeno è noto come ripple. L'obiettivo del progettista è quello di progettare un PDS che abbia un'impedenza d'uscita bassa a ogni frequenza e i cui carichi richiedano corrente per ridurre al minimo il ripple.

Figura 5.2 Alimentatore reale

Che cos'è il ripple?

Il ripple, o ondulazione residua, è una variazione di tensione sulla pista di alimentazione di un alimentatore. Il ripple è il risultato delle variazioni della corrente di carico che sviluppano una caduta di tensione attraverso l'impedenza d'uscita dell'alimentazione, riducendo così la tensione di alimentazione vista dal carico. Un'ondulazione eccessiva può causare il malfunzionamento del sistema, rendendo la tensione Vdd troppo bassa per il corretto funzionamento del circuito che alimenta.

È stato dimostrato come un ripple eccessivo sia la fonte primaria di interferenze elettromagnetiche, EMI, nella maggior parte dei sistemi. Si accoppia infatti direttamente sulle linee di segnale sbrogliate sui piani Vdd di un PCB. (Questo dà origine a una delle regole empiriche secondo cui i segnali "critici" devono essere sbrogliati solo sui piani di massa). L'eccesso di ripple è spesso il motivo per cui si utilizzano solo alimentatori lineari per l'alimentazione del SERDES (serializzatore/deserializzatore) nei collegamenti ad alta velocità.

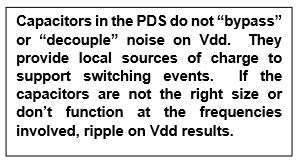

C'è spesso confusione sull’origine del ripple. Non è un "rumore" proveniente da una fonte misteriosa che deve essere "bypassato" o "disaccoppiato." La presenza di ripple su una pista di tensione è un segnale che l'impedenza del PDS è troppo alta alle frequenze contenute nel ripple. La soluzione è quindi quella di riprogettare il PDS per ridurre l'impedenza a quelle frequenze. Il metodo più comune per ridurre l'impedenza del PDS consiste nell'aggiungere condensatori di "disaccoppiamento", che, come già spiegato, non hanno il compito di disaccoppiare nulla in realtà. Stanno invece fornendo una fonte locale di potenza per supportare un evento di commutazione. Anche noti con il termine inglese "Coulomb buckets" poiché memorizzano i coulomb di carica utilizzati per supportare gli eventi di commutazione. Una volta chiarito questo punto, il compito degli ingegneri è di capire quanti coulomb e a quali frequenze siano necessari nel PDS.

Ripple sulla Vdd

Condensatori o coulomb buckets

A tutti i progettisti è capitato di dover posizionare condensatori attorno a componenti logici e analogici. Nella maggior parte dei casi, le istruzioni riguardo al loro numero e al loro posizionamento sono state tratte dalle note applicative. È raro, se non impossibile, che queste note siano pensate per garantire che vengano utilizzati il giusto tipo e numero di condensatori, e il loro preciso posizionamento.

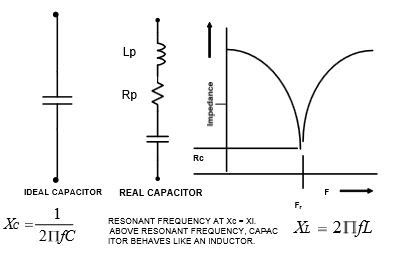

È importante ricordare che i condensatori hanno due parassiti che limitano la loro capacità di fornire carica agli eventi di commutazione su un PCB. La Figura 5.3 mostra il diagramma di un condensatore ideale, un condensatore reale e l'impedenza rispetto alla frequenza del condensatore reale. È bene notare come il condensatore reale abbia un'induttanza (Lp) e una resistenza (RP) collegata in serie. Questi sono parassiti indesiderati ma inevitabili che fanno parte di ogni condensatore, non importa quanto piccolo.

Nella parte inferiore della Figura 5.3 sono mostrate due equazioni. Consentono il calcolo dell'impedenza di L e C in funzione della frequenza. Si noti come. a DC o f = 0, l'impedenza del condensatore sia infinita e non visibile ai carichi PDS. Si noti come, a DC o f = 0, l'impedenza dell'induttore sia zero e non visibile ai carichi PDS. Quando f aumenta, Xc diminuisce e XL aumenta. Ad una e una sola frequenza, Fr, queste due impedenze sono uguali e si annullano a vicenda. L'impedenza vista dai carichi del PDS è la resistenza parassita R; è a questa frequenza che il Coulomb bucket è particolarmente utile nel PDS.

Al di sotto di Fr, il condensatore diventa impedenza elevata e non può fornire energia a un carico. Molto al di sopra di Fr, il condensatore inizia a comportarsi come un induttore in parallelo con la capacità del piano PCB, formando un circuito risonante parallelo. Questo può creare un'impedenza elevata che si traduce in tensioni di ripple molto elevate alla frequenza di risonanza del circuito parallelo.

Figura 5.3 Condensatori ideali e reali

Impedenza e frequenza di un PDS a confronto

Quando si progetta un PDS, l'obiettivo è quello di creare una bassa impedenza su un'ampia gamma di frequenze. La Figura 5.4 mostra l'impedenza rispetto alla frequenza di un singolo condensatore da 0,1 uF, e di un singolo condensatore da 0,01 uF quando montato tra Vdd e Vss di una serie di piste di alimentazione. La curva blu corrisponde al profilo di impedenza del condensatore da 0,1 uF, la curva gialla è invece l'impedenza del condensatore da 0,01 uF, mentre la curva rossa corrisponde all'impedenza combinata di questi due condensatori.

La maggior parte delle note applicative invitano i progettisti a posizionare un certo numero di condensatori di questo tipo su ciascuna pista di alimentazione. La Figura 5.4 nostra come l'impedenza venga abbassata a 100 milliohm tra 6 MHz e 15 MHz. Su entrambi i lati di questo intervallo, l'impedenza aumenta però bruscamente. Si immagini un delta I di 1 ampere a 100 Mhz: il ripple a questa frequenza sarebbe di 500 millivolt. A frequenze superiori, la situazione peggiorerebbe ulteriormente.

Figura 5.4 Impedenza vs Frequenza di un Condensatore da 0,01 uF e un Condensatore da 0,1 uF su un PDS

Come dimensionare i carichi

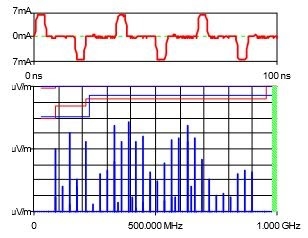

Una buona domanda da porsi è come dimensionare i carichi che il PDS deve supportare. Nella maggior parte dei sistemi basati su CMOS, le piste di trasmissione presentano la terminazione serie come mostrato nella Figura 1.7 nel Capitolo 1 di questo libro. La forma d'onda della tensione, quando un tale circuito passa da 1 a 0 e viceversa, è illustrata nella Figura 1.12. La corrente viene prelevata dal PDS per caricare la pista di trasmissione. Per determinare quali siano le frequenze in quella forma d'onda di corrente è necessario eseguire una trasformata di Fourier. La Figura 5.5 mostra la forma d'onda corrente in alto in rosso. L'escursione positiva è la corrente prelevata dal PDS per caricare la pista di trasmissione mentre passa da uno 0 logico ad un 1 logico. L'escursione negativa è la forma d'onda della corrente quando la carica viene rimossa dalla pista di trasmissione, mentre passa da un 1 logico a uno 0 logico.

La parte inferiore della Figura 5.5 mostra una trasformata di Fourier della forma d'onda della corrente che carica la pista di trasmissione da uno 0 logico a un 1 logico. Questo mostra le frequenze necessarie al PDS per creare una forma d'onda logica adeguata. In questo esempio, la linea di trasmissione è lunga 12 pollici (30 cm) e la frequenza di clock è di 30 MHz. Si noti come certi componenti di frequenza inizino intorno agli 80 MHz e arrivino fino a circa 900 MHz. Nessuno di questi sono armoniche del clock. La frequenza più alta è determinata dal tempo di salita del fronte di commutazione (1 nSec) e la frequenza più bassa è determinata dalla lunghezza della pista di trasmissione.

Figura 5.5 Trasformata di Fourier della Forma d'Onda di Corrente che Guida una Pista di Trasmissione con Terminazione Serie

Facendo riferimento alla figura 5.4, si può notare come la classica strategia di utilizzare condensatori da 0,1 uF, 0,01 uF consigliata da tante note applicative si occupi solo di frequenze fino a circa 30 MHz. Nessuno dei componenti di frequenza non è supportato dal PDS e appare come un rumore di ripple sulla pista di alimentazione. Questo rumore si accoppierà a qualsiasi segnale sbrogliato sul piano Vdd e può uscire dal PCB lungo i cavi di segnale. Questa è la fonte primaria di EMI in quasi tutti i sistemi che non riescono a limitare le frequenze elettromagnetiche. Questo stesso rumore appare su qualsiasi segnale logico che si trovi a un 1 logico, poiché il CMOS mette in corto le linee di segnale a Vdd quando su 1 logico.

Fonte primaria di EMI

Nel 1995 questo fatto è stato dimostrato dalla facoltà EMC dell'Università del Missouri, Rolla, ora conosciuta come Missouri University of Science and Technology. Per dimostrare il problema e la sua soluzione, è stato condotto uno studio per vedere cosa succede quando viene utilizzato l'approccio classico per aggirare il PDS. Il risultato di tale studio è allegato alle note al fondo di questo articolo. Questo studio dovrebbe interessare chiunque si trovi a progettare un PDS. La Figura 5.6 mostra il grafico dell'impedenza rispetto alla frequenza nel PCB di test utilizzato nello studio. Il PCB di test utilizzava un condensatore piano di circa 15 nF.

Sono presenti tre curve di impedenza rispetto alla frequenza nella Figura 5.6. La prima è l'impedenza del PCB nudo che mostra solo l'impedenza del condensatore piano. La seconda corrisponde all'impedenza della scheda con un condensatore da 0,1 uF e uno da 0,01 uF, mentre la terza è con un condensatore da 0,1 uF e quattro da 0,01 uF. Come prevedibile, quando viene testata solo la scheda nuda, l'impedenza è molto alta alle basse frequenze, poiché la dimensione del condensatore piano è contenuta. Quando si aggiungono due condensatori, come potrebbe accadere seguendo una nota applicativa, l'impedenza combinata è bassa dove il condensatore da 0,1 uF è risonante in serie (circa 13 MHz) e cresce all'aumentare della frequenza, scendendo nuovamente quando i condensatori da 0,01 uF diventano risonanti in serie (circa 45 MHz). Tra 50 MHz e 100 MHz, l'impedenza è peggiore che senza alcun condensatore. Questo fenomeno viene spesso chiamato "buco" d’impedenza. È il risultato dell'induttanza parassita del condensatore da 0,01uF e della induttanza di montaggio che insieme formano un circuito risonante in parallelo con il condensatore piano del PCB.

5.6 Impedenza PDS vs. Diagramma di Frequenza dello Studio UMR, per gentile concessione dell'IEEE

Una soluzione comune a questo problema consiste nell'aggiungere più condensatori. La terza curva rappresenta il risultato di questa soluzione aggiungendo 4 condensatori da 0,01 uF. L'unica differenza è che l'impedenza minore creata dai condensatori 0,01 uF è molto più bassa e si è leggermente alzata in frequenza, mentre il buco d'impedenza si è alzato in frequenza, ma è ancora presente. Più avanti in questo articolo discuteremo di come sia possibile eliminare questo "buco.” Si noti come al di sopra di circa 140 MHz, non vi sia alcun cambiamento.

A differenza del profilo di impedenza illustrato nella Figura 5.4, l'impedenza sopra i 100 MHz è relativamente bassa. Questo dipende dalla presenza di un condensatore piano. È questo condensatore che supporta le frequenze nella forma d'onda di commutazione superiore ai 100 MHz. Lo scopo dello studio UMR era quello di mostrare agli ingegneri EMI come il successo del contenimento delle interferenze elettromagnetiche dipendesse dalla progettazione di un buon condensatore piano su ciascuna pista che supporta le forme d'onda di commutazione.

La maggior parte dei processori moderni dispone di modalità standby e attiva per ridurre al minimo il consumo energetico quando l'attività è scarsa o assente. Questo è particolarmente importante per i prodotti alimentati a batteria come i telefoni cellulari. Quando questi processori passano dalla modalità standby a quella attiva, ne risulta un transitorio di corrente simile a quello mostrato nella Figura 5.5. La gestione di questi transitori viene attuata utilizzando le stesse tecniche utilizzate per la commutazione delle piste di trasmissione.

Condensatore piano

È stato dimostrato sopra, e in molte altre istanze, che un condensatore piano è necessario per il corretto funzionamento della maggior parte dei sistemi di erogazione di potenza. Questo si ottiene separando i piani Vdd e Vss con dielettrici molto sottili. La Figura 5.7 mostra un grafico della capacità per pollice quadrato di separazione tra i piani per una costante dielettrica 4, tipica della maggior parte dei laminati utilizzati per questo scopo. Sono due le curve tracciate, una rossa e una nera. La curva rossa è la capacità per pollice quadrato per i piani solidi, mentre la curva nera è la capacità per pollice quadrato dei piani con un'alta densità di fori, come accade nei dispositivi ad alta densità come i BGA.

Figura 5.7 Capacità per Pollice Quadrato di Due Piani Paralleli a Fungere da Separatori.

Determinazione della capacità del piano necessaria

Determinare quanta capacità del piano sia necessaria per una determinata pista di alimentazione è un'analisi complessa. A tal fine, gli ingegneri devono utilizzare uno degli strumenti elencati più avanti in questo capitolo. Questa analisi comporta una simulazione con un carico di corrente variabile e un condensatore piano variabile. Il carico viene spento e riacceso, mentre la quantità di ripple viene misurata all'aumentare della dimensione del condensatore piano. Una volta raggiunto il target di ripple, verrà di conseguenza stabilita la dimensione necessaria del condensatore piano. A questo punto, è possibile progettare lo stack-up PCB in modo da includere una capacità piana sufficiente per ciascuna pista di alimentazione.

La progettazione PDS precede lo stack-up del PCB

Aggiungere un condensatore piano

È chiaro come quasi tutte le piste di alimentazione nei moderni PCB richiedano l’utilizzo di condensatori piani per supportare i rapidi edge di commutazione dei segnali logici. Il problema è quindi come costruire questi condensatori piani. La Figura 3.9 nel Capitolo 3 mostra un PCB a 10 strati con due coppie di piani ravvicinati, Layer 3 e 4 e Layer 7 e 8. Questi sono separati da soli 3 mil (75 micron) per creare capacità tra i piani.

Cosa succede se lo stack-up normalmente utilizzato non ha coppie di layer a sufficienza per creare la capacità necessaria? Le soluzioni possibili sono due. La scelta più semplice è quella di aggiungere coppie di piani. Per una serie di motivi, questo potrebbe non essere possibile.

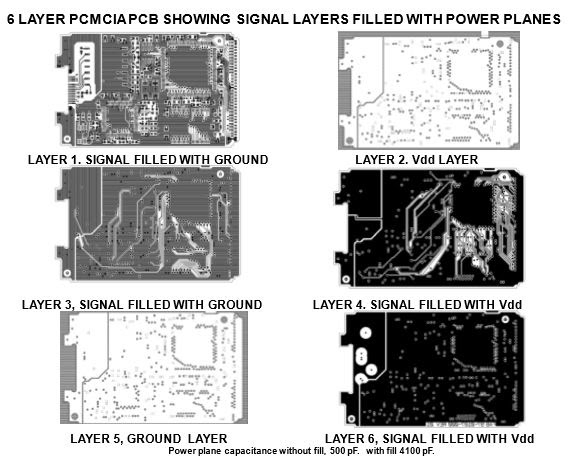

La Figura 5.8 illustra come questo problema sia stato risolto con un PCB PCMCIA a 6 layer che non poteva ospitare una coppia aggiuntiva di layer, sia per ragioni di costo che di spessore. Questo progetto ha fallito i test EMI ben sei volte. Ad ogni test, gli ingegneri hanno cambiato il numero di condensatori discreti sperando inutilmente di risolvere il problema. Il motivo per cui non ha funzionato è ben spiegato nello studio UMR sopra citato. Il problema EMI è scomparso creando una versione a 8 layer, aggiungendo due layer di alimentazione per creare un condensatore del piano di alimentazione. Questa soluzione ha però comportato due problemi: il PCB era ora troppo spesso per entrare nel suo involucro e il costo dei due layer aggiuntivi ha reso il prodotto non competitivo sul mercato.

Sui livelli 1, 3, 4 e 6 il rame è rappresentato in nero, mentre sugli strati 2 e 5, gli originali layer di massa e alimentazione, il rame è mostrato in bianco.

Ispezionando i quattro layer di segnale, 1, 3, 4 e 6, era chiaro come ci fosse un notevole spazio inutilizzato che poteva essere riempito con rame per creare capacità piana. La capacità piana prima del riempimento era di mezzo nanoFarad, mentre dopo era salita a quattro nanoFarad, sufficienti per risolvere il problema di interferenze elettromagnetiche.

La Figura 5.8 mostra lo stack-up di questo PCB PCMCIA prima e dopo il riempimento dei layer di segnale. Come si può osservare dalla figura, lo stack-up precedente aveva un solo condensatore piano con una separazione di 12 mil, mentre il successivo ha cinque condensatori piani con una separazione di 4 mil.

Figura 5.8 Una Scheda PCMCIA a 6 Layer che Illustra il Riempimento del Layer di Segnale per Aggiungere Condensatori Piani.

Figura 5.9 Stack-up del PCB a 6 Layer Prima e Dopo

Posizionamento dei condensatori

Sono tante le scuole di pensiero per quanto riguarda il posizionamento dei condensatori di bypass, noti anche come condensatori di disaccoppiamento. Per esempio:

- Il più vicino possibile a ciascun cavo di alimentazione

- Accanto a ciascun cavo di alimentazione

- Sotto il componente

- Utilizzare tracce per collegare il condensatore a ciascun cavo di alimentazione.

Nessuna di queste soluzioni sembra sufficientemente precisa. Ci deve pur essere un metodo accurato per determinare la posizione dei condensatori adatta per assicurare che svolgano correttamente il loro lavoro e, al contempo, rendere il layout e l'assemblaggio il più semplice possibile. Esiste in effetti un metodo ben definito, in uso ormai da molto tempo nelle aziende che progettano prodotti ad alte prestazioni. Resta comunque sottinteso come il condensatore piano sia un componente fondamentale di un PDS. Quando questo condensatore piano fa parte del PDS, l'induttanza della coppia di piani è notevolmente inferiore all'induttanza di montaggio di ciascun condensatore.

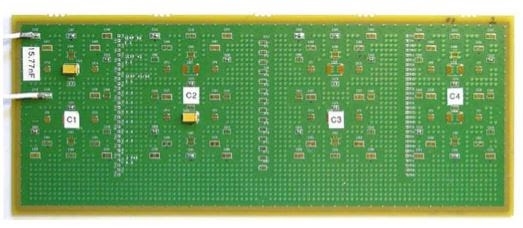

La Figura 5.10 mostra un PCB di prova con una capacità ben progettata. Questo PCB di prova è stato utilizzato per effettuare una varietà di misurazioni relative al comportamento dei condensatori. In questo esempio, la domanda posta è: se un IC fosse montato nell'angolo in alto a sinistra del PCB, potrebbe rilevare il montaggio di un condensatore su C1, C2, C3 o C4? Questo test determina il posizionamento ideale di ciascun condensatore per l’ottimizzazione delle prestazioni.

Figura 5.10 PCB di Prova Utilizzato per Valutare il Posizionamento dei Condensatori

La Figura 5.11 mostra l'impedenza misurata rispetto alla frequenza nei punti scelti per il posizionamento dei quattro condensatori. Si noti come le quattro curve siano virtualmente identiche, lasciando intendere come la posizione del condensatore abbia di fatto pochissimo effetto sulll'impedenza complessiva del PDS. La piccola differenza tra le curve è il risultato dell'induttanza di diffusione della coppia di piani quando il condensatore viene spostato più lontano dall'IC. Si noti che C1 è a circa ½ pollice (1,25 cm) dall'IC e C4 è a circa 9 pollici (23 cm)!

Figura 5.11 Impedenza vs Frequenza nei Punti Scelti per il Posizionamento dei Quattro Condensatori nella Figura 5.8

La conclusione che si deve trarre dai test di cui sopra è che la posizione dei condensatori di bypass, nei progetti PDS con un condensatore piano, è di minima rilevanza. Il consiglio è quindi quello di posizionare i condensatori in modo che non interferiscano con il layout, rendendo il montaggio il più semplice possibile. Tutte le note applicative che insistono nel concentrare i condensatori tra i fori di via sotto un BGA o "il più vicino possibile" rendono la progettazione e l'assemblaggio inutilmente difficili e costosi.

La Figura 5.12 mostra un esempio di PCB progettato con i condensatori di bypass posizionati in modo da non interferire con il layout.

Figura 5.12 Progettazione PCB con Condensatori Ben Posizionati

Consigli per i Condensatori di Bypass

Ridurre i "buchi" d'impedenza

Nella Figura 5.6 possono essere notati picchi d'impedenza in grado di degradare le prestazioni del PDS alle frequenze in cui si verificano. Questi sono difetti di progettazione da evitare. È stato dimostrato in quest'articolo come questi difetti siano il risultato di un circuito risonante parallelo formato dal condensatore piano e dall'induttanza parassita dei condensatori collegati al piano. La Figura 5.13 è un esempio di un circuito risonante in parallelo e la risultante curva dell'impedenza rispetto alla frequenza di questa combinazione.

Sia l'induttore che il condensatore hanno una certa resistenza parassita. Il termine RL si riferisce alla resistenza parassita del condensatore e quello RC alla resistenza parassita dei piani. La resistenza dei piani è in micro-ohm e non avrà molto effetto sul comportamento di questo circuito, mentre la resistenza parassita del condensatore avrà un effetto importante sui buchi di impedenza che possono comparire nei PDS.

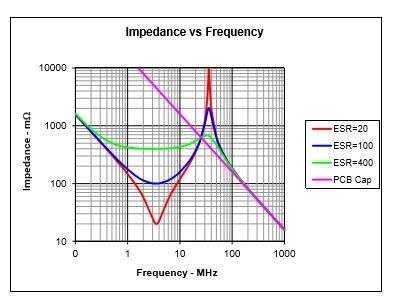

Alle basse frequenze, l'impedenza dell'induttore è molto bassa mentre l'impedenza del condensatore è molto alta. Ad una frequenza specifica, queste due impedenze saranno le stesse e agiranno in modo tale da produrre un'impedenza elevata. Gli ingegneri RF approfittano di questo comportamento per creare un circuito risonante che permette di selezionare una frequenza desiderata in una radio e rifiutare quelle vicine. Sfortunatamente, questo comportamento può degradare un PDS. È tuttavia disponibile una soluzione per ridurre al minimo questo problema. La Figura 5.14 mostra il grafico di un condensatore piano e un condensatore da 1 uF con tre diverse perdite o ESR (resistenza equivalente in serie).

Figura 5.13 Un Circuito Risonante Parallelo Creato da un Condensatore e un Induttore

Figura 5.14 Impedenza vs Frequenza del Condensatore Piano e dei Condensatori Discreti

Il grafico della Figura 5.14 contiene quattro curve. La curva viola rappresenta l'impedenza rispetto alla frequenza del condensatore piano preso singolarmente. La curva rossa rappresenta la combinazione di un condensatore da 1 uF con un ESR di 20 milliohm e il condensatore piano. La curva blu è invece la combinazione del condensatore da 1 uF con un ESR di 100 milliohm e il condensatore piano. La curva verde rappresenta infine la combinazione di un condensatore da 1 uF con un ESR di 400 milliohm e il condensatore piano.

Se l'impedenza desiderata per il PDS è di 20 milliohm, questa si ottiene a 3,5 MHz utilizzando solo un condensatore ESR di 20 milliohm. Il problema con questa soluzione è che a 35 MHz si crea un buco di impedenza di 10 ohm! Questo è disastroso in un PDS. Quando viene utilizzato un condensatore con più perdita (100 milliohm) si ottiene la curva blu. L'impedenza a 3,5 MHz è salita a circa 100 milliohm e il buco dell'impedenza è stato ridotto a due ohm, il che è meglio, ma non ancora soddisfacente.

La curva verde, utilizzando un condensatore con una ESR di 400 milliohm, ha finalmente eliminato il buco dell'impedenza. Nel processo, l'impedenza a 3,5 MHz è però salita a 400 milliohm. Se l'impedenza desiderata era di 20 milliohm, questo risultato non può essere considerato soddisfacente. Per tornare a 20 milliohm senza creare un buco di impedenza, è quindi necessario utilizzare 20 di questi condensatori con perdite in parallelo. Questo è esattamente il modo in cui gli ingegneri PDS determinano quanti condensatori di un dato valore siano necessari.

L'esperienza ha dimostrato che il miglior tipo di condensatori ceramici da utilizzare in un PDS sono quelli con dielettrici X5R o X7R. Questo è il dielettrico migliore per i condensatori utilizzati nei PDS.

Ridurre al minimo i buchi di impedenza

Induttori o perline di ferrite

Molte note applicative suggeriscono il posizionamento di perline di ferrite nei cavi di alimentazione dei dispositivi. La motivazione è che queste "bloccano" il rumore prima che questo possa entrare nei pin di alimentazione del dispositivo dal PDS. Questa è una scorciatoia che non risolve la vera causa del rumore, ovvero una progettazione scadente del PDS. È probabile che siano le note applicative stesse ad aver portato a una cattiva progettazione del PDS. All'inizio di questo articolo, è stato affermato come un buon PDS abbia un'impedenza molto bassa alle frequenze di funzionamento, mentre per bloccare efficacemente il rumore, la perlina di ferrite deve creare un'impedenza alta.

L'origine di questa regola empirica risale alla fine degli anni '80, quando alcuni dispositivi (dispositivi CMOS personalizzati) sono finalmente arrivati a commutare abbastanza velocemente da creare frequenze nella banda EMI. Gli esperti in EMI hanno iniziato a inserire perline di ferrite nei cavi di alimentazione di questi dispositivi, facendo scomparire le interferenze elettromagnetiche. Questo accadeva perché il dispositivo CMOS non aveva accesso al condensatore piano del PCB, e non poteva più commutare abbastanza velocemente da creare frequenze nella banda EMI.

Ma la tecnologia CMOS odierna ci consente di progettare PCB con SERDES (Serializzatore/Deserializzatore) che operano a velocità di 28 Gb/S e superiori. Queste parti hanno oggi bisogno di accedere ai condensatori piani del PCB per svolgere il loro lavoro. La Figura 5.15 è il diagramma ad occhio per l'output di un SERDES da 3,125 Gb/S. Il diagramma ad occhio a sinistra include una perlina di ferrite nel cavo Vdd del driver, mentre in quello a destra la perlina di ferrite è rimossa.

Figura 5.15 Diagramma ad Occhio di un SERDES da 3,125 Gb/S con Sfera di Ferrite (a Sinistra) e Senza (a Destra)

Non posizionare perline di ferrite nei cavi di alimentazione dei circuiti integrati

PCB senza condensatori piani

Esistono migliaia di prodotti realizzati su PCB a quattro layer con stack-up come quello mostrato nella Figura 5.16. La maggior parte delle schede madri e delle schede grafiche per PC sono progettate in questo modo. Hanno tutti segnali così veloci da aver bisogno di un condensatore piano per funzionare, eppure non ce n'è neanche uno in un PCB a quattro layer. Come è possibile che funzionino correttamente?

Potrebbe essere utile sottolineare perché i condensatori piani funzionino a frequenze più elevate rispetto ai condensatori discreti. Il motivo è che l'induttanza di una coppia di piani ravvicinati è nell'ordine dei femtohenry, mentre quella dei condensatori discreti meglio posizionati è raramente inferiore a 1 nanohenry.

Figura 5.16 Un Tipico Stack-up PCB a Quattro Layer Come Quello Usato in una Scheda Madre

Dividere i piani di massa

Ci sono "regole empiriche" che spingono i progettisti a dividere un piano di massa sotto un convertitore AD, o a "solcare" l'area intorno a un circuito analogico o un alimentatore di commutazione per impedire che le correnti nel piano di massa vadano a degradare le prestazioni dei circuiti nelle vicinanze. Non ci sono prove inconfutabili che esista un problema reale, o che dividere i piani di massa migliori effettivamente le prestazioni. È mia esperienza che seguire tali regole porti più spesso alla creazione di un nuovo problema, come l'EMI, piuttosto che alla sua soluzione.

Sono molte le pubblicazioni che parlano della gestione della massa in un PCB. Tutte sostengono che il modo più affidabile per collegare le masse dei componenti in un sistema sia attraverso un piano di massa continuo e ininterrotto. Il piano di massa è la struttura di induttanza e resistenza più bassa che ci sia in un PCB, a patto che non venga interrotta da tagli o solchi.

La nota numero 8 ai piedi dell'articolo include una spiegazione su come gestire la massa "A" e la massa "D" di un convertitore AD. È opera dell'ingegnere capo di Analog Devices e dimostra chiaramente come la creazione di due piani diversi non risolva alcun problema, creandone anzi di nuovi.

Non interrompere i piani di massa

Strumenti di PDS design

Esistono numerosi strumenti di progettazione specifici per la progettazione PDS. Si parte da strumenti basati su fogli di calcolo Excel che modellano tutti i condensatori e i piani del PCB in due dimensioni, fino a strumenti molto complessi capaci di modellare l'intero PCB e tutti i suoi carichi. Questi strumenti consentono al progettista di simulare eventi di commutazione effettivi, come il test di un condensatore di disaccoppiamento, per vedere quali profili di ripple e caduta di tensione avvengano quando i circuiti si accendono e si spengono.

Alcuni produttori di componenti hanno persino pubblicato strumenti appositi che i loro clienti possono utilizzare per progettare i PDS. Tra questi c'è Altera, che ha reso pubblico uno strumento scaricabile gratuitamente dal loro sito web. Questo strumento è Altera PDN_Tool V10; io stesso ho utilizzato questo strumento in decine di progetti con buoni risultati.

Riepilogo

La conversione dei più diffusi bus dati paralleli in coppie differenziali, e la capacità di produrre circuiti integrati con miliardi di transistor, ha portato a nuove sfide di progettazione. Si è gradualmente passati dal tentativo di sbrogliare migliaia di fili in spazi molto piccoli, senza troppa preoccupazione per l'integrità del segnale e per la progettazione del PDS, alla necessità di valutare come i materiali influiscano sulla qualità del segnale e di come lo stack-up PCB influisca sui PDS e sulle EMI.

In molti casi, la progettazione dei PDS va ben oltre il semplice routing dei segnali. Questo perché spesso ci sono molte tensioni diverse che devono rientrare in un numero limitato di layer. Questi necessitano quindi di sequenziamenti complessi, mentre le loro correnti sono spesso molto elevate con basse tensioni di esercizio. Fortunatamente però, sono stati sviluppati strumenti e tecniche per aiutare i progettisti nella progettazione.

BIBLIOGRAFIA

- Power Bus Decoupling on Multilayer Printed Circuit Boards” IEEE Transactions on Electromagnetic Compatibility, Vol. 37, NO 2, Maggio 1995.

- Smith, etal, “Power Distribution System Design Methodology and Capacitor Selection for Modern CMOS Technology” Pubblicato da Sun Microsystems, 1999.

- Hubing, Todd, etal, “PWB Power Structures: Theory and Design”, University of Missouri, Rolla, Novembre 1999.

- “Power Distribution Network Design Methodologies”, Istvan Novak, IEC Publications, 2008.

- Smith, Larry, etal, “On Die Capacitance Measurements in the Frequency and Time Domains,” DesignCon 2011.

- Smith, Larry, “PDN Currents,” Pubblicato su SI Reflector. Disponibile su Speeding Edge.

- Smith, Larry & Bogatin, Eric: “Principles of Power Integrity and PDB Design Simplified,” Prentice Hall, 2017. 8. Grounding A/D Converters‐ James Bryant, Analog Devices, EDN Pagina 42, Marzo 2006