Cos'è lo standard JESD204C per ADC/DAC?

Le interfacce seriali hanno avuto difficoltà a tenere il passo con le esigenze dei componenti convertitori di dati ad alta velocità di campionamento, in particolare gli ADC e i DAC. Un'opzione per farlo era in precedenza l'utilizzo di collegamenti LVDS tra i convertitori di dati e un controller host. Questi collegamenti fornivano alte velocità di trasmissione dati su coppie differenziali a un singolo dispositivo, offrendo un trasferimento di dati ad alta velocità da ADC a campionamento rapido. Successivamente, la JEDEC ha rilasciato la specifica JESD204, che da allora è stata incorporata in molti componenti come interfaccia per convertitori di dati.

L'iterazione più recente degli standard dell'interfaccia JESD204, attualmente JESD204C, porta velocità di dati estreme ai componenti ADC/DAC veloci che sono utilizzati per campionare segnali a velocità di campionamento molto elevate. Ora che la versione più recente dello standard è disponibile da poco più di 2 anni, ci sono molti componenti disponibili che possono essere utilizzati con gli FPGA per fornire campionamento ultra-veloce, trasmissione e DSP nei sistemi RF.

Panoramica di JESD204C

Lo standard JESD204C rappresenta l'ultima iterazione dello standard generale JESD204, che è pubblicato e mantenuto da JEDEC. Lo standard è stato sviluppato per sostituire l'uso di collegamenti LVDS tra i convertitori di dati e i loro sistemi ospitanti. Definisce un'interfaccia seriale e un protocollo utilizzati negli ADC/DAC ad alta frequenza di campionamento per il campionamento del segnale, la sintesi e la sincronizzazione. L'aspetto della sincronizzazione è importante per questa interfaccia poiché consente a un singolo controller host di sincronizzare il campionamento del segnale e la sintesi su più dispositivi.

Alcuni dei principali parametri operativi implementati nello strato fisico sono elencati nella tabella sottostante. L'attuale iterazione JESD204C migliora il tasso di dati e le caratteristiche di codifica della precedente iterazione JESD204B, che utilizzava la codifica 8b/10b con un tasso di dati massimo di 12,5 Gbps. Questa interfaccia può essere trovata in ADC/DAC che operano da 100 MSps a 1 GSps o più.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Esempio di Topologia

La topologia di un'interfaccia JESD204C dipende dalla Sottoclasse dell'interfaccia. JESD204B ha introdotto le Sottoclassi 1 e 2 per implementare una strategia di sincronizzazione nota come latenza deterministica. Questa strategia raggiunge la sincronizzazione tra dispositivi determinando lo sfasamento di fase tra i flussi di dati trasmessi al controller host.

- Sottoclasse 0 - Nessun supporto per la latenza deterministica (compatibile con JESD204A)

- Sottoclasse 1 - Latenza deterministica ottenuta utilizzando un oscillatore di riferimento esterno (SYSREF) come segnale di temporizzazioneSottoclasse 2 -

- Latenza deterministica ottenuta utilizzando un pin SYNC tra il controller host e l'ADC/DACDue implementazioni dell'interfaccia sono mostrate nella grafica sottostante.

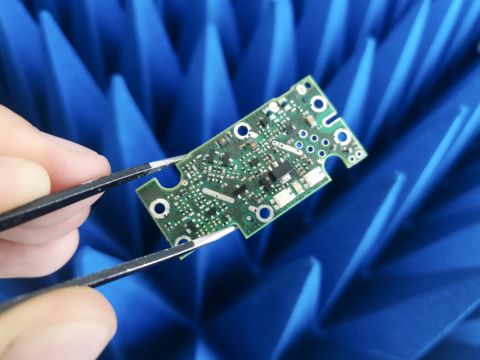

DATA1 e DATA2 sono instradati come coppie differenziali; ogni canale in questi gruppi di I/O è una coppia differenziale e un dato dispositivo potrebbe avere più canali (alcuni prodotti ne hanno fino a 8 per dispositivo). In entrambe le Sottoclassi, la fonte dell'orologio è instradata a tutti i dispositivi in modo sincrono con la sorgente. Il timing e la latenza deterministica sono raggiunti in ogni Sottoclasse tramite un appropriato abbinamento di SYSREF e DCLK/SYNC ai tempi di setup e di mantenimento, così come l'uno con l'altro quando distribuiti su più convertitori di dati.

Instradamento, Deskew e Latenza

La latenza deterministica è stata menzionata sopra: questa è la tecnica mediante la quale un singolo controller host può sincronizzare la raccolta e la sintesi dei dati su più dispositivi con un timing preciso in modo tale che lo skew temporale tra i frame di campionamento sia noto. Questo viene corretto accordando i ritardi delle tracce l'uno con l'altro in modo che i ritardi tra di loro siano abbinati. Un'interfaccia JESD204B o JESD204C utilizza l'abbinamento dei ritardi nei bit di controllo che provengono da SYSREF (nella Sottoclasse 1) o dai pin SYNC (nella Sottoclasse 2).

La tabella sottostante delinea i requisiti di abbinamento della lunghezza/ritardo nei segnali di timing per ogni Sottoclasse nelle interfacce JESD204B e JESD204C.

|

Sottoclasse 1 |

Sottoclasse 2 |

|

Ogni coppia DCLK + SYSREF abbinata ai tempi di setup e hold |

DCLK è utilizzato come orologio del dispositivo, nessun SYSREF per l'allineamento dei frame |

|

Le coppie DCLK e SYSREF sono abbinate l'una all'altra su tutti i dispositivi |

Le reti DCLK sono abbinate l'una all'altra su tutti i dispositivi |

|

SYNC attiva solo la sincronizzazione del gruppo di codici e non è critico per il timing |

SYNC instradato in topologia punto-punto per la sincronizzazione del gruppo di codici |

|

SYNC instradato in topologia bus |

Le reti SYNC non devono necessariamente essere abbinate l'una all'altra, ma devono rispettare i tempi di setup e hold di DCLK per ogni dispositivo |

La principale differenza qui è il trattamento delle reti SYNC. Nella Sottoclasse 1, queste reti sono utilizzate solo per la sincronizzazione del gruppo di codici, mentre nella Sottoclasse 2 sono utilizzate anche per il timing. Pertanto, JESD204C ha meno segnali per un dato numero di canali I/O nei convertitori di dati.

Perché JESD204C rispetto a LVDS?

Il vantaggio dell'interfaccia JESD204C per il campionamento ad alta velocità e la sintesi a frequenze GHz è questa capacità di eliminare lo skew e la discrepanza di latenza tra più convertitori. Esiste un certo budget di skew per qualsiasi interfaccia JESD204, che è la quantità massima di skew che può essere compensata nello schema di temporizzazione del sistema per garantire una latenza deterministica entro i limiti del rumore di fase. L'obiettivo è assicurare che il controller host conosca le discrepanze di fase dei flussi di dati in arrivo risultanti e possa compensarle in logica, stabilendo così il vero timing tra i segnali campionati.

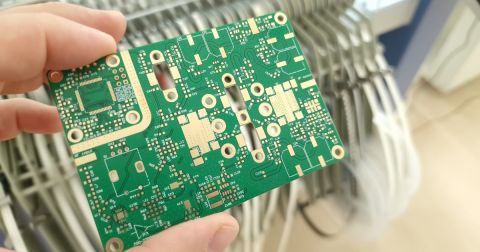

Un altro motivo per l'uso di JESD204C è che riduce i requisiti di routing e temporizzazione nel layout del PCB. In un'implementazione tipica, le coppie differenziali DATA1 e DATA2 provenienti dal Dispositivo 1 e dal Dispositivo 2 avranno una certa discrepanza tra loro. Con LVDS, ciò richiederebbe di abbinare coppie differenziali che corrono in parallelo l'una all'altra. In JESD204C, dobbiamo solo eliminare lo skew attraverso le reti DCLK e SYSREF/SYNC, ma non le reti dati tra i dispositivi. Questo rende l'interfaccia essenziale nei dispositivi misti ad alta densità.

I progettisti che sviluppano tecnologie avanzate per l'aerospaziale possono implementare lo standard JESD204C utilizzando i migliori strumenti di progettazione di prodotti del settore in Altium Designer®. Quando hai terminato il tuo progetto e vuoi inviare i file al tuo produttore, la piattaforma Altium 365™ semplifica la collaborazione e la condivisione dei tuoi progetti.

Abbiamo solo scalfito la superficie di ciò che è possibile fare con Altium Designer su Altium 365. Inizia oggi la tua prova gratuita di Altium Designer + Altium 365.