Projekt Pi.MX8 - Układ płyty Część 3

Rozdziały

Board Layout Part 3

| Created: June 24, 2024PCB Assembly

| Coming soonWitamy w nowej odsłonie projektu modułu komputerowego open-source Pi.MX8! W tej serii zagłębiamy się w projektowanie i testowanie modułu system-on-module opartego na procesorze i.MX8M plus od NXP.

W poprzedniej aktualizacji zakończyliśmy przygotowania układu. Obejmowało to tworzenie profili impedancji, dodawanie zasad projektowania zgodnie ze specyfikacjami producenta płyty oraz definiowanie obszarów, gdzie powinny obowiązywać specjalne zasady projektowania. Zakończyliśmy również trasowanie interfejsu LPDDR4, ale na razie bez dostosowywania długości.

Zanim zaczniemy dostosowywanie długości interfejsu DRAM, przyjrzymy się trasowaniu pozostałych interfejsów na module Pi.MX8. Na płycie znajduje się wiele magistral o wysokiej i niskiej prędkości, z których niektóre są szerokimi magistralami równoległymi, zajmującymi dużo miejsca na trasowaniu. Aby przydzielić wystarczająco dużo miejsca każdemu interfejsowi, najpierw utworzymy przybliżony plan rozmieszczenia dla każdej warstwy trasowania na module.

Planowanie trasowania

Plan trasowania pomoże nam określić, jak rozdzielić wszystkie interfejsy o wysokiej i niskiej prędkości między dostępne warstwy sygnałowe. Ustalając wstępne wytyczne, możemy upewnić się, że dysponujemy wystarczającą ilością miejsca do trasowania na warstwie, nad którą obecnie pracujemy. Pomaga to również zminimalizować przejścia między warstwami i redukować ilość poprawek do wykonania podczas procesu trasowania.

Istnieje kilka sposobów na przygotowanie planu układu, głównie zależnych od dostępnych narzędzi. Potrzebujemy tylko podstawowego narzędzia do rysowania, które pozwoli nam szkicować na istniejącym obrazie. W tym przykładzie użyjemy Inkscape.

W Inkscape możemy dodać obraz tła, który pokazuje rozmieszczenie komponentów i nieztrasowane interfejsy w formie kolorowych przewodów powietrznych. Zauważ, że sieci zasilające są ukryte na tym zrzucie ekranu, ponieważ skupimy się tylko na sieciach, które będą trasowane na warstwach sygnałowych. W schemacie umieściliśmy dyrektywę klasy sieci na każdej sieci zasilającej, co ułatwia identyfikację, które sieci są trasowane na warstwach płaszczyzn, poprzez po prostu włączenie lub ukrycie powiązanej klasy sieci w edytorze układu.

Do właściwego trasowania po prostu dodajemy linie w Inkscape, aby reprezentować interfejsy, które chcemy trasować na odpowiadającej im warstwie. Możemy dostosować szerokość tych linii, aby reprezentowały ilość sygnałów, które będą trasowane w interfejsie. Kolor linii można wybrać z obrazu tła, aby łatwiej było zidentyfikować, który interfejs jest reprezentowany.

Ponieważ przejścia między warstwami również wymagają przydzielonej przestrzeni na wszystkich warstwach, możemy dodać blok na końcu każdej linii szczegółowo opisujący przejście między warstwami.

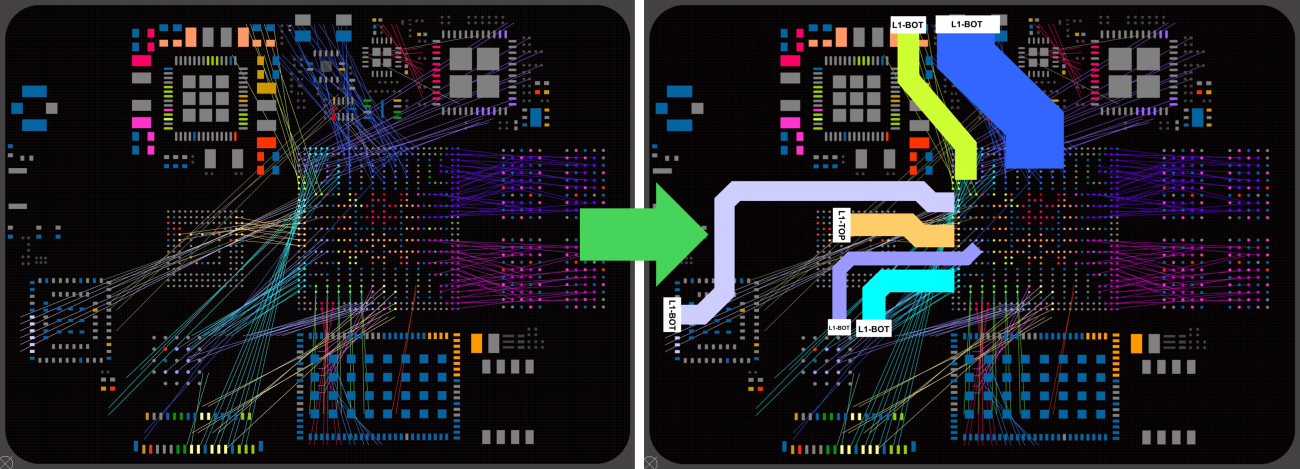

Planowanie układu w Inkscape z zrzutem ekranu Altium Designer jako obrazem tła

Gdy powtórzymy powyższy proces dla każdej warstwy trasowania, możemy przejść do właściwego procesu trasowania.

Trasowanie warstwy górnej

Mając strategię trasowania, zacznijmy od trasowania interfejsów na górnej warstwie. Ponieważ już wykonaliśmy trasowanie wyprowadzeń dla komponentów na górnej warstwie, możemy wykorzystać całą pozostałą przestrzeń na trasowanie sygnałów. Nie zostało wiele miejsca, ale to, co mamy, można nadal wykorzystać, aby ułatwić trasowanie na wewnętrznych warstwach sygnałowych poprzez strategiczne umieszczanie VIA w regionach, które nie będą kolidować z trasowaniem na wewnętrznych warstwach później. Jest to kolejna korzyść z planowania układu z góry, w przeciwnym razie te regiony nie byłyby zdefiniowane na tym etapie.

Trasowanie górnej warstwy modułu PiMX8

Umieszczając ścieżki na górnej warstwie, powinniśmy również wziąć pod uwagę, że potrzebujemy trochę miejsca na dodanie elementów takich jak fiducjale czy etykiety na górnej warstwie. Kody matrycowe wygrawerowane laserowo mogą również wymagać albo jednolitej powierzchni miedzianej, albo obszaru bez ścieżek, aby zapewnić jednolity kontrast, co oznacza, że te obszary nie mogą być wykorzystane do trasowania.

Trasowanie wewnętrznej warstwy sygnałowej

Większość połączeń zostanie umieszczona na dwóch wewnętrznych warstwach sygnałowych, które zdefiniowaliśmy w menedżerze stosu warstw. Zacznijmy od trasowania wszystkich szybkich interfejsów synchronicznych. W naszym przypadku mogą to być interfejsy MIPI-CSI, MIPI-DSI i LVDS. Wszystkie te interfejsy używają niskonapięciowego sygnału różnicowego i posiadają dedykowaną linię zegarową oraz co najmniej dwie linie danych. Wymagają one dużo miejsca do trasowania, ponieważ długość każdej linii danych musi być dopasowana do linii zegarowej w określonym marginesie czasowym. Dopasowanie długości wielu par różnicowych może wymagać dużo miejsca, ponieważ bardzo prawdopodobne jest, że jedna lub więcej par w interfejsie wprowadzi znaczące opóźnienie, które musi być uwzględnione. Trasując te interfejsy jako pierwsze, możemy upewnić się, że później będzie dostępna wystarczająca ilość miejsca na dostrojenie długości.

Umieszczanie VIA powrotnych ścieżek blisko przejść warstw tych szybkich par różnicowych jest również ważne, aby zapewnić integralność sygnału. VIA powrotne ścieżki mogą zajmować miejsce na wielu warstwach, więc te VIA należy umieścić tak szybko, jak tylko zostanie umieszczone przejście sygnału.

Następnie możemy poprowadzić inne interfejsy wysokiej prędkości takie jak PCIe, USB, HDMI i Ethernet. Te interfejsy mają mniej rygorystyczne wymagania dotyczące dopasowania długości między parami, więc nie musimy poświęcać tyle miejsca na dopasowanie długości. Zarządzanie solidną ścieżką powrotną oraz podstawowe podejścia do projektowania wysokich prędkości na tych sygnałach są nadal bardzo ważne, chociaż umieszczamy je na drugim miejscu listy priorytetów trasowania.

Na koniec możemy poprowadzić pozostałe interfejsy o niższej prędkości takie jak SDIO, GPIO, RGMII oraz inne różne magistrale takie jak UART czy I2C i SPI. Te interfejsy nadal działają z wysokimi prędkościami zboczy, co oznacza, że nadal musimy traktować je jako sygnały wysokiej prędkości.

Trasowanie wewnętrznej warstwy sygnałowej 1

Trasowanie wewnętrznej warstwy sygnałowej 2

Trasowanie dolnej warstwy

W przypadku płyty PiMX8 możemy traktować dolną warstwę jako wewnętrzną warstwę trasowania pod względem dostępnej przestrzeni. Większość aktywnych komponentów jest umieszczona na górnej warstwie modułu, pozostawiając tylko kilka regulatorów napięcia i pasywnych komponentów takich jak kondensatory odsprzęgające i rezystory konfiguracyjne na dolnej warstwie.

Priorytet trasowania na dolnej warstwie jest taki sam jak dla warstw wewnętrznych, więc zaczniemy od interfejsów MIPI-CSI, MIPI-DSI i LVDS. W module PiMX8 wysokoprędkościowy multiplekser może wybierać między portami DSI a LVDS. Ten komponent jest umieszczony na dolnej warstwie blisko złącza płyta-płyta. Ze względu na rozmieszczenie wyprowadzeń multipleksera, na jednej z linii sygnałowych połączonych z multiplekserem występuje znaczne opóźnienie. Będziemy musieli przyjrzeć się temu bliżej podczas procesu dopasowywania długości, ale musimy zarezerwować trochę miejsca na dolnej warstwie, aby umożliwić większe opóźnienie.

Rozmieszczenie wyprowadzeń multipleksera z jedną długą linią w interfejsie

Trasowanie dolnej warstwy modułu PiMX8

W module PiMX8 istnieje kilka scenariuszy, które wymagają szczególnej uwagi podczas strojenia opóźnień. Będziemy szeroko korzystać z sygnałów X, aby pokonać niektóre z tych wyzwań. Co dokładnie stanowią te wyzwania i jak możemy zaimplementować sygnały X, aby zapewnić precyzyjne strojenie opóźnień nad komponentem współdzielonym przez wiele interfejsów, będzie częścią następnej aktualizacji. Bądźcie na bieżąco!