O que é o padrão JESD204C para ADCs/DACs?

JESD204C oferece uma interface padronizada para ADCs de RF com alta taxa de amostragem, que agora estão aparecendo mais em aplicações espaciais comerciais.

As interfaces seriais têm enfrentado dificuldades em acompanhar as necessidades dos componentes conversores de dados de alta taxa de amostragem, nomeadamente ADCs e DACs. Uma opção para isso era anteriormente os links LVDS entre conversores de dados e um controlador host. Esses links forneceriam altas taxas de dados por pares diferenciais para um único dispositivo, oferecendo transferência de dados de alta capacidade de ADCs de amostragem rápida. Posteriormente, a JEDEC lançou a especificação JESD204, e desde então ela foi incorporada em muitos componentes como uma interface de conversor de dados.

A iteração mais recente dos padrões de interface JESD204, atualmente JESD204C, traz taxas de dados extremas para componentes ADC/DAC rápidos que são usados para amostrar sinais em taxas de amostragem muito altas. Agora que a iteração mais nova do padrão está presente há pouco mais de 2 anos, existem muitos componentes disponíveis que podem ser usados com FPGAs para fornecer amostragem ultra-rápida, transmissão e DSP em sistemas RF.

Visão Geral do JESD204C

O padrão JESD204C é a iteração mais recente do padrão geral JESD204, que é publicado e mantido pela JEDEC. O padrão foi desenvolvido para substituir o uso de links LVDS entre conversores de dados e seus sistemas hospedeiros. Ele define uma interface serial e protocolo usados em ADCs/DACs de alta taxa de amostragem para amostragem de sinal, síntese e sincronização. O aspecto da sincronização é importante para esta interface, pois permite que um único controlador hospedeiro sincronize a amostragem de sinal e a síntese em múltiplos dispositivos.

Alguns dos principais parâmetros operacionais implementados na camada física estão listados na tabela abaixo. A iteração atual JESD204C melhora a taxa de dados e as características de codificação da iteração anterior JESD204B, que usava codificação 8b/10b com taxa de dados máxima de 12,5 Gbps. Esta interface pode ser encontrada em ADCs/DACs que operam em qualquer lugar de 100 MSps a 1 GSps ou mais.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Exemplo de Topologia

A topologia de uma interface JESD204C depende da Subclasse da interface. JESD204B introduziu as Subclasses 1 e 2 para implementar uma estratégia de sincronização conhecida como latência determinística. Esta estratégia alcança a sincronização entre dispositivos determinando o descompasso de fase entre os fluxos de dados sendo transmitidos ao controlador host.

- Subclasse 0 - Sem suporte para latência determinística (compatível com JESD204A)

- Subclasse 1 - Latência determinística alcançada usando um oscilador de referência externo (SYSREF) como sinal de temporizaçãoSubclasse 2 - Latência determinística alcançada usando um pino SYNC entre o controlador host e o ADC/DAC

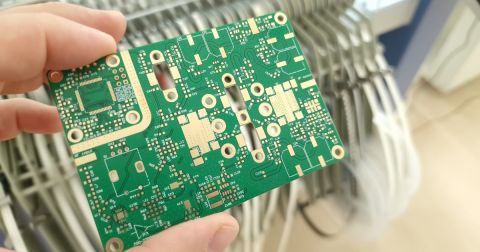

Duas implementações da interface são mostradas no gráfico abaixo.

DATA1 e DATA2 são roteados como pares diferenciais; cada via nesses grupos de E/S é um par diferencial e um dispositivo dado pode ter várias vias (alguns produtos têm até 8 por dispositivo). Em ambas as Subclasses, a fonte de relógio é roteada para todos os dispositivos de maneira síncrona à fonte. O tempo e a latência determinística são alcançados em cada Subclasse pelo pareamento apropriado de SYSREF e DCLK/SYNC com os tempos de configuração e retenção, bem como entre si quando distribuídos por vários conversores de dados.

Roteamento, Correção de Desvio e Latência

A latência determinística foi mencionada acima: esta é a técnica pela qual um único controlador host pode sincronizar a coleta e síntese de dados em vários dispositivos com temporização precisa de tal forma que o desvio de tempo entre os quadros de amostragem é conhecido. Isso é corrigido por ajustar os atrasos de traço entre si para que os atrasos entre eles sejam correspondidos. Uma interface JESD204B ou JESD204C usa correspondência de atraso nos bits de controle sendo originados de SYSREF (na Subclasse 1) ou dos pinos SYNC (na Subclasse 2).

A tabela abaixo delineia os requisitos de correspondência de comprimento/atraso nos sinais de temporização para cada Subclasse nas interfaces JESD204B e JESD204C.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A principal diferença aqui é como as redes SYNC são tratadas. Na Subclasse 1, essas redes são usadas apenas para sincronização do grupo de códigos, enquanto na Subclasse 2, elas também são usadas para tempo. Portanto, JESD204C tem menos sinais para um dado número de canais de I/O nos conversores de dados.

Por que JESD204C em vez de LVDS?

A vantagem da interface JESD204C para amostragem e síntese de alta velocidade em frequências de GHz é esta capacidade de eliminar o desvio de fase (skew) e a incompatibilidade de latência entre múltiplos conversores. Existe um orçamento de desvio de fase para qualquer interface JESD204, que é a quantidade máxima de desvio que pode ser compensada no esquema de temporização do sistema para garantir uma latência determinística dentro dos limites do ruído de fase. O objetivo é garantir que o controlador anfitrião conheça os desajustes de fase dos fluxos de dados de entrada resultantes e possa compensá-los em lógica, estabelecendo assim o verdadeiro temporização entre os sinais amostrados.

Outra razão para o uso do JESD204C é que ele reduz os requisitos de roteamento e temporização no layout da PCB. Em uma implementação típica, os pares diferenciais DATA1 e DATA2 vindos do Dispositivo 1 e Dispositivo 2 terão algum desvio entre eles. Com LVDS, isso exigiria que pares diferenciais correspondentes corressem em paralelo um ao outro. No JESD204C, só precisamos eliminar o desvio de fase entre as redes DCLK e SYSREF/SYNC, mas não as redes de dados entre dispositivos. Isso torna a interface essencial em dispositivos de sinal misto de alta densidade.

Designers que desenvolvem tecnologias avançadas para a área aeroespacial podem implementar o padrão JESD204C utilizando as melhores ferramentas de design de produtos da indústria no Altium Designer®. Quando você terminar seu design e quiser liberar os arquivos para o seu fabricante, a plataforma Altium 365™ facilita a colaboração e o compartilhamento dos seus projetos.

Apenas começamos a explorar o que é possível com o Altium Designer no Altium 365. Comece seu teste gratuito do Altium Designer + Altium 365 hoje.