Что такое стандарт JESD204C для АЦП/ЦАП?

JESD204C предоставляет стандартизированный интерфейс для РЧ АЦП с высокой частотой дискретизации, которые теперь все чаще появляются в коммерческих космических приложениях.

Серийные интерфейсы имели трудности с поддержанием темпа за потребностями компонентов преобразователей данных с высокой скоростью выборки, а именно АЦП и ЦАП. Одним из вариантов для этого ранее были связи LVDS между преобразователями данных и хост-контроллером. Эти связи обеспечивали высокие скорости передачи данных по дифференциальным парам к одному устройству, предлагая высокую пропускную способность передачи данных от АЦП с быстрой выборкой. Позже JEDEC выпустил спецификацию JESD204, и с тех пор она была включена во многие компоненты как интерфейс преобразователя данных.

Самая последняя итерация стандартов интерфейса JESD204, на данный момент JESD204C, предоставляет экстремальные скорости передачи данных компонентам быстрых АЦП/ЦАП, которые используются для выборки сигналов с очень высокой скоростью выборки. Теперь, когда новейшая итерация стандарта существует уже более 2 лет, имеется множество компонентов, которые могут использоваться с FPGA для обеспечения ультрабыстрой выборки, передачи и цифровой обработки сигналов в РЧ системах.

Обзор JESD204C

Стандарт JESD204C является новейшей версией общего стандарта JESD204, который публикуется и поддерживается JEDEC. Стандарт был разработан для замены использования связей LVDS между преобразователями данных и их системными хостами. Он определяет последовательный интерфейс и протокол, используемые в АЦП/ЦАП с высокой частотой выборки для семплирования сигналов, синтеза и синхронизации. Аспект синхронизации важен для этого интерфейса, поскольку он позволяет одному контроллеру хоста синхронизировать семплирование сигналов и синтез на нескольких устройствах.

Некоторые основные рабочие параметры, реализованные на физическом уровне, перечислены в таблице ниже. Текущая итерация JESD204C улучшает характеристики скорости передачи данных и кодирования предыдущей итерации JESD204B, которая использовала кодирование 8b/10b с максимальной скоростью передачи данных 12,5 Гбит/с. Этот интерфейс можно найти в АЦП/ЦАП, работающих в диапазоне от 100 Мвыб/с до 1 Гвыб/с или выше.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Пример топологии

Топология интерфейса JESD204C зависит от подкласса интерфейса. JESD204B ввел подклассы 1 и 2 для реализации стратегии синхронизации, известной как детерминированная задержка. Эта стратегия достигает синхронизации между устройствами, определяя разность фаз между потоками данных, передаваемыми контроллеру хоста.

- Подкласс 0 - Поддержка детерминированной задержки отсутствует (совместимо с JESD204A)

- Подкласс 1 - Детерминированная задержка достигается с использованием внешнего эталонного генератора (SYSREF) в качестве сигнала времени

- Подкласс 2 - Детерминированная задержка достигается с использованием вывода SYNC между контроллером хоста и АЦП/ЦАП

Две реализации интерфейса показаны на графике ниже.

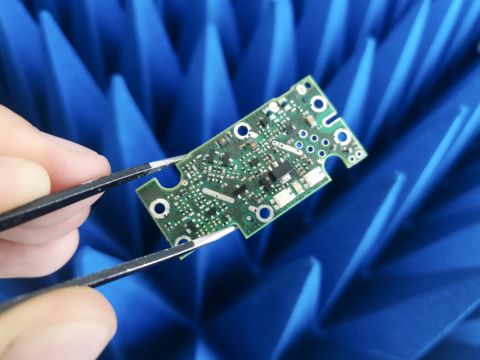

DATA1 и DATA2 маршрутизируются как дифференциальные пары; каждый канал в этих группах ввода/вывода является дифференциальной парой, и данный устройство может иметь несколько каналов (некоторые продукты имеют до 8 на устройство). В обоих подклассах источник тактового сигнала маршрутизируется ко всем устройствам синхронно с источником. Точное время и детерминированная задержка достигаются в каждом подклассе за счет соответствующего согласования SYSREF и DCLK/SYNC с временами установки и удержания, а также друг с другом при распределении по нескольким преобразователям данных.

Маршрутизация, Компенсация Сдвига и Задержка

Выше упоминалась детерминированная задержка: это техника, с помощью которой один контроллер хоста может синхронизировать сбор и синтез данных на нескольких устройствах с точным временем таким образом, что временной сдвиг между кадрами выборки известен. Это корректируется путем настройки задержек трасс относительно друг друга, так чтобы задержки между ними совпадали. Интерфейс JESD204B или JESD204C использует согласование задержек в управляющих битах, исходящих из SYSREF (в подклассе 1) или из контактов SYNC (в подклассе 2).

В таблице ниже приведены требования к согласованию длины/задержки в сигналах времени для каждого подкласса в интерфейсах JESD204B и JESD204C.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Основное отличие здесь заключается в обработке линий SYNC. В Подклассе 1 эти линии используются только для синхронизации групп кодов, в то время как в Подклассе 2 они также используются для времени. Таким образом, JESD204C имеет меньше сигналов для заданного числа каналов ввода/вывода в преобразователях данных.

Почему JESD204C вместо LVDS?

Преимущество интерфейса JESD204C для высокоскоростного семплирования и синтеза на частотах в ГГц заключается в возможности устранения сдвига и несоответствия задержек между несколькими преобразователями. Для любого интерфейса JESD204 существует некоторый бюджет сдвига, который является максимальным количеством сдвига, который может быть скомпенсирован в схеме тайминга системы для гарантии детерминированной задержки в пределах фазового шума. Цель состоит в том, чтобы обеспечить, чтобы хост-контроллер знал о фазовых несоответствиях результирующих входящих потоков данных и мог компенсировать это в логике, тем самым устанавливая истинное время между семплированными сигналами.

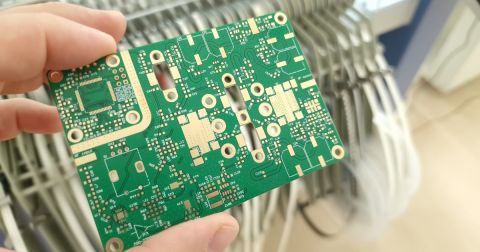

Другая причина использования JESD204C заключается в том, что это снижает требования к маршрутизации и таймингу в разводке печатной платы. В типичной реализации, дифференциальные пары DATA1 и DATA2, идущие от Устройства 1 и Устройства 2, будут иметь некоторый сдвиг между собой. С LVDS это потребовало бы согласования дифференциальных пар, идущих параллельно друг другу. В JESD204C нам нужно только устранить сдвиг через сети DCLK и SYSREF/SYNC, но не через сети данных между устройствами. Это делает интерфейс необходимым в высокоплотных смешанных сигнальных устройствах.

Дизайнеры, разрабатывающие передовые технологии для аэрокосмической отрасли, могут использовать стандарт JESD204C, применяя лучшие в отрасли инструменты проектирования продукции в Altium Designer®. Когда вы завершили свой проект и хотите отправить файлы вашему производителю, платформа Altium 365™ упрощает сотрудничество и обмен проектами.

Мы только начали раскрывать возможности Altium Designer на Altium 365. Начните свою бесплатную пробную версию Altium Designer + Altium 365 сегодня.