Cần Quy Định Gì cho Tính Toàn Vẹn Kênh Truyền: Các Danh Sách Kiểm Tra Thực Tế cho Các Liên Kết Tốc Độ Cao

Hầu hết các nhóm chỉ phát hiện vấn đề về tính toàn vẹn kênh khi bring-up: biểu đồ mắt trông sạch trong mô phỏng lại khép trên bàn đo, đầu nối được đánh giá đạt tốc độ dữ liệu yêu cầu nhưng lại thất bại trong topology thực tế, hoặc một thay đổi stackup làm lan truyền tổn thất margin mà không ai dự trù trong ngân sách. Mỗi trường hợp này đều là một lỗi đặc tả, nhưng biểu hiện ra ngoài dưới dạng lỗi signal integrity (SI). Cách khắc phục là xác định tính toàn vẹn kênh như một tập hợp các yêu cầu có thể đo lường được đủ sớm để tác động đến kiến trúc, rồi xác minh các yêu cầu đó xuyên suốt mọi giai đoạn của thiết kế.

Điểm chính cần nhớ

- Tính toàn vẹn kênh trước hết là một bài toán về yêu cầu. Margin được quyết định bởi topology, stackup và các lựa chọn liên kết/interconnect.

- Retimer, redriver, đầu nối và cáp đều tiêu tốn một phần ngân sách kênh của bạn. Hãy đặc tả chúng bằng các thông số IL, RL, xuyên nhiễu và jitter gắn trực tiếp với margin của liên kết.

- Kế hoạch đo kiểm là một phần của đặc tả kênh. Chiến lược fixture và de-embedding cần được xác định trước khi layout được chốt.

Thực chất tính toàn vẹn kênh bao gồm những gì

Một kênh tốc độ cao bao gồm toàn bộ đường dẫn điện từ chân phát đến chân thu, gồm breakout của package, via, chuyển tiếp giữa các mặt phẳng tham chiếu, trace, đầu nối, cáp và mọi khối điều hòa tín hiệu chủ động trên đường đi. Tính toàn vẹn kênh là khả năng của đường dẫn đó đáp ứng mục tiêu bit error rate (BER) trong các điều kiện điện áp, nhiệt độ, biến thiên quy trình và điều kiện interconnect thực tế. Topology, linh kiện và phương pháp xác thực của bạn đều phải đứng vững, và kết quả phải có tính lặp lại.

Mỗi phần tử trên đường dẫn đều tiêu tốn một phần ngân sách margin. Khi chỉ một phần tử bị đặc tả thiếu, vấn đề sẽ xuất hiện muộn và chu kỳ debug sẽ trở nên tốn kém. Trong bài viết này, chúng tôi trình bày quy trình tám bước để giúp bạn hiểu cần đặc tả gì, đặc tả như thế nào và cần yêu cầu gì từ nhà cung cấp linh kiện để kết quả mô phỏng và trong phòng lab hội tụ với nhau. Ngoài ra, chúng tôi cũng cung cấp các checklist thực tế cho từng bước trong quy trình.

Để xem kỹ hơn cách PCIe 7.0, 800G Ethernet, USB4 và Wi-Fi 7 đang đẩy các yêu cầu này lên các giai đoạn đầu của thiết kế, hãy xem Các chuẩn tốc độ cao liên tục nâng chuẩn.

Bước 1. Xác định đúng liên kết mà bạn thực sự đang xây dựng

Hãy bắt đầu bằng một khối định nghĩa liên kết ngắn gọn, được đưa vào cả tài liệu yêu cầu lẫn kế hoạch kiểm thử.

Checklist định nghĩa liên kết

- Chuẩn và mục tiêu tốc độ (ví dụ: PCIe, Ethernet, USB4 hoặc SerDes độc quyền).

- Số lane và kỳ vọng về lane bonding.

- Tầm với và topology. Chỉ trên bo, bo sang bo, dùng cáp hay flyover.

- Ngân sách độ trễ (đặc biệt nếu có thể thêm retimer).

- Ràng buộc công suất và nhiệt tại các vị trí điều hòa tín hiệu tiềm năng.

- Ràng buộc môi trường và cơ khí (rung động, khả năng tiếp cận để bảo trì).

Những quyết định này tạo thành baseline yêu cầu cho mọi lựa chọn ở các bước sau. Hãy chốt chúng sớm và giữ chúng trong kế hoạch kiểm thử.

Bước 2. Lập ngân sách trước khi bắt đầu layout

Ngân sách kênh là xương sống của đặc tả. Nó biến những kỳ vọng mơ hồ thành các con số cụ thể mà stackup, lựa chọn đầu nối và kế hoạch điều hòa tín hiệu của bạn thực sự có thể đáp ứng.

Các hạng mục cần có trong ngân sách

- Suy hao chèn (IL) theo tần số.

- Suy hao phản xạ (RL) theo tần số.

- Mục tiêu xuyên nhiễu: NEXT, FEXT và các chỉ số mixed-mode (nếu bạn sử dụng).

- Ngân sách skew: bao gồm đóng góp từ glass weave và đầu nối.

- Mục tiêu chuyển đổi mode vì năng lượng common-mode thường biểu hiện thành EMI.

- Các giả định về ngân sách jitter và mức độ bạn kỳ vọng equalization có thể phục hồi.

Nếu bạn không thể diễn đạt một yêu cầu dưới dạng một dòng ngân sách và một mặt phẳng tham chiếu, bạn sẽ không thể xác thực nó một cách rõ ràng.

Bước 3. Retimer: Cần đặc tả gì khi bạn cần CDR

Khi cần clock and data recovery (CDR), retimer cung cấp một điểm reset trong kênh. Nó phát lại một phiên bản sạch của tín hiệu, khôi phục margin mà chỉ equalization thôi không thể lấy lại được. Khả năng đó đi kèm với các ràng buộc thiết kế mà bạn cần đặc tả ngay từ đầu.

Checklist đặc tả retimer

- Tốc độ dữ liệu và giao thức được hỗ trợ.

- Số lane và mức độ linh hoạt trong ánh xạ lane.

- Độ trễ (điển hình và trường hợp xấu nhất).

- Khả năng chịu jitter và đặc tính truyền jitter (thiết bị lọc hoặc cho jitter đi qua như thế nào).

- Đặc tính và điều khiển equalization: preset tĩnh hay hành vi thích nghi; cách cấu hình và giám sát.

- Các trạng thái nguồn và đặc tính nhiệt.

- Yêu cầu về xung clock tham chiếu, nếu có.

- Yêu cầu đường tín hiệu: kỳ vọng về AC coupling, ràng buộc breakout package và hướng dẫn routing.

- Tính sẵn có của model: IBIS-AMI khi phù hợp, cùng với thiết kế tham chiếu và tài liệu đánh giá.

Retimer tiêu biểu

Broadcom BCM85667 là retimer PCIe Gen 6 và CXL 3.1, 16 lane, công nghệ 5 nm, hoạt động ở 64 GT/s PAM4. Tài liệu giới thiệu sản phẩm của nó nêu rõ các tốc độ dữ liệu được hỗ trợ, tùy chọn bifurcation, điều khiển EQ và khả năng tương thích footprint. Đó là mức độ chi tiết về đặc tả mà bạn nên kỳ vọng từ bất kỳ retimer nào được đưa vào đánh giá.

Bước 4. Redriver: Cần đặc tả gì khi bạn muốn EQ tuyến tính

Redriver cung cấp equalization tuyến tính và điều hòa đầu ra. Nó không thực hiện khôi phục clock. Sự đánh đổi này thường mang lại độ trễ thấp hơn và tích hợp đơn giản hơn, nhưng khả năng phục hồi một kênh bị suy giảm nghiêm trọng sẽ kém hơn.

Checklist đặc tả redriver

- Tốc độ dữ liệu và băng thông được hỗ trợ.

- Dải equalization và kích thước bước điều chỉnh.

- Dải biên độ đầu ra và điều khiển flat gain.

- Đặc tính nhiễu và tuyến tính, đặc biệt nếu có khả năng khuếch đại cả nhiễu cùng với tín hiệu.

- Độ nhạy đầu vào và khả năng xử lý common-mode.

- Giao diện cấu hình và telemetry.

- Ràng buộc package và breakout.

- Tính sẵn có của model và hướng dẫn layout tham chiếu.

Redriver tiêu biểu

PI3EQX32908ZRIEX của Diodes là redriver tuyến tính PCIe 5.0, 8 kênh, hỗ trợ 5 đến 32 Gbps với EQ theo từng kênh có thể lập trình, điều khiển biên độ đầu ra và flat gain; đồng thời cũng hỗ trợ các giao thức SAS4 và CXL.

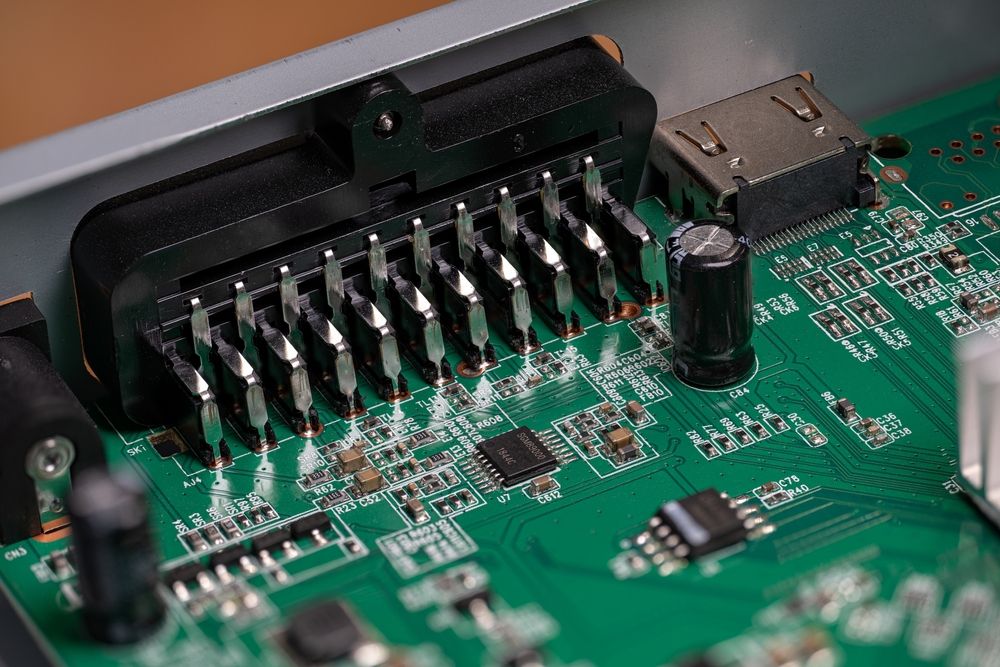

Bước 5. Đầu nối như một thành phần của kênh

Ở tốc độ cao, đầu nối và phần launch của nó có thể tiêu tốn một tỷ lệ margin lớn bất thường, vì vậy chúng xứng đáng được đặc tả nghiêm ngặt như bất kỳ thành phần kênh nào khác.

Checklist đặc tả đầu nối

- Mục tiêu trở kháng vi sai và dung sai.

- IL và RL theo tần số cho cặp đầu nối ghép mating và cho các launch trên PCB.

- Đặc tính xuyên nhiễu và hướng dẫn cách ly vùng chân pin.

- Các tùy chọn chiều cao stack và dung sai cộng dồn.

- Số chu kỳ cắm/rút và các giả định về độ bền cơ khí.

- Ràng buộc footprint PCB và breakout.

- Tính sẵn có của S-parameter và mọi hướng dẫn thiết kế tham chiếu.

- Kế hoạch second-source ở cấp giao diện.

Đầu nối tiêu biểu

Molex Mirror Mezz 202828-1506 là đầu nối mezzanine bo sang bo kiểu hermaphroditic với 404 mạch, chiều cao stack 2,50 mm và kiểu gắn BGA-attach, hỗ trợ tốc độ dữ liệu lên đến 56 Gbps trên mỗi cặp vi sai. Nó sử dụng footprint được OCP khuyến nghị và dùng chung trong dòng Mirror Mezz, nhờ đó bạn có dữ liệu S-parameter, tài liệu footprint và khả năng theo dõi qua nhà phân phối để gắn vào mô hình kênh và đánh giá BOM.

Bước 6. Cáp và flyover: Đặc tả phần mở rộng của kênh

Các cụm cáp đồng và flyover quang chủ động đều mở rộng tầm với của kênh vượt quá khả năng mà trace trên bo có thể cung cấp, nhưng chúng giải quyết các bài toán khác nhau. Cáp đồng hoạt động như đường truyền với các ràng buộc về trở kháng, che chắn và bán kính uốn. Flyover quang loại bỏ hoàn toàn suy hao điện môi nhưng lại đưa vào các yếu tố chuyển đổi điện-quang, công suất, nhiệt và độ trễ. Hãy đặc tả phương án mà ngân sách liên kết của bạn yêu cầu, đồng thời xác định rõ “hiệu năng tương đương” nghĩa là gì đối với mọi phương án thay thế mà bạn cân nhắc.

Checklist đặc tả cáp

- Trở kháng vi sai và skew.

- IL và RL theo tần số, bao gồm cả các chuyển tiếp ở mỗi đầu.

- Hiệu quả che chắn và phương án nối đất.

- Ràng buộc về bán kính uốn và chống kéo căng.

- Yêu cầu về số chu kỳ cắm/rút và khả năng tiếp cận để bảo trì.

- Đặc tính thụ động hay chủ động, nếu áp dụng. Với flyover quang, hãy đặc tả bước sóng, ngân sách công suất quang, độ trễ và mức tiêu thụ điện trên mỗi lane.

- Yêu cầu đánh giá/chứng nhận và danh sách cáp được phê duyệt.

Cụm flyover quang chủ động tiêu biểu

Samtec ECUO-B04-14-015-0-2-1-2-01 (FireFly ECUO) là cụm flyover quang chủ động có sẵn dưới dạng transceiver full-duplex 4 kênh ở 28 Gbps mỗi kênh, hoặc bộ phát hay bộ thu 12 kênh ở 16 Gbps mỗi kênh. Với sợi quang đa mode OM3, chúng có thể đạt tới 100 mét. Nó bỏ qua hoàn toàn suy hao trace trên PCB và sử dụng cùng hệ micro-connector như các cụm flyover đồng của Samtec, nên footprint vẫn giữ nguyên nếu bạn chuyển đổi giữa quang và đồng.

Bước 7. Vật liệu low-loss và đồng: Đưa stackup vào đặc tả

Các liên kết băng thông cao hơn đòi hỏi stackup phải là một đầu vào thiết kế được kiểm soát. Đặc tả kênh của bạn nên bao gồm các mục tiêu vật liệu và các khoảng chấp nhận được, đồng thời nêu rõ bạn đang giả định điều gì về độ nhám đồng và năng lực quy trình chế tạo.

Checklist đặc tả vật liệu và stackup

- Mục tiêu Dk và Df tại các tần số liên quan, cùng với mức biến thiên cho phép.

- Các giả định về biên dạng lá đồng khi suy hao dẫn là yếu tố giới hạn.

- Kiểm soát rủi ro glass weave và skew cho các đoạn chạy vi sai dài.

- Tg, Td và CTE theo trục Z nếu môi trường hoặc profile lắp ráp của bạn có yêu cầu khắt khe.

- Các giả định về năng lực của nhà chế tạo: tỷ lệ khía cạnh lỗ khoan, độ đăng ký, via fill và số chu kỳ ép lớp.

- Hãy chốt hệ laminate và yêu cầu xem xét rõ ràng trước mọi thay thế.

Laminate low-loss tiêu biểu

Panasonic’s MEGTRON 7 và I-Tera MT40 của Isola là những dòng vật liệu laminate tiêu biểu thuộc nhóm suy hao cực thấp và suy hao rất thấp, được sử dụng trong các kênh số tốc độ cao. Hãy dùng các sản phẩm này làm mốc tham chiếu cho những gì bạn mong muốn ở bất kỳ vật liệu laminate nào được chọn: dữ liệu điện ổn định, hướng dẫn quy trình rõ ràng và định danh sản phẩm minh bạch để bạn có thể chốt trong ghi chú chế tạo.

Bước 8. Kế hoạch đo lường: Lấy tương quan làm mục tiêu

Kế hoạch đo lường của bạn cần có các mặt phẳng tham chiếu, đồ gá, hiệu chuẩn và de-embedding được xác định rõ ràng, ताकि bạn có thể so sánh kết quả mô phỏng với dữ liệu đo thực tế mà không có sự mơ hồ. IEEE 370-2020 là một chuẩn tham chiếu thực tế cho công việc này, bao quát chất lượng dữ liệu, các yếu tố liên quan đến đồ gá và de-embedding cho đặc tính hóa PCB và liên kết đến 50 GHz.

Danh sách kiểm tra kế hoạch đo lường

- Bạn sẽ đo gì: TDR để lập biên dạng trở kháng, tham số S bằng VNA cho các đoạn liên kết, và eye diagram hoặc jitter tại các điểm xác định.

- Bạn sẽ đo ở đâu: Xác định các mặt phẳng tham chiếu và đặt tên cho chúng.

- Bạn sẽ hiệu chuẩn như thế nào: Nêu rõ phương pháp hiệu chuẩn và khả năng truy xuất nguồn gốc.

- Bạn sẽ de-embed như thế nào: Chọn các phương pháp mà bạn có thể thực hiện với đồ gá và công cụ hiện có.

- Bạn sẽ tương quan như thế nào: Xác định tiêu chí chấp nhận cho sự phù hợp giữa mô phỏng và phép đo.

Nền tảng đo lường nổi bật

Máy phân tích mạng Keysight PNA-X hỗ trợ các dải tần từ 900 Hz đến 67 GHz (tùy model), với nhiều nguồn nội bộ, bộ thu tham số S và nhiễu, đồng thời tương thích với phần mềm PLTS của Keysight để đặc tính hóa liên kết và de-embedding.

Octopart phù hợp ở đâu trong quy trình làm việc

Các linh kiện liên quan đến tính toàn vẹn kênh thường có ít lựa chọn thay thế thực sự hơn. Các dòng đầu nối, IC điều hòa tín hiệu chuyên dụng và một số cụm cáp nhất định có thể trở thành những linh kiện làm chậm tiến độ chế tạo. Hãy dùng Octopart và BOM Tool để giữ kết nối giữa ba yếu tố sau khi thiết kế vẫn còn linh hoạt:

- Mã linh kiện và trạng thái vòng đời được cập nhật.

- Tài liệu hỗ trợ: datasheet, mô hình và thiết kế tham chiếu.

- Sản phẩm thay thế và các lựa chọn nhà cung cấp trước khi footprint và giao diện được cố định.

Bạn càng sớm gắn dữ liệu linh kiện thực vào mô hình kênh, càng ít giả định bị kéo dài sang giai đoạn layout. Một file tham số S của đầu nối, tài liệu tóm tắt sản phẩm retimer hoặc bảng Dk/Df của laminate có giá trị hơn nhiều so với một placeholder và kế hoạch hoàn thiện sau. Octopart cho bạn một nơi thuận tiện để kiểm tra tình trạng sẵn có, lấy datasheet và xác nhận trạng thái vòng đời trong khi thiết kế vẫn còn đủ linh hoạt để hấp thụ những gì bạn tìm thấy.

Tính kỷ luật giúp tránh phải làm lại bo mạch

Tính toàn vẹn kênh được xây dựng thông qua một loạt quyết định bạn đưa ra trong giai đoạn kiến trúc, stackup và lựa chọn liên kết, sau đó được xác minh bằng mô phỏng, đo lường và tương quan trước và sau layout. Xuyên suốt toàn bộ quá trình, nguyên tắc vẫn như nhau: xác định điều bạn cần, đặc tả bằng các con số, chọn linh kiện có dữ liệu chứng minh cho các con số đó và viết kế hoạch đo lường trước khi layout bị khóa. Những nhóm thực hiện điều này một cách nhất quán chính là những nhóm tránh được vòng làm lại.