Hướng dẫn về Mạ Cạnh PCB trong Thiết kế RF

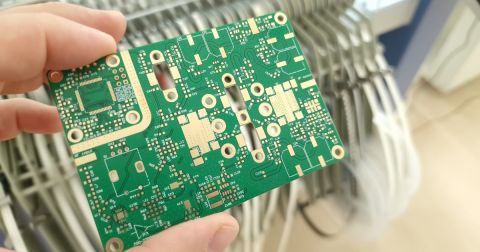

Một số thiết kế sử dụng việc mạ cạnh xung quanh bên ngoài của PCB, nơi mà các bức tường bên của lớp nền PCB được mạ bằng đồng. Lớp mạ đồng được sử dụng trong PCB RF được đặt cho nhiều mục đích, như cung cấp kết nối đất cho một vỏ bọc được bảo vệ hoặc chứa các trường điện từ. Nếu bạn xác định bạn cần bao gồm việc mạ cạnh, bạn nên chỉ định điều này trong bố cục PCB và dữ liệu sản xuất như thế nào?

Bài viết này sẽ cung cấp một cái nhìn tổng quan ngắn gọn về cách áp dụng mạ cạnh trong bố cục PCB của bạn, cũng như mạ cạnh sẽ trông như thế nào trong các sản phẩm giao hàng của bạn. Hãy chắc chắn bạn tuân theo các quy tắc thiết kế này để áp dụng thành công việc mạ cạnh trong bố cục PCB của bạn.

Quy Tắc Thiết Kế cho Mạ Cạnh

Quy Tắc DFM

Bộ quy tắc thiết kế quan trọng đầu tiên là các quy tắc DFM cho mạ cạnh. Mạ cạnh thường được áp dụng theo hai cách. Phương pháp đầu tiên áp dụng mạ cạnh như một cấu trúc đồng riêng biệt mà không kết nối với các lớp đồng khác trên PCB. Điều này có thể được thực hiện khi áp dụng một vòng bảo vệ xung quanh cạnh của PCB, thường được thực hiện khi áp dụng một chassis ground.

Hình ảnh dưới đây cho thấy khoảng cách gắn kết và khoảng trống điển hình cần được áp dụng giữa đổ đồng ở bên trong bảng mạch và lớp phủ cạnh. Lưu ý rằng lớp đổ định nghĩa lớp phủ cạnh mở rộng qua mép bảng mạch khoảng 0.5 mm; điều này có thể được phản ánh trong bố cục PCB với một quy tắc thiết kế (xem bên dưới).

Trong trường hợp trên, lớp phủ cạnh sẽ được áp dụng bằng cách gán nó vào mạng lưới riêng của nó. Nếu bạn đặt tên mạng lưới riêng cho vòng, bạn có thể tạo một quy tắc khoảng trống cụ thể cho mạng lưới đối với mép bảng mạch sẽ cho phép lớp đổ mở rộng qua đường viền bảng mạch. Bạn cũng có thể sử dụng quy tắc này để thiết lập khoảng trống cần thiết giữa lớp phủ cạnh và đồng không kết nối.

Lựa chọn khác là bao bọc hoàn toàn một lớp đổ đa giác quanh toàn bộ cạnh của PCB và quay trở lại lớp bề mặt kia. Trong trường hợp này, khoảng trống giống như trên lớp trên vẫn sẽ được áp dụng, giống như chúng ta đã có trong sắp xếp khác. Phương án trên thường không được sử dụng với một mặt đất khung máy, thay vào đó nó chỉ áp dụng cho một mặt đất hệ thống GND.

Trong Bố Cục PCB

Để áp dụng việc mạ cạnh vào bố trí PCB, lớp mạ cần được định nghĩa sử dụng đổ đa giác. Sau đó, đổ đa giác có thể được chạy đến mép của PCB. Thực hành thông thường trong phần mềm ECAD là mở rộng thêm lớp đồng qua mép của PCB. Khoảng cách mở rộng lớp mạ đồng qua mép có thể nhỏ, thường là khoảng cách 20 mil/0.5 mm được hiển thị trong các hình ảnh trên.

Để làm điều này trong Altium Designer, bạn có thể thiết lập một quy tắc Board Outline Clearance. Nếu bạn thiết lập khoảng cách là một giá trị âm, nó sẽ cho phép đổ đa giác ra ngoài mép bảng.

Nếu bạn có bất kỳ kết nối cắm nào ở mép trong bố trí PCB, hãy cẩn thận sau khi áp dụng việc mở rộng đa giác qua mép bảng. Đa giác có thể mở rộng xung quanh pad và sẽ tạo ra khả năng cho một mạch ngắn; điều này có thể được mong đợi ở vị trí gắn ở giữa cho một kết nối cắm SMA ở mép. Để ngăn chặn vấn đề này, sử dụng một khu vực cắt đa giác xung quanh pad để ngăn chặn việc mạ cạnh trong khu vực đó.

Quy trình trên được trình bày cho việc mạ cạnh, nhưng nó cũng áp dụng cho việc cắt lỗ trên khu vực nội thất của PCB. Một khi khu vực mạ được xác định và các quy tắc thiết kế được thiết lập, hãy loại bỏ lớp mặt nạ hàn dọc theo cạnh để khu vực đó có thể được truy cập để mạ. Điều này cũng đảm bảo rằng việc mạ có thể tiếp xúc với bất kỳ kim loại bên ngoài nào theo yêu cầu, chẳng hạn như trong một vỏ bọc được che chắn.

Dữ Liệu Sản Xuất

Sau khi bạn xuất các tệp sản xuất, đồng sẽ xuất hiện trên cạnh của lớp đường viền bảng mạch. Thông thường, một nhà sản xuất sẽ gửi cho bạn email để đặt câu hỏi và đảm bảo không có lỗi nào trong các tệp thiết kế của bạn. Để đảm bảo bạn có thể bắt đầu sản xuất nhanh chóng mà không gặp phải những câu hỏi thiết kế này, bạn nên chắc chắn rằng các yêu cầu xây dựng của mình được truyền đạt một cách chính xác.

Để làm điều này, hãy bao gồm một ghi chú trong bản vẽ sản xuất của bạn. Bạn nên bao gồm điều gì đó như sau:

- MẠ DỌC THEO CẠNH BẢNG MẠCH. ĐỘ DÀY HOÀN THIỆN CỦA LỚP MẠ CẠNH LÀ X MILS +/- Y MILS.

Cuối cùng, nếu bạn cần hoàn thành một biểu mẫu báo giá cho đơn hàng của mình, hãy chắc chắn rằng mạ cạnh được bao gồm trong biểu mẫu báo giá để không có sự mơ hồ nào về ý định thiết kế của bạn.

Bất cứ khi nào bạn cần đặt các cấu trúc đồng độc đáo trong bố cục PCB RF, bao gồm cả việc mạ cạnh, hãy sử dụng bộ công cụ thiết kế và sản xuất PCB đầy đủ trong Altium Designer®. Khi bạn đã hoàn thành bố cục PCB và bạn sẵn sàng chia sẻ các tài liệu sản xuất, bạn có thể dễ dàng chia sẻ dữ liệu và phát hành các tệp cho nhóm của mình với nền tảng Altium 365™.

Chúng ta mới chỉ khám phá bề mặt của những gì có thể thực hiện với Altium Designer trên Altium 365. Bắt đầu dùng thử miễn phí Altium Designer + Altium 365 ngay hôm nay.