Cách Thiết Kế Một Bias Tee Cho Bộ Khuếch Đại Công Suất

Bias tees được sử dụng trong một số hệ thống RF để tách điện AC và DC dọc theo một đường dây cụ thể. Tìm hiểu thêm về thiết kế bias tee trong bài viết này.

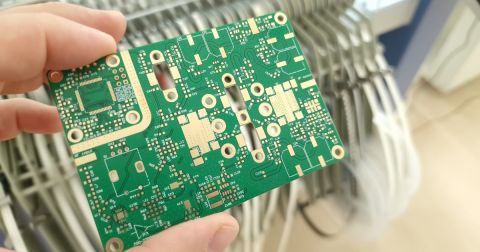

RF bias tees được sử dụng để tách biệt nguồn điện DC và AC dọc theo một kết nối. Đây là thiết bị 2 đầu vào, 1 đầu ra sử dụng các yếu tố phản ứng để cung cấp dòng điện theo các hướng khác nhau. Trong một dự án trước đây với bố trí khuếch đại công suất RF, có một bias tee trong thiết kế được sử dụng để cung cấp nguồn điện DC cho bộ khuếch đại đồng thời cho phép công suất RF truyền tới đầu ra của bộ kết nối SMA.

Trong bài viết này, tôi sẽ trình bày cách thiết kế mạch này và những thông số quan trọng để đảm bảo truyền tải công suất cao vào thành phần tải của bạn. Những thiết bị này có sẵn dưới dạng mô-đun công suất cao cho phát sóng tầm xa, nhưng chúng cũng có thể được xây dựng như các mạch nhỏ trên PCB cho các hệ thống RF công suất thấp.

Biểu Tee là gì?

Một bias tee là một mạch đơn giản sử dụng cuộn cảm và tụ điện để điều khiển dòng điện AC và DC. Loại bias tee đơn giản nhất là thiết bị 2 đầu vào; cuộn cảm được sử dụng để truyền điện DC từ một cổng đầu vào, và tụ điện được sử dụng để truyền điện AC đến cổng ra. Trong ví dụ trước với bộ khuếch đại công suất RF của chúng tôi, một bias tee đã được sử dụng để cung cấp điện cho bộ khuếch đại, đồng thời cũng truyền công suất đầu ra RF từ cùng một chân. Mạch đã được sử dụng trước đây được hiển thị dưới đây.

Khái niệm rất đơn giản; trở kháng cảm ứng của cuộn cảm chặn tín hiệu AC, trong khi tụ điện chặn tín hiệu DC không cho qua tải trong hệ thống này. Tín hiệu DC đơn giản là điện được cung cấp cho chân VDD, sẽ cấp điện cho bộ khuếch đại, và mạch nội bộ của bộ khuếch đại sẽ điều hướng công suất đầu vào theo cách cần thiết.

Tỷ lệ Trở kháng trong một Bias Tee Đơn giản

Bias tees được thiết kế sao cho chúng ta cố gắng đạt được tỷ lệ trở kháng cụ thể. Tỷ lệ trở kháng trong một bias tee đề cập đến tỷ lệ giữa trở kháng dọc theo đường dẫn DC và trở kháng mà tín hiệu nhìn thấy khi nó di chuyển dọc theo đường dẫn đầu ra. Tỷ lệ trở kháng này cần được bao gồm trong thiết kế của bias tee dưới các mục tiêu thiết kế sau:

Trở kháng nhìn vào cổng DC nên lớn hơn nhiều so với trở kháng nhìn vào đầu ra RF

Trở kháng tương đương giảm qua bias tee (đo từ RFOUT đến phía đầu ra của tụ điện) cần phải khớp với đường truyền tín hiệu LO_OUT

Vì vậy, chúng ta có hai định nghĩa quan trọng mà chúng ta có thể sử dụng để tính toán tỷ lệ trở kháng:

Các giá trị trong hai phương trình trên là điện kháng của cuộn cảm (L) và tụ điện (C) tại tần số hoạt động của mạch. Một giá trị điển hình cho tỷ lệ trở kháng có thể nằm trong khoảng từ n = 1 đến n = 1000. Trở kháng của bias tee Z(tee) sẽ được khớp với trở kháng đường truyền, thường là 50 Ohms trên PCB. Chúng ta có hai phương trình và hai ẩn số, vì vậy chúng ta có thể dễ dàng giải quyết cho các điện kháng này.

Các giá trị trên là giá trị tối thiểu cần thiết để hội tụ về một sự khớp trở kháng. Nếu chúng ta sử dụng định nghĩa về dung kháng và cảm kháng trong phương trình trên, chúng ta có mối quan hệ sau đây giữa tần số hoạt động mục tiêu và điện dung:

Mối quan hệ này cho chúng ta biết rằng chúng ta có thể dịch chuyển băng thông qua cho bias tee bằng cách điều chỉnh C cho một tỷ lệ trở kháng mục tiêu trong khi giữ giá trị cuộn cảm L không đổi. Chúng ta cũng có thể sử dụng cùng một mối quan hệ nhưng với L ở vế phải của phương trình thay vì C.

Ví dụ, nếu chúng ta lấy các giá trị trên và tăng điện dung lên một yếu tố N, tần số hoạt động mà chúng ta mong đợi sẽ thấy sự cung cấp công suất tối đa vào tải sẽ phải giảm đi một yếu tố √N để duy trì cùng một tỷ lệ trở kháng. Điều này có thể thay đổi sự khớp trở kháng ở đầu ra; mặc dù chúng ta có thể có một số phản xạ và không khớp trở kháng, bias tee đang dịch chuyển băng thông của mình sao cho công suất tải có thể được tăng lên.

Máy Tính Bias Tee LC

Bạn có thể sử dụng ứng dụng máy tính bên dưới để xác định các giá trị L và C để sử dụng trong một bias tee. Điều này đòi hỏi người thiết kế nhập vào tỷ lệ trở kháng mong muốn và trở kháng mục tiêu. Tần số được đưa ra ở đây là tần số dự kiến nơi chúng ta thấy giá trị cao nhất trong dải thông qua của bias tee.

Lọc Cấp Cao

Điều gì sẽ xảy ra nếu chúng ta đặt một bộ lọc phức tạp hơn ở phía DC? Việc đặt một mạch lọc cũng là khả thi. Giai đoạn DC được hiển thị ở trên có thể có một giai đoạn lọc phức tạp hơn giữa cổng nguồn vào và điểm nhánh trên mạng lưới đầu ra RF. Ví dụ, chúng ta có thể đặt một bộ lọc thông thấp hai chiều cấp cao hơn giữa cổng DC vào và điểm nhánh.

Điều này sẽ trông giống như mạch dưới đây. Ở đây, tôi đã đặt các mạch RL song song làm các phần tử lọc cơ bản giới hạn dòng điện ở tần số cao hơn đến từ nguồn cung cấp điện. Nếu bạn tìm kiếm trên internet, bạn sẽ thấy các ví dụ khác về mạch RLC được sử dụng như bộ lọc thông thấp dọc theo kết nối DC.

Trong mạch này, trở kháng của cuộn cảm + giai đoạn lọc RF được kích thước để đạt được tỷ lệ trở kháng cụ thể so với đường 50 Ohm và mục tiêu tỷ lệ trở kháng. Cũng thường thấy một tụ điện được nối từ cực VDD. Tại sao chúng ta muốn áp dụng cách tiếp cận này cho giai đoạn lọc? Có ba lý do có thể:

- Vì đây là bộ lọc cấp cao, sẽ có độ dốc lớn hơn ở các tần số cao

- Dựa trên điểm trước, phần bộ lọc có thể lọc nhiễu từ nguồn DC

- Điểm nối tee có thể có tỷ lệ trở kháng cao một cách nhất quán trên một dải thông qua rộng hơn

Trong ví dụ trên, một bộ lọc cấp cao đang được sử dụng trên cổng đầu vào DC. Thách thức chính với điều này là cấu trúc của bộ lọc chặn có thể có một số dao động dải thông qua như một chức năng của tần số, và kết quả là trở kháng của điểm nối tee cũng có thể có một số dao động dải thông qua. Do đó, việc mô phỏng hoạt động của phần bộ lọc là quan trọng, điều này có thể được thực hiện trong một mô phỏng SPICE.

Ví dụ: Mô phỏng SPICE Với LC Bias Tee

Trong phần này, tôi sẽ trình bày một số kết quả mô phỏng cho điểm nối bias LC đơn giản được hiển thị trong sơ đồ trên cho dự án mô-đun khuếch đại công suất của chúng tôi. Như đã được thiết kế ban đầu, điểm nối bias được hiển thị ở trên sẽ hoạt động như dự định với hoạt động băng thông rộng, và việc khớp trở kháng sẽ gần như chính xác là 50 Ohm. Tuy nhiên, nó không được tối ưu hóa cho việc cung cấp công suất cho tải 50 Ohm do hành động lọc của điểm nối bias do tỷ lệ trở kháng cao.

Sơ đồ dưới đây cho thấy mạch ban đầu sẽ được sử dụng để mô phỏng bias tee.

Trong mô phỏng này, chúng ta sẽ xem xét một mô phỏng AC cho tee, nơi chúng ta quan tâm đến điện áp đầu ra, dòng điện vào phía RF, và công suất cung cấp cho RLOAD. Chúng ta cũng muốn biết trở kháng nhìn qua đầu vào RF là bao nhiêu. Lý tưởng nhất, điều này nên gần với 50 Ohm càng tốt. Kết quả AC ban đầu được hiển thị dưới đây.

Mô phỏng ban đầu này tiết lộ một số kết quả khá tốt. Băng thông qua là rất rộng cho bias tee này, và việc khớp trở kháng xuất hiện cực kỳ chính xác ngay đến tần số hoạt động của mạch là 6.3 GHz. Mặc dù trở kháng mục tiêu dường như đã được đạt tới, chúng ta không thấy việc cung cấp công suất tối đa cho tải ở tần số mong muốn. Điều này là do 6.3 GHz nằm trong phần giảm của băng thông.

Giả sử bây giờ chúng ta đặt tỷ lệ trở kháng là 1:1 cho mạch này. Điều này sẽ yêu cầu một cuộn cảm 1.2 nH và tụ điện 0.5 pF. Kết quả với cấu hình mô phỏng cập nhật này được hiển thị dưới đây.

Từ đây, chúng ta thấy rằng băng thông đã chuyển lên các tần số cao hơn, nhưng không nhất thiết chúng ta nhận được nhiều công suất hơn từ tee được cung cấp cho RLOAD. Chúng ta cũng thấy rằng trở kháng không hội tụ với mục tiêu cho đến một tần số cao hơn nhiều (khoảng 10 GHz). Vì vậy, chúng ta vẫn chưa đạt được một thiết kế hoàn hảo.

Cuối cùng, hãy xem điều gì xảy ra nếu chúng ta tăng các tham số lên L = 6 nH và C = 1 pF (tương đương với tỷ lệ trở kháng 3.14 tại khoảng 6.45 GHz). Trong trường hợp này, chúng ta nhận được sự khớp nối tốt hơn nhiều với trở kháng mục tiêu, mặc dù công suất cung cấp cho tải có phần thấp hơn. Mặc dù băng thông đã chuyển lên cao hơn nhiều, trở kháng mà mạch này nhắm đến tại 6.45 GHz là khoảng 77.4 Ohm, có thể giải thích việc cung cấp công suất thấp hơn trong mạch này.

Một quét tham số có thể giúp xác định sự cân bằng tốt nhất giữa L và C trong một phạm vi nào đó. Mô phỏng khác mà chúng ta có thể thực hiện là mô phỏng phân tích chuyển tiếp. Điều này sẽ cho chúng ta biết điều gì xảy ra với tee khi mạch ban đầu được đưa lên công suất hoạt động của nó. Hãy thử làm điều này bởi vì nó khá đơn giản, và nó sẽ minh họa những rủi ro tiềm ẩn khi sử dụng bộ lọc bậc cao trên phía DC của mạch.

Có điều gì không ổn với bức tranh này không? Hóa ra là có! Cụ thể, có hai điểm không được xem xét trong mô phỏng này:

- Ở tần số GHz, nơi hệ thống này hoạt động, tụ điện và cuộn cảm có thể có một số linh kiện phụ (ESR/ESL trên tụ điện và EPC trên cuộn cảm)

- Bộ chia bias hỗ trợ sự lan truyền sóng, vì vậy các kết nối giữa các linh kiện thực sự là đường truyền.

Dựa vào điểm #2, và ý tưởng rằng tín hiệu ra từ một bộ khuếch đại có thể được kết thúc nội bộ với 50 Ohm, trở kháng của bộ chia bias đôi khi được đặt rất thấp. Điều này có thể được chấp nhận miễn là bộ chia được đặt rất gần với chân ra trên bộ khuếch đại công suất. Tuy nhiên, việc sử dụng khớp trở kháng xuyên suốt kết nối để cố gắng tối đa hóa việc truyền tải công suất vào tải là ưu tiên hơn nhiều.

Các mô phỏng SPICE không giỏi lắm trong việc mô phỏng sự truyền dẫn trên các đường truyền giữa các thành phần và ra khỏi bộ chia bias. Do đó, mô phỏng SPICE được hiển thị ở trên sử dụng một tải 50 Ohm để đại diện cho trở kháng đầu vào khi nhìn vào tải trong ví dụ mô-đun khuếch đại công suất của chúng tôi. Nếu chúng ta có tình huống mà tải được đặt gần với đầu ra của bộ chia bias, thì chúng ta chắc chắn có thể áp dụng cách tiếp cận mạch được lý tưởng hóa trong ví dụ mô phỏng SPICE được hiển thị ở đây.

Sau khi bạn chọn các thành phần cho bộ chia bias của mình, hãy chắc chắn bạn sử dụng bộ công cụ thiết kế PCB đầy đủ trong Altium Designer® để thiết kế bảng mạch của bạn. Altium Designer là nền tảng CAD hàng đầu của ngành cũng bao gồm một trình mô phỏng SPICE dễ sử dụng ngay trong trình chỉnh sửa sơ đồ. Khi bạn hoàn thành thiết kế và muốn gửi các tệp cho nhà sản xuất của mình, nền tảng Altium 365™ giúp việc hợp tác và chia sẻ các dự án của bạn trở nên dễ dàng.

Chúng ta mới chỉ khám phá bề mặt của những gì có thể thực hiện với Altium Designer trên Altium 365. Bắt đầu dùng thử miễn phí Altium Designer + Altium 365 ngay hôm nay.