JESD204C là tiêu chuẩn gì cho ADCs/DACs?

JESD204C cung cấp một giao diện tiêu chuẩn cho các ADC RF với tốc độ lấy mẫu cao, hiện nay đang xuất hiện nhiều hơn trong các ứng dụng không gian thương mại.

Giao diện nối tiếp đã gặp khó khăn trong việc theo kịp nhu cầu của các thành phần bộ chuyển đổi dữ liệu tốc độ cao, cụ thể là ADCs và DACs. Một lựa chọn để thực hiện điều này trước đây là sử dụng liên kết LVDS giữa bộ chuyển đổi dữ liệu và bộ điều khiển chủ. Những liên kết này sẽ cung cấp tốc độ dữ liệu cao qua các cặp vi sai cho một thiết bị đơn lẻ, cung cấp khả năng truyền dữ liệu tốc độ cao từ ADCs lấy mẫu nhanh. Sau đó, JEDEC đã phát hành thông số kỹ thuật JESD204, và kể từ đó, nó đã được tích hợp vào nhiều thành phần như một giao diện bộ chuyển đổi dữ liệu.

Phiên bản mới nhất của các tiêu chuẩn giao diện JESD204, hiện tại là JESD204C, mang lại tốc độ dữ liệu cực cao cho các thành phần ADC/DAC nhanh được sử dụng để lấy mẫu tín hiệu với tốc độ lấy mẫu rất cao. Giờ đây, khi phiên bản mới nhất của tiêu chuẩn đã xuất hiện được hơn 2 năm, có nhiều thành phần có sẵn có thể được sử dụng với FPGAs để cung cấp khả năng lấy mẫu, truyền dẫn và DSP siêu nhanh trong hệ thống RF.

Tổng quan về JESD204C

Tiêu chuẩn JESD204C là phiên bản mới nhất của tiêu chuẩn JESD204 chung, được xuất bản và duy trì bởi JEDEC. Tiêu chuẩn này được phát triển để thay thế việc sử dụng liên kết LVDS giữa các bộ chuyển đổi dữ liệu và hệ thống chủ của chúng. Nó định nghĩa một giao diện và giao thức nối tiếp được sử dụng trong ADC/DAC có tốc độ lấy mẫu cao để lấy mẫu tín hiệu, tổng hợp và đồng bộ hóa. Khía cạnh đồng bộ hóa là quan trọng đối với giao diện này vì nó cho phép một bộ điều khiển chủ đơn lẻ đồng bộ hóa việc lấy mẫu tín hiệu và tổng hợp trên nhiều thiết bị.

Một số thông số hoạt động chính được triển khai trong lớp vật lý được liệt kê trong bảng dưới đây. Phiên bản JESD204C hiện tại cải thiện về tốc độ dữ liệu và đặc điểm mã hóa của phiên bản JESD204B trước đó, sử dụng mã hóa 8b/10b với tốc độ dữ liệu tối đa là 12.5 Gbps. Giao diện này có thể được tìm thấy trong ADC/DAC hoạt động ở mức từ 100 MSps đến 1 GSps hoặc cao hơn.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ví dụ về Topology

Topology của giao diện JESD204C phụ thuộc vào Subclass của giao diện. JESD204B đã giới thiệu Subclass 1 và 2 để thực hiện chiến lược đồng bộ hóa được biết đến với tên gọi độ trễ xác định. Chiến lược này đạt được sự đồng bộ hóa giữa các thiết bị bằng cách xác định sự chênh lệch pha giữa các luồng dữ liệu được truyền đến bộ điều khiển chủ.

- Subclass 0 - Không hỗ trợ độ trễ xác định (tương thích ngược với JESD204A)

- Subclass 1 - Độ trễ xác định đạt được bằng cách sử dụng bộ dao động tham chiếu bên ngoài (SYSREF) làm tín hiệu thời gianSubclass 2 - Độ trễ xác định đạt được bằng cách sử dụng một chân SYNC giữa bộ điều khiển chủ và ADC/DAC

Hai cách thực hiện giao diện được hiển thị trong đồ họa dưới đây.

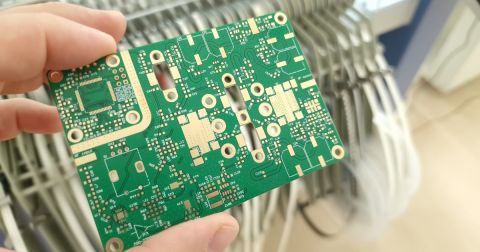

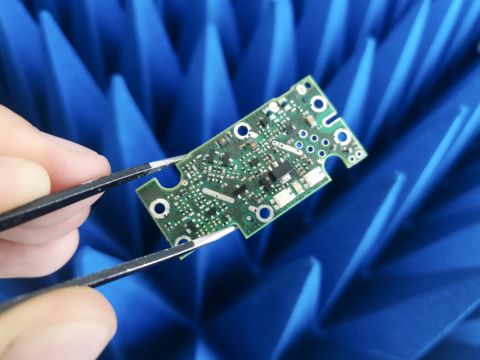

DATA1 và DATA 2 được định tuyến như các cặp vi sai; mỗi làn trong những nhóm I/O này là một cặp vi sai và một thiết bị nhất định có thể có nhiều làn (một số sản phẩm có tới 8 làn cho mỗi thiết bị). Ở cả hai Subclass, nguồn clock được định tuyến đến tất cả các thiết bị theo cách đồng bộ nguồn. Thời gian và độ trễ xác định được đạt được trong mỗi Subclass bằng cách phù hợp SYSREF và DCLK/SYNC với thời gian thiết lập và giữ, cũng như với nhau khi được phân phối qua nhiều bộ chuyển đổi dữ liệu.

Định tuyến, Bù trễ, và Độ Trễ

Độ trễ xác định đã được đề cập ở trên: đây là kỹ thuật mà một bộ điều khiển chủ đơn có thể đồng bộ hóa việc thu thập và tổng hợp dữ liệu trên nhiều thiết bị với thời gian chính xác sao cho độ lệch thời gian giữa các khung lấy mẫu được biết. Điều này được điều chỉnh bằng việc điều chỉnh độ trễ của đường dẫn với nhau sao cho các độ trễ giữa chúng được khớp nối. Một giao diện JESD204B hoặc JESD204C sử dụng việc khớp nối độ trễ trong các bit điều khiển được cung cấp từ SYSREF (trong Subclass 1) hoặc từ các chân SYNC (trong Subclass 2).

Bảng dưới đây mô tả các yêu cầu khớp nối độ dài/độ trễ trong các tín hiệu thời gian cho mỗi Subclass trong các giao diện JESD204B và JESD204C.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Sự khác biệt chính ở đây là cách xử lý các mạch SYNC. Trong Subclass 1, các mạch này chỉ được sử dụng cho đồng bộ hóa nhóm mã, trong khi chúng cũng được sử dụng cho thời gian trong Subclass 2. Do đó, JESD204C có ít tín hiệu hơn cho một số lượng kênh I/O nhất định trong các bộ chuyển đổi dữ liệu.

Tại sao JESD204C so với LVDS?

Lợi ích của giao diện JESD204C đối với việc lấy mẫu và tổng hợp tốc độ cao ở tần số GHz là khả năng loại bỏ sự chênh lệch và độ trễ không khớp giữa nhiều bộ chuyển đổi. Có một ngân sách chênh lệch nhất định cho bất kỳ giao diện JESD204 nào, đó là lượng chênh lệch tối đa có thể được bù đắp trong kế hoạch thời gian của hệ thống để đảm bảo độ trễ xác định trong giới hạn của nhiễu pha. Mục tiêu là đảm bảo bộ điều khiển chủ biết được sự không khớp pha của các dòng dữ liệu đến kết quả và có thể bù đắp cho nó trong logic, từ đó thiết lập thời gian thực sự giữa các tín hiệu được lấy mẫu.

Lý do khác cho việc sử dụng JESD204C là nó giảm thiểu yêu cầu về định tuyến và thời gian trong thiết kế PCB. Trong một triển khai điển hình, các cặp vi sai DATA1 và DATA2 từ Thiết bị 1 và Thiết bị 2 sẽ có một số độ lệch giữa chúng. Với LVDS, điều này đòi hỏi phải khớp các cặp vi sai chạy song song với nhau. Trong JESD204C, chúng ta chỉ cần loại bỏ độ lệch giữa các đường DCLK và SYSREF/SYNC, nhưng không phải các đường dữ liệu giữa các thiết bị. Điều này làm cho giao diện trở nên quan trọng trong các thiết bị tín hiệu hỗn hợp mật độ cao.

Các nhà thiết kế xây dựng công nghệ tiên tiến cho ngành hàng không vũ trụ có thể áp dụng tiêu chuẩn JESD204C sử dụng công cụ thiết kế sản phẩm tốt nhất trong ngành với Altium Designer®. Khi bạn hoàn thành thiết kế và muốn gửi các tệp cho nhà sản xuất, nền tảng Altium 365™ giúp bạn dễ dàng hợp tác và chia sẻ dự án của mình.

Chúng ta mới chỉ khám phá bề mặt của những gì có thể thực hiện với Altium Designer trên Altium 365. Bắt đầu dùng thử miễn phí Altium Designer + Altium 365 ngay hôm nay.