Abschlusstechniken für Übertragungsleitungen im High-Speed-Design

Eine Übertragungsleitung ist ein Leiterpaar, über das Energie in Form eines elektromagnetischen Feldes bereitgestellt wird. Die meisten von uns kennen die Kabel, die zu unseren Häusern führen und Energie liefern, die für den Betrieb unserer Lampen und Geräte erforderlich ist. Beim Leiterplatten-Design handelt es sich um ein Signal in einer Signallage auf einer Fläche bzw. zwischen zwei Flächen.

ABSCHLUSSTECHNIKEN FÜR ÜBERTRAGUNGSLEITUNGEN IM LEITERPLATTEN-DESIGN

In diesem Abschnitt erläutern wir, was Übertragungsleitungen sind; was übertragen wird, wie sie sich verhalten, wenn Schaltsignale gesendet werden und wie diese Schaltsignale für optimale Signalqualität mit Leitungsabschlüssen gesteuert werden können. Am Ende dieses Abschnitts befindet sich eine Liste von nützlichen weiterführenden Materialien.

In diesem und den folgenden Abschnitten geht es vor allem darum, relevante Designregeln aufzustellen und ihre Gültigkeit zu belegen. Der Autor ist der Überzeugung, dass alle Designregeln mit Belegen unterstützt werden sollten und dass außerdem ihre möglichen Beschränkungen aufgezeigt werden sollten.

WAS IST EINE ÜBERTRAGUNGSLEITUNG?

Allgemein gesagt ist eine Übertragungsleitung ein Leiterpaar, über das Energie in Form eines elektromagnetischen Feldes bereitgestellt wird. Die meisten von uns kennen die Kabel, die zu unseren Häusern führen und Energie liefern, die für den Betrieb unserer Lampen und Geräte erforderlich ist. Beim Leiterplatten-Design handelt es sich um ein Signal in einer Signallage auf einer Fläche bzw. zwischen zwei Flächen. Abbildung 1 zeigt die vier Arten von Übertragungsleitungen, die normalerweise in Leiterplatten verwendet werden. Wie Sie sehen können, gibt es zwei Haupttypen: Streifenleitungen und Mikro-Streifenleitungen. Erstere sind Übertragungsleitungen zwischen zwei Flächen, letztere Übertragungsleitungen auf einer Fläche. Dabei sollte man beachten, dass das Wort „Masse“ nicht zur Beschreibung der Flächen verwendet wurde. Die DC-Bezeichnung einer Fläche spielt keine Rolle, wenn es um elektromagnetische Felder geht.

Abbildung 1. Arten von Leiterplatten-Übertragungsleitungen

Verschiedene Kombinationen dieser vier Übertragungsleitungskonfigurationen werden verwendet, um einen Leiterplatten-Lagenaufbau zu bilden. Im nächsten Block erläutern wir, wie sich das Übersprechen von Signalen kontrollieren lässt, die in einer Signallage nebeneinander oder in benachbarten Signallagen übereinander laufen. Auch die Berechnung des charakteristischen Widerstands wird im folgenden Block behandelt.

Es kann enorm aufwendig sein, eine Übertragungsleitung anhand Ihrer verschiedenen charakteristischen Widerstände durchzuarbeiten. Allerdings sollten Sie mit der richtigen Leiterplatten-Designsoftware in der Lage sein, Widerstand und Übersprechen mit intelligenten Designregeln zu kontrollieren und den Aufbau von Leiterplattenlagen einfach und reibungslos zu handhaben. Altium Designer hat dies bei der Gestaltung seiner benutzerfreundlichen Designumgebung berücksichtigt.

Die einheitliche Designumgebung von Altium Designer

WAS LÄUFT ÜBER EINE ÜBERTRAGUNGSLEITUNG?

Um eine Übertragungsleitung richtig umzusetzen, muss man wissen, was über diese Übertragungsleitung läuft. In den Grundlagen der Elektronik lernt man über Spannung und Strom, wobei der Stromfluss als Signal bezeichnet wird. Leider ist das eine vereinfachte Erklärung zum Ablauf der Signalisierung, und wenn der Fokus nur auf dem Stromfluss liegt, kann die Qualität der Signale beeinträchtigt werden.

Die meisten von uns wissen, dass sich elektronische Signale mit oder nahe der Lichtgeschwindigkeit bewegen, die bei ca. 186.000 Meilen oder 300.000 Kilometer pro Sekunde im Vakuum liegt. Der Stromfluss – d. h. die Bewegung der Elektronen in einem Kupferleiter – bewegt sich mit einer Geschwindigkeit von etwa 2.200 Kilometern pro Stunde oder 1.375 Meilen pro Stunde. Das Signal kann also kein Stromfluss sein. Es ist das elektromagnetische Feld. Abbildung 2 zeigt, wie das elektromagnetische Feld um eine Streifenübertragungsleitung herum aussieht. Die Linie kommt aus der Seite und bewegt sich zwischen den beiden Ebenen.

Abbildung 2. Elektromagnetisches Feld um eine Streifenübertragungsleitung herum

Beachten Sie, dass es zwei Feldtypen in der Zeichnung gibt: elektrische Feldlinien, die sich zwischen der Übertragungsleitung und den beiden Ebenen erstrecken, sowie magnetische Feldlinien, die die Übertragungsleitung umgeben. Es ist das Magnetfeld, das die Elektronen in der Übertragungsleitung verschiebt. Das wird als Stromfluss bezeichnet und ist mit einem Amperemeter messbar. In den beiden Ebenen fließt ein gleicher und entgegengesetzter Strom, den wir oft als Rückstrom bezeichnen. Wie dieser Rückstrom zwischen den beiden Ebenen aufgeteilt wird, hängt davon ab, wie nahe die jeweilige Ebene an der Übertragungsleitung liegt.

Zu wissen, wie elektromagnetische Felder erzeugt werden und wie man damit arbeitet, ist der Schlüssel zum Erfolg in der Hochgeschwindigkeitselektronik.

ERZEUGEN VON UND ARBEITEN MIT ELEKTROMAGNETISCHEN FELDERN IM LEITERPLATTEN-DESIGN

Jedes elektronische Signal soll ein Spannungssignal an einen Empfänger liefern. Dazu wird Energie in Form eines elektromagnetischen Feldes erzeugt und über eine Übertragungsleitung an den Empfänger gesendet. Abbildung 3 zeigt einen typischen Signalpfad mit Treiber, Empfänger und einer Übertragungsleitung, die diese verbindet.

Wenn Übertragungsleitung und Leitungsabschlusstyp oder -last abweichend sind, können unterschiedliche Reflexionen auftreten, z. B. eine stehende Welle. Die Handhabung solcher Szenarien erfordert einen erhöhten Arbeitsaufwand für den Leiterplatten-Designer, der beispielsweise die Reflexionskoeffizienten bestimmen und ermitteln muss, wie solche Abweichungen am besten vermieden werden können.

Um dem Empfänger eine möglichst hochwertige Spannungswellenform zu liefern, ist es wichtig, dass das Signal auf dem Weg von der Quelle zum Empfänger nicht beeinträchtigt wird. Die häufigste Form der Beeinträchtigung sind Reflexionen eines Teils des Signals (der Energie) an Widerstandsabweichungen. Idealerweise ist Zout = Zo = Zload, wodurch keine Reflexionen entstehen. In der Signalintegritätstechnik geht es darum, diese Anforderung zu erfüllen, indem Leiterplattenaufbauten so gestaltet werden, dass ein Sollwiderstand erreicht wird, und indem Leitungsabschlüsse hinzugefügt werden, um Abweichungen zu reduzieren.

Abbildung 3. Typischer Signalpfad mit Quell, Last und Übertragungsleitung

Leitungsabschlusstypen

Sobald die über eine Übertragungsleitung gesendete elektromagnetische Energie die Spannungswellenform an den Empfänger übertragen hat, muss sie aus dem System entfernt werden, oder sie wird weiter herumreflektiert und verursacht unerwünschte Transienten, die zu einem falschen Auslösen von Lasten entlang der Leitung bzw. zur kompletten Störung einer Eingabe führen können, falls die Reflexionen zu groß sind. Der Zweck von Abschlüssen besteht darin, diese Energie zu entfernen, sobald die Spannungswellenform übertragen wurde.

Es gibt zwei Leitungsabschlusstypen: seriell und parallel. Abbildung 4 veranschaulicht die möglichen Abschlusstechniken für Übertragungsleitungen und wie diese Abschlüsse mit der Leitung verbunden werden. Die seriellen Abschlüsse werden im Netz am Ausgang des Treibers angeschlossen. Wie dieser Abschluss die EM-Energie von der Übertragungsleitung entfernt, wird im nächsten Abschnitt erläutert. Parallele Abschlüsse werden am Treiberende einer Übertragungsleitung angebracht, um die EM-Energie zu entfernen, wenn sie am Empfänger ankommt.

Abbildung 4. Leitungsabschlusstypen

Beachten Sie in Abbildung 4, dass am Empfängerende der Übertragungsleitung in der Nähe des Empfängers vier Leitungsabschlusstypen platziert sind. Dies sind verschiedene Implementierungsmöglichkeiten für parallele Abschlüsse. Auf die Vorzüge der einzelnen Verfahren wird später eingegangen. Es gibt nur einen Leitungsabschluss in der Nähe des Treibers. Dies ist ein serieller Abschluss. Die Funktionsweise der Reflexionskontrolle wird im nächsten Abschnitt behandelt.

Die vier Optionen für parallele Abschlüsse sind: AC, Diode, Innen- und Einzelwiderstand zu einer Abschlussspannung.

AC-Abschlüsse haben ihren Ursprung in der Zeit von TTL, als die Anstiegszeit so anstieg, dass ein paralleler Abschluss am Empfänger nötig war. TTL konnte die DC-Belastung eines 50-Ohm-Abschlusses nicht unterstützen. Daher wurde ein Kondensator verwendet, um den Abschluss mit der Übertragungsleitung zu verbinden, sodass dieser die Energie in der schnellen Schaltflanke absorbieren konnte, während er im stabilen Zustand abgeschaltet blieb. Dies funktionierte, solange das Verhältnis von Anstiegszeit zu Taktrate sehr groß war. Mit zunehmender Taktrate führte die in Abbildung 5 gezeigte Verschlechterung dazu, dass das Signal nicht mehr brauchbar war. Die rote Wellenform ist das Signal, das den Treiber verlässt, und die orange Wellenform ist das Signal, das am Empfänger ankommt. Dies ist eindeutig eine unbefriedigende Möglichkeit, die Übertragungsleitung parallel abzuschließen, und sollte niemals verwendet werden.

Abbildung 4. AC-abgeschlossener Takt bei 66 MHz

Diodenabschlüsse kamen auf, als Überschwingungen – also Reflexionen, die über Vdd ansteigen oder unter die Masse reichten – die Eingangsnennspannung der Empfänger überstiegen. Wie sich zeigen wird, kann dieses Problem durch die Verwendung einfacher paralleler oder serieller Abschlüsse vermieden werden. Diodenabschlüsse sind eine sehr kostspielige Methode zur Kontrolle von Überschwingungen und sollten nicht verwendet werden, sofern die richtigen Techniken zum Abschluss von Übertragungsleitungen verwendet werden.

Es gibt eine Ausnahme von dieser Regel. Der PCI-Bus erfordert serielle Abschlüsse in den Ausgängen aller Treiber. Ingenieure, die das nicht verstanden haben und Erweiterungskarten für PCs entwickelten, ließen die Reihenabschlusswiderstände weg, um Kosten zu sparen. Wenn diese Karten in ein PC-Motherboard eingesteckt wurden, kam es häufig zu Ausfällen durch Überschwingen. Das Konsortium, das den PCI-Bus-Standard pflegt, konnte dies nicht verhindern und hat die Spezifikation um die Anforderung erweitert, dass alle Eingänge mit Dioden ausgestattet sein müssen, um PCI-konform zu sein. Damit wurde das Problem gelöst.

Parallele Widerstandsabschlüsse sind die einfachste Möglichkeit, eine Übertragungsleitung abzuschließen. Abbildung 5 zeigt einen GTL-Bus mit parallelem Abschluss. Beachten Sie, dass der Abschlusswiderstand an eine Abschlussspannung angeschlossen ist, die normalerweise mit Vtt bezeichnet wird und eine von Vdd separate Spannungsversorgung ist. Dies bedeutet, dass ein System mit parallelen Abschlüssen zwei Spannungsversorgungen benötigt, die sehr schnelle Schalttransienten liefern können. Wenn ein System viele Übertragungsleitungen hat, die parallel abgeschlossen werden müssen, lohnen sich diese zusätzlichen Kosten. Wenn nur wenige Leitungen parallel abgeschlossen werden müssen, z. B. die Taktleitungen in einigen DDR-Konfigurationen, können diese zusätzlichen Kosten eine Belastung darstellen. In diesem Fall ist ein Innenwiderstandsabschluss sinnvoll.

Abbildung 5. Parallel abgeschlossene GTL-Übertragungsleitung

Parallele Innenwiderstandsabschlüsse sind eine Methode, mit der ein Äquivalent zu Vtt und Rt geschaffen wird, das für den parallelen Abschluss einer Übertragungsleitung erforderlich ist, ohne dass dafür eine separate Spannungsversorgung für Vtt gebraucht wird. Abbildung 6 zeigt die Methode zur Berechnung der Widerstandswerte für ein Thevenin-Abschlussnetzwerk zusammen mit einer Beispielrechnung.

Abbildung 6. Verfahren zur Berechnung der Innenwiderstandsabschlusswerte

Funktionsweise serieller Abschlüsse

Seriell abgeschlossene Übertragungsleitungen sind die primäre Methode zum Verbinden von CMOS-Logikgeräten. Die Funktionsweise dieser Übertragungsleitungen muss man unbedingt verstehen, um sicherzustellen, dass die Signale ordnungsgemäß an die einzelnen Empfänger weitergeleitet werden. Diese Funktionsweise ist keineswegs intuitiv und durchaus verwirrend, bis sie gut erklärt wird. Diese kurze Zusammenfassung soll Klarheit schaffen.

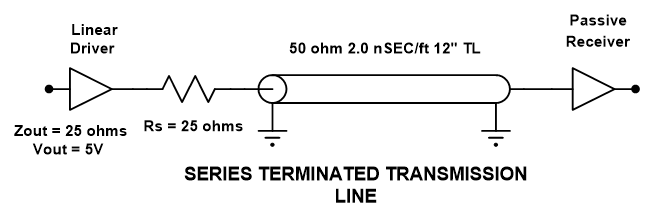

In Abbildung 7 ist ein typischer 5V-CMOS-Treiber mit einer 50-Ohm-Übertragungsleitung dargestellt, die an einen passiven CMOS-Empfänger angeschlossen ist. Das bedeutet, dass er einfach auf die Spannungswellenform reagiert, die an seinem Eingang ankommt. (Für die Zwecke dieser Erklärung sehen CMOS-Empfänger wie sehr kleine Kondensatoren aus, die als offene Stromkreise betrachtet werden können.) In diesem Beispiel ist die Linie 12 Zoll oder etwa 30 cm lang. In einer Leiterplatte bewegt sich die Energie mit ungefähr sechs Zoll pro Nanosekunde, sodass diese Linie etwa zwei Nanosekunden lang ist.

Abbildung 7. Ein typischer 5-V-CMOS-Schaltkreis mit seriellem Abschluss

In Abbildung 8 ist ein gleichwertiger Schaltkreis für eine Übertragungsleitung wie in Abbildung 7 dargestellt.

Abbildung 8. Ein gleichwertiger Schaltkreis für die Übertragungsleitung in Abbildung 7

Beachten Sie, dass Kapazität, Widerstand und Induktivität entlang der Länge der Übertragungsleitung verteilt sind. Diese Elemente werden als „parasitär“ bezeichnet und bestimmen das Verhalten der Übertragungsleitung, wobei das Verhältnis von Induktivität pro Längeneinheit zu Kapazität pro Längeneinheit den charakteristischen Widerstand bestimmt, wie in Gleichung 2 gezeigt.

Lo ist die Induktivität pro Längeneinheit und Co die Kapazität pro Längeneinheit. Diese beiden Variablen werden für einen bestimmten Übertragungsleitungstyp unter Verwendung eines Werkzeugs, wie z. B. eines 2D-Feldlösers, bestimmt. Viele Feldlöser sind als Teil von Signalintegritätstools verfügbar.

In fast allen Fällen ist der Wert von R im Vergleich zu L und C so gering, dass er ignoriert werden kann. Solange die beteiligten Frequenzen ein GHz nicht überschreiten, kann man mit dieser Annahme arbeiten.

Gleichung 2. Widerstand als Funktion der verteilten Kapazität und Induktivität

Wenn der Treiber in Abbildung 7 die Logikebene auf der Übertragungsleitung von einer logischen 0 auf eine logische 1 verschieben soll, muss er die verteilte parasitäre Kapazität der Übertragungsleitung aufladen. Dies ist die primäre Energie, die von CMOS-Logikschaltungen verbraucht wird. Wenn derselbe Treiber den Logikpegel von einer logischen 1 auf eine logische 0 verschieben möchte, muss er diese Ladung entfernen.

Tipp: Wenn ein Signal entlang einer Draht- oder Übertragungsleitung gesendet wird, handelt es sich dabei um Energie in Form eines elektromagnetischen Feldes. Diese Energie läuft entlang des Pfades und wird an den Enden des Pfades immer weiter reflektiert, sofern sie nicht durch einen Abschlusswiderstand absorbiert wird bzw. langsam im Widerstand des Leiters verlorengeht. Wenn die Enden des Pfades offene Schaltungen sind, hat die reflektierte Energie die gleiche Polarität wie die einfallende Energie. Wenn die Enden des Pfades kurzgeschlossen sind, wird die reflektierte Energie invertiert.

Wie Ladung auf eine Logikleitung gelegt wird, um sie von einer Null auf eine Eins zu schalten

Abbildung 9 zeigt die äquivalente Schaltung von Abbildung 7 in dem Moment, in dem der Treiber beginnt, die Logikleitung von einer Null auf eine Eins zu schalten. Beachten Sie, dass durch die Kombination des Treiberausgangswiderstands und des seriellen Abschlusses im oberen Teil sowie des Widerstands der Übertragungsleitung im unteren Teil ein Spannungsteiler gebildet wurde. Wenn der serielle Abschluss richtig gewählt wurde, ist die Kombination aus Zout und Zst gleich Zo. In diesem Beispiel betragen beide 50 Ohm, sodass die Spannung am Eingang der Übertragungsleitung V/2 beträgt.

Abbildung 9. Äquivalenter Schaltkreis zu Abbildung 7 zu Beginn des Übergangs von Null zu Eins

Abbildung 10 zeigt die Spannungswellenformen am Eingang der Übertragungsleitung und am Eingang des Empfängers im Zeitverlauf. Die rote Wellenform ist der Eingang zur Übertragungsleitung und die orangefarbene Wellenform ist der Eingang zum Empfänger am Ende der Übertragungsleitung. Beachten Sie, dass der Spannungspegel unmittelbar nach dem Übergang von Null auf Eins nur die Hälfte von Vdd bzw. die halbe Größe beträgt. Dies liegt an dem in Abbildung 9 gezeigten Spannungsteiler. Dieser Spannungspegel wird oft als „Bench“-Spannung bezeichnet.

Was in die Übertragungsleitung geschickt wurde, ist Energie in Form eines elektromagnetischen Feldes (EM), dessen Spannungskomponente V/2 ist. Diese Energie lädt die parasitäre Kapazität der Übertragungsleitung auf einen Spannungspegel von V/2 auf, während das Feld die Übertragungsleitung verlässt.

Nach zwei Nanosekunden (der elektrischen Länge der Übertragungsleitung) ist die Leitung vollständig auf V/2 aufgeladen und das elektromagnetische Feld trifft am Empfänger auf eine offene Schaltung. Trifft ein solches Feld auf eine offene Schaltung, wird keine Energie darin absorbiert, sondern mit der gleichen Stärke zurückgeworfen, mit der es ausgegangen ist.

Im Moment der Totalreflexion ist der Spannungspegel am Ende der Leitung V/2. Da die Spannungsgröße des elektromagnetischen Feldes V/2 nach der Gesamtreflexion beträgt, ist die Amplitude V. Beachten Sie, dass das orangefarbene Signal eine Amplitude von V aufweist, sobald das EM-Feld am Ende der Leitung eintrifft. Auf dem Rückweg wird die parasitäre Kapazität der Übertragungsleitung bis auf V aufgeladen. Sobald das elektromagnetische Feld zum Treiber zurückkehrt, trifft es auf die in Abbildung 11 gezeigte äquivalente Schaltung.

Abbildung 10. Spannungswellenformen an den beiden Enden der Übertragungsleitung in Abbildung 7.

Abbildung 11. Äquivalente Schaltung des Treibers in Abbildung 7 aus Sicht des elektromagnetischen Feldes

Die Summe von Zout und Zst beträgt 50 Ohm und die Spannungsquelle ist ein Kurzschluss. Zusammen bilden sie einen Parallelabschluss, der den gleichen Wert hat wie der charakteristische Widerstand der Leitung. Dadurch wird die gesamte Energie im elektromagnetischen Feld absorbiert und der Spannungspegel auf der Übertragungsleitung stabilisiert sich bei 5 Volt – eine ideale logische 1 für diese Schaltung.

Umschalten von einer logischen 1 auf eine logische 0

Wenn die Schaltung in Abbildung 8 von einer logischen 1 auf eine logische 0 umschaltet, hat der Treiber die Aufgabe, die Ladung auf der dort angebrachten Leitungskapazität zu entfernen, um sie von einer logischen 0 auf eine logische 1 zu bringen. Dazu bewegt sich der Treiberpegel intern von 5 V auf 0 V. Wie beim Übergang von einer logischen 0 zu einer logischen 1 ähnelt die Ersatzschaltung der in Abbildung 9 gezeigten. Jetzt liegt jedoch die Leitung bei 5 V, und am Ausgangswiderstand sowie am seriellen Abschlusswiderstand liegen 0 V an. Der Spannungsteiler arbeitet wie zuvor.

Infolgedessen wird die Leitungsspannung auf V/2 verschoben und Ladung aus der Leitungskapazität wird auf diesen Pegel reduziert, während die Energie sich durch die Leitung hinabbewegt. (Der Spannungspegel dieses Übergangs beträgt –V/2.) Wenn das EM-Feld zwei Nanosekunden später am Ende der Übertragungsleitung ankommt, trifft es auf eine offene Schaltung und wird durch die Leitung zurückreflektiert. Das Ergebnis nach der Reflexion ist, dass die Leitung jetzt bei 0 V liegt. Zwei Nanosekunden später kommt das EM-Feld wieder beim Treiber an, trifft auf die in Abbildung 5 gezeigte Schaltung und wird absorbiert. Die resultierende Wellenform ist in Abbildung 12 dargestellt.

Abbildung 12. Spannungswellenformen an den beiden Enden der Übertragungsleitung nach dem Umschalten von 1 auf 0

Beachten Sie, dass die Spannungswellenform am Empfänger (orange) ein ordnungsgemäßes Rechteckwellen-Logiksignal ist, was das Ziel dieses Signalwegs ist. Diese Signalisierungsmethode wird als „Reflexionswellenschaltung“ bezeichnet, da der korrekte logische Pegel durch die reflektierte Welle auf ihrem Weg durch die Übertragungsleitung erzeugt wird. Dies ist die Methode mit dem geringsten Stromverbrauch für die Hochgeschwindigkeits-Logiksignalisierung, da dem Stromnetz nur während des Aufladens der Leitung Strom entnommen wird. Sobald die Leitung vollständig auf eine logische 1 geladen ist, geht die Stromaufnahme auf Null.

Diese Umschaltmethode wird auch im PCI-Bus verwendet, der in den meisten PCs verbaut ist.

Außerdem ist zu beachten, dass die Spannungswellenform am Treiberausgang für die Zeit, die der Umlaufverzögerung entlang der Übertragungsleitung entspricht, bei jedem Schaltvorgang einen unbestimmten logischen Zustand aufweist. Werden Lasten entlang der Länge der Übertragungsleitung platziert, wie es beim PCI-Bus der Fall ist, kommen sie erst dann in einen „datentauglichen“ Zustand, wenn die reflektierte Welle auf dem Rückweg an ihnen vorbeizieht. Daher muss die Taktung von Daten an diesen Eingängen verzögert werden, bis sie an allen Eingängen gut sind. Auf diese Weise werden Daten auf dem PCI-Bus und anderen Busprotokollen getaktet, die auf Reflexionswellenschaltung beruhen.

Widerstandseditor im Editor für Regeln und Beschränkungen von Altium Designer

Was passiert, wenn der Treiberwiderstand nicht mit dem Leitungswiderstand übereinstimmt?

Die in Abbildung 13 gezeigte Schaltung entspricht der in Abbildung 7 gezeigten, außer dass der serielle Abschluss nicht seriell mit dem Ausgang eingefügt wurde.

Abbildung 13. Eine nicht abgeschlossene 5V-CMOS-Übertragungsleitung

Abbildung 14 zeigt die Schaltwellenform für den Übergang von einer logischen 0 zu einer logischen 1. Beachten Sie, dass die Bench-Spannung deutlich höher als V/2 ist. Tatsächlich beträgt sie 2V/3 oder 2/3 der insgesamt 5 Volt, also 3,33 V. Warum ist das so? Wenn Sie sich in diesem Beispiel den Spannungsteiler in Abbildung 3 anschauen, beträgt der obere Widerstand 25 Ohm, oder Zout des Treibers, und der untere Widerstand bzw. der untere charakteristische Widerstand beträgt 50 Ohm, wodurch der 2/3-Spannungspegel entsteht.

Das EM-Feld lädt die Leitungskapazität wie zuvor auf diesen Wert auf. Wenn das EM-Feld zwei Nanosekunden nach seiner Erzeugung am Empfänger ankommt, wird es zurückreflektiert und verdoppelt die Spannung auf 6,66 V. Wie bisher lädt das EM-Feld die Leitungskapazität bis zu 6,66 V auf. Nach zwei weiteren Nanosekunden erreicht das EM-Feld wieder den Treiber und trifft auf einen Leitungsabschluss wie in Abbildung 5 gezeigt. Der parallele Abschluss beträgt jedoch nicht 50 Ohm. Stattdessen beträgt er 25 Ohm. Nun passieren zwei Dinge. Erstens beträgt der Spannungsteiler diesmal oben 50 Ohm und unten 25 Ohm, wie in Abbildung 15 gezeigt, wobei der Wert des seriellen Abschlusses 0 Ohm beträgt, sodass die Spannung heruntergeteilt wird. Zweitens wird nicht die gesamte Energie absorbiert.

Wenn ein EM-Feld auf einen parallelen Abschluss trifft, dessen Wert niedriger ist als der TL, hat die reflektierte Energie die entgegengesetzte Polarität der einfallenden Wellenform. Dies ist am Treiber nicht sichtbar. Zwei Nanosekunden später kommt die Energie am Empfänger an und wird, wie zu sehen, invertiert bzw. negativ.

Wie zuvor verdoppelt die Energiemenge den Spannungspegel am Empfänger und geht zurück zum Treiber. Sobald sie am Treiber ankommt, wird ein Teil davon absorbiert und der Rest invertiert reflektiert. Dies geht so lange weiter, bis die gesamte Energie in der Ausgangsimpedanz des Treibers absorbiert wurde und sich der Logikpegel bei 5 V einpendelt. Dies ist in Abbildung 16 zu sehen.

Abbildung 14. Schaltwellenform für eine nicht abgeschlossene CMOS-Übertragungsleitung

Abbildung 15. Ersatzschaltung von Abbildung 13, Zst = 0

Abbildung 16. Schaltwellenform für eine nicht abgeschlossene CMOS-Übertragungsleitung

Mit der Wellenform in Abbildung 16 gibt es zwei Probleme. Zunächst liegt die Spannung 1,66 Volt über Vdd. Diese Überspannung kann zu Logikfehlern führen oder den Empfänger beschädigen. Zweitens bewirkt das Signal, nachdem es wieder am Treiber angekommen ist und invertiert wird, dass die logische 1 am Empfänger auf unter 4 Volt abfällt. Dies reduziert die logische 1 auf einen Pegel, der zu einem Logikfehler führen könnte. Beides ist schlecht. Aus diesem Grund wird einer solchen Schaltung ein serieller Abschluss hinzugefügt.

Abbildung 17 zeigt die Wellenform, wenn das Signal auf eine logische 0 schaltet. Wie Sie sehen können, treten in diesem logischen Zustand dieselben Pegelverletzungen auf.

Der Maßstab ist 1 Volt pro Division, wobei die unterste Linie bei -1 V und die oberste bei 8 V liegt

Abbildung 17. Eine weitere Schaltwellenform für eine nicht abgeschlossene CMOS-Übertragungsleitung

Über- und Unterschwingungen

Die Begriffe „Überschwingen“ und „Unterschwingen“ werden verwendet, um ein unerwünschtes Ausbrechen von Signalwellenformen aufgrund von Reflexionen zu beschreiben, die durch Widerstandsänderungen verursacht werden. Abbildung 18 zeigt eine 50-Ohm-Übertragungsleitung mit parallelem Abschluss und drei verschiedenen Werten für den Abschlusswiderstand. Die dargestellten Signale werden am Treiberausgang gemessen. Wenn eine Übertragungsleitung perfekt mit ihrem charakteristischen Widerstand – in diesem Fall 50 Ohm – abgeschlossen ist, wird die gesamte Energie vom Abschluss absorbiert, wenn sie am Empfänger ankommt. Es wird keine Energie zum Treiber zurückreflektiert. Dies wird durch die mittlere Wellenform in Abbildung 18 dargestellt.

Abbildung 18. Parallel abgeschlossene Übertragungsleitung

Als der Wert des Abschlusswiderstands auf 70 Ohm geändert wurde, war die Leitung nicht mehr perfekt abgeschlossen und ein Teil der Energie wurde zum Treiber zurückreflektiert. Gleichung 3 wird oft als Reflexionsgleichung bezeichnet. Sie wird verwendet, um den Reflexionsgrad zu berechnen, der bei einer Widerstandsabweichung auftritt. In der Gleichung ist Zl der Widerstand stromaufwärts und Zo der Widerstand stromabwärts. In diesem Fall ist der Widerstand stromaufwärts der Leitungswiderstand von 50 Ohm, und der Widerstand stromabwärts der Leitungsabschlusswiderstand. Wenn der Abschlusswiderstand bei 70 Ohm liegt, prognostiziert die Gleichung, dass 16 % der einfallenden Spannung reflektiert werden und die Polarität positiv ist. Dadurch wird die einfallende Spannung erhöht, wie in Abbildung 18 zu sehen, was zu einem Überschwingen führt.

Wenn der Wert des Abschlusswiderstands auf 30 Ohm geändert wird, ist die Leitung nicht mehr perfekt abgeschlossen und ein Teil der Energie wird zum Treiber zurückreflektiert. Bei Verwendung von Gleichung 3 beträgt der reflektierte Wert 25 %, der Wert ist jedoch negativ, wodurch er vom einfallenden Wert abgezogen wird. Dies wird als Unterschwingen bezeichnet.

Gleichung 3. Die Reflexionsgleichung

Wenn die Logikspannungen im Bereich von 5 Volt lagen, wurden die Überschwingungen oft so groß, dass sie zu Logikfehlern oder sogar Schaltkreisschäden führten. Aus diesem Grund lag der Schwerpunkt immer darauf, übermäßiges Überschwingen zu vermeiden. Aus diesem Grund finden sich Dioden an den Eingängen. Da mit der Zeit die Logikpegel immer weiter sanken, wurde es weniger wahrscheinlich, dass aus diesen Gründen Fehler auftreten würden. Und während Logikpegel sanken, ist die Noise Margin ebenfalls kleiner geworden, wodurch Logikfehler durch eingekoppeltes Rauschen zu einem großen Problem wurden. Infolgedessen wird bei den meisten aktuellen Logikfamilien mehr Wert auf die Vermeidung von Unterschwingungen gelegt.

Bestimmen der Abschlusswiderstandswerte

Wie bereits erwähnt gibt es zwei Abschlusstypen: seriell und parallel. Der Wert für einen Parallelabschluss ist der charakteristische Widerstand der abgeschlossenen Schaltung oder der Übertragungsleitung. Die Bestimmung der Werte der seriellen Abschlusswiderstände ist nicht so einfach. Der serielle Abschlusswiderstand soll sich zum Widerstand der Übertragungsleitung addieren, wenn er mit dem Ausgangswiderstand des Treibers kombiniert wird. Mit anderen Worten: Zst = Zo – Zout. Wo erhält man den charakteristischen Ausgangswiderstand des Treibers? Es wäre schön, wenn diese Informationen als Teil des Komponentendatenblatts gedruckt würden. Leider kommt das nur selten vor. Um Zout zu finden, muss man das IBIS- oder SPICE-Modell des Ausgabetreibers abrufen und es aus der VI-Kurve berechnen. Die meisten SI-Modellierungswerkzeuge führen diese Berechnung durch und zeigen den Ausgangswiderstand an. Einige berechnen sogar den empfohlenen seriellen Widerstandswert.

Hier ist es besonders hilfreich, über eine live aktualisierte und leicht zugängliche Komponentenbibliothek zu verfügen, mit Zugriff auf Lieferanteninformationen und einfach zu aktualisierende Komponentenmodelle. Glücklicherweise haben Sie über Altium Designer Zugriff auf eine Vielzahl von Komponentenbibliotheken und in Echtzeit aktualisierte Lieferanteninformationen, auf die Sie in Ihren Produktionsteams von überall aus zugreifen können.

Lage der Leiterplattenabschlüsse

Oft stellt sich die Frage, wie nah ein Abschluss am Ende einer Übertragungsleitung liegen muss, damit er korrekt funktionieren kann. Es wäre gut, diese Widerstände so auf der Leiterplattenoberfläche zu platzieren, dass sie das Layout oder die Bestückung nicht unnötig erschweren.

Die Platzierung von parallelen Widerständen ist relativ einfach. Jede Position hinter der Übergabe des Signals an den Geräteeingang ist in Ordnung, da die Spannungswellenform bereits übergeben wurde und die Energie nur noch entfernt werden muss. Platzieren Sie daher die parallelen Abschlüsse nach der letzten Last auf der Übertragungsleitung in sicherer Entfernung. Sie müssen sich nicht unter dem BGA-Pin-Feld befinden, wodurch das Routing der Leiterplatte sowie die Bestückung einfacher werden.

Für die Positionierung von seriellen Abschlüssen muss man etwas mehr analysieren. Da der serielle Abschlusswiderstand oder die Leitungsabschlussschaltung mit dem charakteristischen Ausgangswiderstand des Treibers summiert werden soll, muss er sich nahe genug befinden. Die Leiterbahn, die die beiden verbindet, muss also kurz genug sein, um nicht als Übertragungsleitung zu fungieren, die einen Widerstand vom anderen isoliert. Die einzige Möglichkeit, eine akzeptable Länge für die Verbindung zu finden, besteht darin, mit einem Simulator zu ermitteln, wie lang diese Verbindung sein darf, damit am Empfänger trotzdem eine akzeptable Wellenform vorliegt. Es stellt sich heraus, dass die zulässige Länge eine direkte Funktion der Anstiegszeit des Treibers ist. Je schneller die Anstiegszeit, desto kürzer ist die zulässige Verbindung.

Stichleitungen

Eine Stichleitung ist ein Abzweig von der Hauptübertragungsleitung. Unter bestimmten Bedingungen kann sich eine Stichleitung negativ auf ein Signal auswirken. Wenn eine Stichleitung lang genug ist, scheint sie das Signal vorübergehend kurzzuschließen. Abbildung 20 zeigt eine Übertragungsleitung mit einer Länge von einer Viertelwellenlänge bei einer bestimmten Frequenz F.

Abbildung 19. Übertragungsleitung mit Stichleitung

In Abbildung 20 ist eine Sinuswelle dargestellt, die am Eingang der Übertragungsleitung eingespeist wird. Eine Viertelwellenlänge bzw. 90 Grad später kommt sie am offenen Ende der Übertragungsleitung an, die eine offene Schaltung ist. Da das Ende offen ist, wird die gesamte Energie zurückreflektiert, ohne invertiert zu werden. Eine Viertelwellenlänge später kommt sie dann genau um 180 Grad phasenverschoben zum Eingangssignal zurück und hebt es auf. Der Effekt ist ein Kurzschluss bei der Frequenz F.

HF-Ingenieure verwenden Viertelwellenlängen-Stichleitungen als Bandsperrfilter in bestimmten Funkkomponenten, bei denen eine einzelne Frequenz Störungen verursacht. Leider gibt es nur wenige Stellen in der Logik, an denen die Eliminierung einer einzelnen Frequenz erforderlich ist. Stattdessen verursachen Stichleitungen Wellenformumkehrungen wie die in Abbildung 21 gezeigte blaue Wellenform. Diese Wellenformumkehrung erfolgt getaktet, was zu einer doppelten Taktung führt.

Abbildung 20. Wellenform auf einer Viertelwellen-Übertragungsleitung

Abbildung 21. Wellenformen auf einer Taktleitung mit den Effekten einer Stichleitung

Die einzige zuverlässige Methode, um zu ermitteln, ob eine Stichleitung kurz genug ist, um das in Abbildung 21 gezeigte Problem zu vermeiden, besteht darin, die vorgeschlagene Topologie in einem Tool wie Hyperlynx zu simulieren und zu prüfen, ob die Verschlechterung der Wellenform akzeptabel ist. Da die Anstiegszeiten vieler aktueller ICs so kurz sind (häufig weniger als 100 Picosek.), kann die Länge der Leiterbahn von der Kugel auf einem BGA bis zum eigentlichen Kontakt auf dem Chip selbst lang genug sein, um zu Problemen zu führen. Diese Länge muss in die Simulation einbezogen werden.

Vias

Der Begriff Via beschreibt die metallisierte Durchkontaktierung, über die der Signalpin eines IC mit einer Leiterbahn auf einer inneren Lage bzw. auf der gegenüberliegenden Seite einer Leiterplatte verbunden wird. Vias sind metallisierte Durchkontaktierungen, die sowohl Kapazität als auch Induktivität aufweisen. Die Induktivität der Durchkontaktierung beträgt etwa 35 Picohenry pro mil Länge (1,4 Nanohenry pro mm). Ob diese Induktivität ein Problem darstellt oder nicht, hängt davon ab, wie das Via verwendet wird.

Wenn über das Via ein Bypass-Kondensator oder eine Komponentenstromleitung mit einer Ebene verbunden wird, kann diese Induktivität ein Problem bei Signalen mit sehr schnellen Anstiegszeiten darstellen bzw. die Leistung von Bypass-Kondensatoren verschlechtern.

Lagenaufbau-Management leicht gemacht

Die meisten Vias werden mit Bohrern von 12 mil (0,3 mm) oder kleiner erstellt. Ein Via, das mit einem 12-mil-Bohrer in einer 2,5 mm (100 mil) dicken Leiterplatte erstellt wurde, weist im Durchschnitt etwa 0,3 pF auf. Ob diese zusätzliche Kapazität ein Signalintegritätsproblem verursacht oder nicht, lässt sich am besten mit einem guten Simulator ermitteln. Der Autor dieses Artikels hat die Erfahrung gemacht, dass bei Datenraten bis zu etwa 3 Gb/S die Verschlechterung durch Vias akzeptabel ist.

Ein gutes Lagenaufbau-Management in Ihrer Leiterplatten-Designsoftware sowie ein einfacher Übergang zwischen 3D-Modell-Viewern helfen dabei, Vias zu integrieren und sie in Ihren Designs im Blick zu behalten. Lassen Sie nicht zu, dass Via- und Microvia-Management zu Problemen in Ihren Designs führen, so kurz vor der Ziellinie.

Vias im 3D-Modell-Viewer von Altium Designer

Rechtwinklige Biegungen

Der Effekt von rechtwinkligen Biegungen in Signalleiterbahnen ist seit Beginn der Leiterplattenherstellung ein Grund zur Sorge. Zu den bekannten Effekten gehören:

- Rechtwinklige Biegungen verursachen EMI.

- Rechtwinklige Biegungen verursachen Signalintegritätsprobleme.

- Rechtwinklige Biegungen verursachen Säurefallen bei der Leiterplattenherstellung.

Beispiel für die Winkel der Leiterbahnführung

In einigen Fällen wurden große Anstrengungen unternommen, um rechtwinklige Biegungen komplett zu vermeiden. Sogar ganze CAD-Systeme wurden überflüssig, weil sie rechtwinklige Biegungen in Leiterbahnen einfügten. Eine berechtigte Frage wäre: „Sind rechtwinklige Biegungen ein Problem bei Logikschaltungen?“ Punkt 1 am Ende dieses Abschnitts beschreibt eine Testplatte, die zur Messung der Auswirkungen von rechtwinkligen Biegungen konstruiert wurde. Diese Leiterplatte wurde mit rechtwinkligen, spitzen und stumpfen Winkelbiegungen konstruiert, um zu sehen, welche Auswirkungen das auf die drei oben aufgeführten Aspekte haben würde. Die Tests wurden im EMI-Labor der University of Missouri, Rolla, durchgeführt.

Man kam dabei zu dem Ergebnis, dass die rechtwinkligen Biegungen tatsächlich zu keinem der mutmaßlichen Probleme führten. Eine berechtigte Frage wäre nun: „Wie sind diese Ideen entstanden?“ Sehr wahrscheinlich lag es daran, dass HF-Ingenieure grundsätzlich alle Ecken abrunden. Das rührt daher, dass an scharfen Ecken bei hohen HF-Leistungspegeln Koronaentladungen auftreten.

Das Merkwürdige ist, dass man bereits seit mindestens 40 Jahren weiß, dass rechtwinklige Biegungen keine Probleme verursachen, was auch durch Tests und veröffentlichte Artikel nachgewiesen wurde. Doch die Mythen werden weiterhin von Ingenieur zu Ingenieur weitergegeben.

VERWEISE ZUM THEMA ÜBERTRAGUNGSLEITUNGEN UND ABSCHLUSSTYPEN

- „90 Degree Corners, The Final Turn“ Doug Brooks, et al., Printed Circuit Design, Januar 1998.

- SIGNAL INTEGRITY- SIMPLIFIED, Eric Bogatin, Prentice Hall, 2004.

- „Reflections and Crosstalk in Logic Circuit Connections“, John A DeFalco, IEEE Spectrum, Juli 1970.

- „Right the First Time, a Practical Handbook on High Speed PCB and System Design, Volumes 1 & 2“, Zasio and Ritchey, Speeding Edge 2003 und 2006.

Signalintegritätsprinzipien sowie Techniken für Übertragungsleitungen und ihre Abschlüsse korrekt anzuwenden, ist eine Aufgabe für sich. Mit der richtigen Design-Software kann Ihnen ein Großteil der Arbeit abgenommen werden, und zwar von Anfang an, wenn Sie die richtigen Designregeln programmieren und über geeignete Tools zur Signalintegritätsanalyse verfügen. Stellen Sie sicher, dass Sie Design-Software verwenden, die diese Arbeit für Sie erledigt.

Mit fortschrittlichen Design-Tools, einer einheitlichen Umgebung und branchenüblicher Regelüberprüfung können Sie in Altium Designer mühelos alles entwickeln, was Sie sich vorstellen können. Holen Sie sich Ihre kostenlose Testversion und probieren Sie es aus.