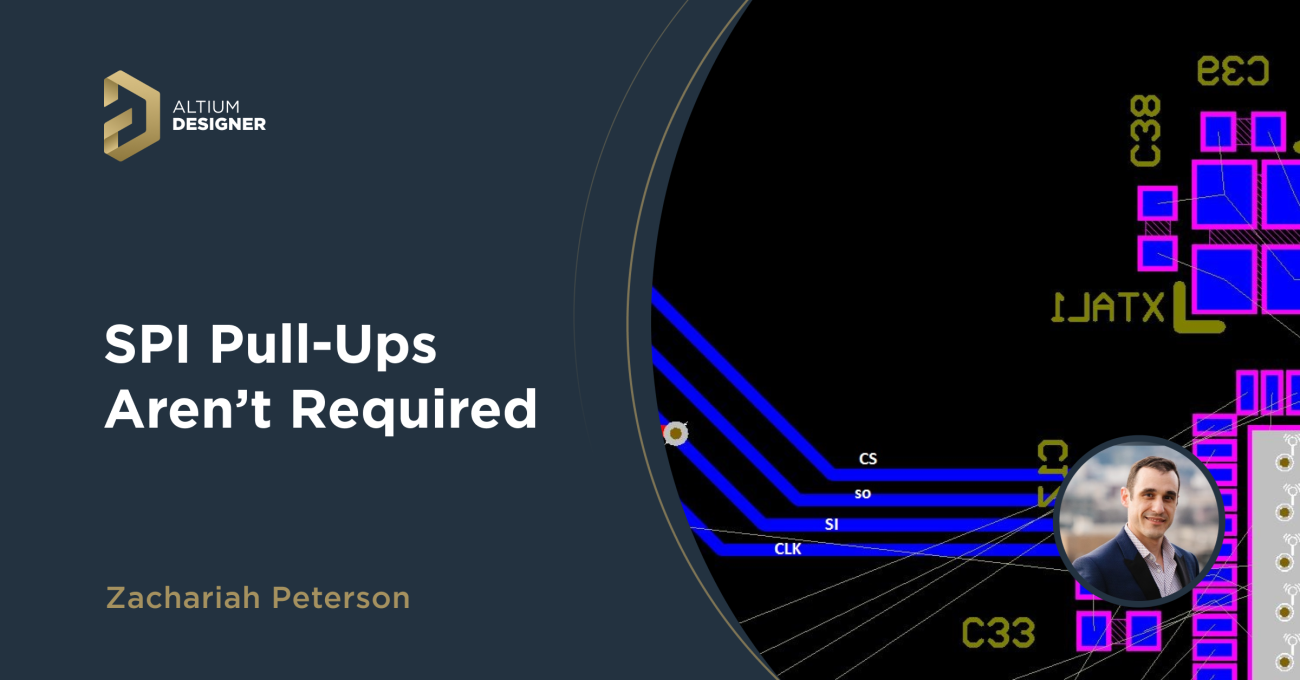

Sie benötigen nicht immer Pull-up-Widerstände auf SPI-Leitungen

Es gibt ein weit verbreitetes Missverständnis, dass Pull-Up-Widerstände auf den Leitungen eines SPI-Busses erforderlich oder notwendig sind. Ich bin hier, um Ihnen eindeutig zu sagen, dass Pull-Up-Widerstände auf einem SPI-Bus nicht erforderlich sind, um seine grundlegende Funktion des Sendens und Empfangens digitaler Daten zu erfüllen.

Der Puffer in einer SPI-Schnittstelle hat eine Push-Pull-Topologie, die (auf hoher Ebene) High-Side- und Low-Side-Schalt-MOSFETs umfasst und im Wesentlichen einen CMOS-Inverter bildet. Wie wir in diesem Artikel sehen werden, hat die Anwesenheit von Pull-Up-Widerständen keinen Einfluss auf die Funktionalität eines Push-Pull-Busses.

Das heißt, es gibt Fälle, in denen es sinnvoll ist, einen Pull-Up-Widerstand auf einem Push-Pull-Bus zu platzieren, und in einigen Datenblättern wird ein Bauteilhersteller dies empfehlen oder fordern. Wir werden uns diese Situationen ansehen und wie sie das Verhalten Ihres Systems beeinflussen. Obwohl es komplexere Lösungen geben kann, die den Bedarf an Pull-Up-Widerständen in diesen Situationen eliminieren, kann die Platzierung eines Pull-Up-Widerstands eine Lösung sein, die Ihr Design einfach hält und sicherstellt, dass die Schnittstelle korrekt funktioniert.

Wie ein SPI-Bus mit Pull-Up-Widerständen funktioniert

Lassen Sie uns das typische Modell eines Buffers in einer SPI-Schnittstelle betrachten. Alle SPI-Buffer haben eine Push-Pull-Topologie, die aus Hoch- und Niedrigseitenschaltung besteht, welche ein Signal auf den Bus treibt, und jedes Signal im SPI-Bus (CS, MOSI, MISO und SCLK) wird diese Topologie haben. Ein Beispiel für diesen Schaltkreis ist unten dargestellt. Beachten Sie, dass ein echter SPI-Buffer nicht so einfach wie zwei MOSFETs ist, aber die gleiche Idee gilt im Allgemeinen.

CMOS-Inverter als SPI-Treiber. Der Ausgang verbindet sich mit einer Leiterbahn (dargestellt als gebündelte Elemente) und einem Lastkreis (RC-Äquivalentmodell).

Der gesamte Grund für die Verwendung dieser Topologie ist, dass die entladenden Kapazitäten im Buffer-Schaltkreis angemessen schnelle Flankenraten am Ausgang ermöglichen, die viel kürzer als die Taktperiode auf dem Bus sein werden. Das ermöglicht schnellere Datenraten als ein Open-Drain-Protokoll (z.B. I2C).

Ein SPI-Bus, der Pull-up-Widerstände beinhaltet, ist im Wesentlichen ein CMOS-Invertertreiber mit einem Widerstand parallel zum High-Side-FET im Ausgangspuffer. Jetzt sehen wir uns an, was während jedes Schaltzustands im Treiber passiert und was auf dem Bus geschieht.

Logik HIGH Ausgang

Im Zustand des Logik HIGH Ausgangs ist der NMOS AUS und der PMOS EIN. VDDIO speist nun Strom in die verbundene Leiterbahn und Last ein. Die Kapazität in der Leiterbahn und der Last beginnt sich aufzuladen, bis die an der Last gesehene Spannung VDDIO entspricht. Hier ist der EIN-Widerstand des PMOS in der Größenordnung von mOhm, während der Pull-up-Widerstand in der Größenordnung von 1 bis 10 kOhm liegt. Offensichtlich ist der Pull-up-Widerstand so groß, dass er im Zustand des HIGH-Logikausgangs im Wesentlichen durch den PMOS kurzgeschlossen wird.

Da der gesamte Strom im HIGH-Logikzustand unabhängig von der Anwesenheit des Pull-up-Widerstands durch den PMOS fließt, werden die Schaltcharakteristiken nicht beeinflusst.

Logik LOW Ausgang

Nun betrachten wir, dass der Schaltkreis in den Zustand mit logisch NIEDRIGEM Ausgang gewechselt hat. In diesem Zustand ist der NMOS EIN und der PMOS AUS, sodass die Leiterbahn und die Lastkapazität über den NMOS in das GND-Netz entladen werden. Da der PMOS ausgeschaltet ist, erscheint er als ein sehr hoher Widerstand (in der Größenordnung von MOhm), der viel größer ist als der Wert des Pull-up-Widerstands (1 bis 10 kOhm).

Da der Pull-up in diesem Fall der kleinere Widerstand ist, wird er einen Stromwert von VDDIO/R(pu) zum NMOS fließen lassen. Für einen Pull-up-Widerstand von 1 bis 10 kOhm und VDDIO = 3,3 V wäre der Leckstrom in den NMOS 0,33 bis 3,3 mA. Das ist viel kleiner als der typische SPI-Strom von ~50 mA, also werden wir wiederum keine Auswirkungen auf die Schaltcharakteristiken bemerken. Die Abfallzeit auf dem Bus wird durch die Last- und Leiterbahnkapazitäten, die ausgangsseitige resistive Impedanz des Pufferkreises und den EIN-Zustandswiderstand des NMOS begrenzt.

Wenn das Schalten nicht beeinflusst wird, warum verwendet man dann einen Pull-up?

Offensichtlich beeinflusst die Platzierung eines Pull-Up-Widerstands an einer SPI-Leitung nicht dessen Fähigkeit, ein Signal auf den Bus zu treiben. Daher sollte der Pull-Up eine andere Funktion erfüllen, die nicht mit der Datenübertragung zusammenhängt, sonst würde der Widerstand nicht verwendet werden.

Die Gründe für die Verwendung eines Pull-Up-Widerstands an einer oder mehreren Leitungen in einer SPI-Schnittstelle variieren je nach der vorgeschlagenen Situation. Einige Situationen, in denen Pull-Up-Widerstände verwendet werden, umfassen:

- Platzierung an der CS-Leitung für ein Peripheriegerät

- Platzierung an der MISO-Leitung für ein Host-Gerät

- Platzierung an der MOSI-Leitung für ein Peripheriegerät

- Platzierung an allen Busleitungen in der Nähe der Ausgangspins

Die angegebene Begründung für die Platzierung in einer dieser Situationen besteht darin, den Logikzustand an einer der peripheren Komponenten im Bus zu setzen. Die häufigste Empfehlung ist, einen Pull-Up-Widerstand am CS-Pin eines Peripheriegeräts zu platzieren, um ihn hochzuziehen. Wenn das Peripheriegerät einen aktiven Low-Enable-Pin hat, dann wird dies den Pin immer hochziehen, es sei denn, die Treiberseite des Pulls setzt den Pin niedrig.

Ein Beispiel für eine solche Verwendung wird unten gezeigt. Im PCB-Layout würde der Pull-Up-Widerstand nahe am CS-Pin dieses Peripheriegeräts platziert werden.

Typische Platzierung eines Pull-Up-Widerstands am CS-Pin eines SPI-Busses.

Warum wird dies verwendet? Der angegebene Grund ist, dass während des Systemstarts der CS-Pin in einem beliebigen Zustand schweben könnte und dies ein Risiko darstellen würde, dass Störungen die Daten auf dem Bus verfälschen können. Darüber hinaus, wenn das Host-Gerät vor dem Peripheriegerät startet und der CS-Pin unbeabsichtigt aktiviert wird, könnte der Host beginnen, Daten im Peripheriegerät zu manipulieren. Dies wird manchmal als Grund angeführt, einen Pull-Up-Widerstand an Speicherperipheriegeräten zu platzieren.

Bis heute kann ich keinen überzeugenden Grund finden, einen Pull-Up-Widerstand an der SCLK (Clock)-Leitung zu platzieren. Der Grund ist, dass die empfangende Logikschaltung nicht umschalten wird, wenn andere Bedingungen (speziell der Zustand der CS-Leitung) nicht erfüllt sind, unabhängig von der Anwesenheit eines Clock-Signals. Einige Anwendungshinweise und Datenblätter empfehlen die Pull-Up-Widerstände für MISO oder MOSI aus verschiedenen Gründen, aber zu testen, ob dies funktioniert, ist einfach und der Widerstand kann immer entlötet werden, wenn Sie an Ihrem Prototyp arbeiten.

Leistungssequenzierung ist eine aufwendigere Lösung

Da dies am häufigsten als Problem mit dem Zustand des CS-Pins während des Systemstarts genannt wird, denke ich, dass die Leistungssequenzierung zwischen Peripheriegeräten und dem Systemhost der beste Ansatz wäre, um dieses Problem beim Start zu verhindern. In kleineren Systemen ist möglicherweise kein Platz im Gerät für mehrere Regler oder für einen Leistungssequenzer verfügbar, der die erforderliche Leistung durchschalten kann. Eine einfachere Lösung ist das Platzieren eines Pull-up-Widerstands, aber verstehen Sie, dass diese Pull-up-Widerstände nicht erforderlich sind, damit die Schnittstelle korrekt funktioniert.

Ob Sie zuverlässige Leistungselektronik oder fortschrittliche digitale Systeme bauen müssen, nutzen Sie den kompletten Satz an PCB-Designfunktionen und Weltklasse-CAD-Tools in Altium Designer. Um die Zusammenarbeit in der heutigen fachübergreifenden Umgebung zu implementieren, nutzen innovative Unternehmen die Altium 365-Plattform, um Design-Daten einfach zu teilen und Projekte in die Fertigung zu bringen.

Wir haben nur an der Oberfläche dessen gekratzt, was mit Altium Designer auf Altium 365 möglich ist. Starten Sie heute Ihre kostenlose Testversion von Altium Designer + Altium 365.