Qué especificar para la integridad del canal: listas de verificación prácticas para enlaces de alta velocidad

La mayoría de los equipos descubren problemas de integridad de canal durante la puesta en marcha: un diagrama de ojo que se veía limpio en simulación se cierra en el banco de pruebas, un conector que estaba especificado para la velocidad de datos falla en la topología real, o un cambio en el stackup provoca una pérdida de margen que nadie había contemplado. Cada uno de estos casos es una falla de especificación que se manifiesta como una falla de integridad de señal (SI). La solución es definir la integridad de canal como un conjunto de requisitos medibles con suficiente antelación como para influir en la arquitectura, y luego verificar esos requisitos en cada fase del diseño.

Conclusiones clave

- La integridad de canal es, ante todo, un problema de requisitos. El margen se gana o se pierde con la topología, el stackup y las decisiones de interconexión.

- Los retimers, redrivers, conectores y cables consumen cada uno una parte de tu presupuesto de canal. Especifícalos con valores de IL, RL, diafonía y jitter que se relacionen directamente con el margen de tu enlace.

- Un plan de medición forma parte de la especificación del canal. La estrategia de fixtures y el de-embedding deben definirse antes de cerrar el layout.

Qué abarca realmente la integridad de canal

Un canal de alta velocidad abarca toda la trayectoria eléctrica desde los pines del transmisor hasta los pines del receptor, incluidos los breakouts del encapsulado, vías, transiciones entre planos de referencia, trazas, conectores, cables y cualquier acondicionamiento activo a lo largo del recorrido. La integridad de canal es la capacidad de esa trayectoria para cumplir una tasa objetivo de error de bit (BER) en condiciones de voltaje, temperatura, variación de proceso y condiciones reales de interconexión. Tu topología, componentes y método de validación deben sostenerse, y los resultados deben ser reproducibles.

Cada elemento de la trayectoria consume una parte del presupuesto de margen. Cuando cualquiera de ellos está insuficientemente especificado, los problemas aparecen tarde y el ciclo de depuración se vuelve costoso. En este artículo presentamos un proceso de ocho pasos para ayudarte a entender qué especificar, cómo especificarlo y qué exigir a los proveedores de componentes para que tus resultados de simulación y laboratorio converjan. Además, proporcionamos listas de verificación prácticas para cada paso del proceso.

Para una mirada más detallada de cómo PCIe 7.0, Ethernet 800G, USB4 y Wi-Fi 7 están impulsando estos requisitos aguas arriba, consulta Los estándares de alta velocidad siguen elevando el listón.

Paso 1. Define el enlace que realmente estás construyendo

Comienza con un bloque breve de definición del enlace que se incluya en tus requisitos y en tu plan de pruebas.

Lista de verificación para la definición del enlace

- Estándar y objetivo de velocidad (ejemplo: PCIe, Ethernet, USB4 o un SerDes propietario).

- Número de lanes y expectativas de lane bonding.

- Alcance y topología. Solo en placa, placa a placa, con cable o flyover.

- Presupuesto de latencia (especialmente si podrías añadir retimers).

- Restricciones de potencia y térmicas en las ubicaciones probables de acondicionamiento.

- Restricciones ambientales y mecánicas (vibración, acceso para servicio).

Estas decisiones forman la línea base de requisitos para cada elección posterior. Fíjalas pronto y mantenlas en tu plan de pruebas.

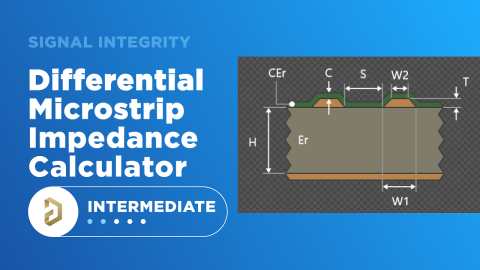

Paso 2. Construye un presupuesto antes de comenzar el layout

Un presupuesto de canal es la columna vertebral de la especificación. Convierte las suposiciones optimistas en cifras concretas que tu stackup, tus elecciones de conectores y tu plan de acondicionamiento realmente puedan cumplir.

Elementos del presupuesto que debes incluir

- Pérdida por inserción (IL) en función de la frecuencia.

- Pérdida por retorno (RL) en función de la frecuencia.

- Objetivos de diafonía: NEXT, FEXT y métricas de modo mixto (si las utilizas).

- Presupuesto de skew: incluyendo las contribuciones del tejido de vidrio y de los conectores.

- Objetivos de conversión de modo porque la energía en modo común suele manifestarse como EMI.

- Suposiciones del presupuesto de jitter y cuánto esperas recuperar mediante ecualización.

Si no puedes expresar un requisito como una línea de presupuesto y un plano de referencia, no podrás validarlo de forma limpia.

Paso 3. Retimers. Qué especificar cuando necesitas CDR

Cuando necesitas recuperación de reloj y datos (CDR), un retimer proporciona un punto de reinicio dentro del canal. Retransmite una versión limpia de la señal, restaurando margen que la ecualización por sí sola no puede recuperar. Esa capacidad viene con restricciones de diseño que debes especificar desde el principio.

Lista de verificación de especificación para retimers

- Velocidades de datos y protocolos compatibles.

- Número de lanes y flexibilidad de mapeo de lanes.

- Latencia (típica y en el peor caso).

- Tolerancia al jitter y comportamiento de transferencia de jitter (cómo el dispositivo filtra o deja pasar el jitter).

- Comportamiento y controles de ecualización: presets estáticos frente a comportamiento adaptativo; cómo se configura y supervisa.

- Estados de potencia y características térmicas.

- Requisitos de reloj de referencia, si los hay.

- Requisitos de la trayectoria de señal: expectativas de acoplamiento AC, restricciones de escape del encapsulado y guía de ruteo.

- Disponibilidad de modelos: IBIS-AMI cuando corresponda, además de diseños de referencia y material de evaluación.

Retimer destacado

Broadcom BCM85667 es un retimer PCIe Gen 6 y CXL 3.1 de 16 lanes, fabricado en 5 nm, que opera a 64 GT/s PAM4. Su resumen del producto documenta las velocidades de datos compatibles, opciones de bifurcación, controles de EQ y compatibilidad de huella. Ese es el nivel de detalle de especificación que deberías esperar de cualquier retimer que evalúes.

Paso 4. Redrivers. Qué especificar cuando quieres EQ lineal

Un redriver proporciona ecualización lineal y acondicionamiento de salida. No realiza recuperación de reloj. Esa compensación normalmente implica menor latencia y una integración más sencilla, con menor capacidad para rehabilitar un canal seriamente degradado.

Lista de verificación de especificación para redrivers

- Velocidad de datos y ancho de banda compatibles.

- Rango de ecualización y tamaño de paso.

- Rango de swing de salida y controles de ganancia plana.

- Comportamiento de ruido y linealidad, especialmente si podrías amplificar ruido junto con la señal.

- Sensibilidad de entrada y manejo del modo común.

- Interfaz de configuración y telemetría.

- Restricciones de encapsulado y escape.

- Disponibilidad de modelos y guía de layout de referencia.

Redriver destacado

PI3EQX32908ZRIEX de Diodes es un redriver lineal PCIe 5.0 de 8 canales compatible con 5 a 32 Gbps, con EQ programable por canal, swing de salida y controles de ganancia plana; también admite los protocolos SAS4 y CXL.

Paso 5. Los conectores como componentes del canal

A altas velocidades, el conector y sus transiciones pueden consumir una parte desproporcionada del margen, por lo que merecen el mismo rigor de especificación que cualquier otro componente del canal.

Lista de verificación de especificación para conectores

- Objetivo de impedancia diferencial y tolerancia.

- IL y RL en función de la frecuencia para el par acoplado y para las transiciones en la PCB.

- Comportamiento de diafonía y guía de aislamiento del campo de pines.

- Opciones de altura de apilado y acumulación de tolerancias.

- Ciclos de acoplamiento y supuestos de durabilidad mecánica.

- Restricciones de huella de PCB y breakout.

- Disponibilidad de parámetros S y cualquier guía de diseño de referencia.

- Plan de segunda fuente a nivel de interfaz.

Conectores destacados

Molex Mirror Mezz 202828-1506 es un conector mezzanine placa a placa hermafrodita con 404 circuitos, altura de apilado de 2,50 mm y montaje BGA, compatible con velocidades de datos de hasta 56 Gbps por par diferencial. Utiliza una huella recomendada por OCP compartida en toda la familia Mirror Mezz, lo que te proporciona datos de parámetros S, documentación de huella y visibilidad de distribuidores que puedes adjuntar a tu modelo de canal y a la revisión de BOM.

Paso 6. Cables y flyovers: especifica la extensión del canal

Los conjuntos de cables de cobre y los flyovers ópticos activos amplían el alcance del canal más allá de lo que pueden ofrecer las trazas en placa, pero resuelven problemas distintos. Los cables de cobre se comportan como líneas de transmisión con restricciones de impedancia, apantallamiento y radio de curvatura. Los flyovers ópticos evitan por completo la pérdida dieléctrica, pero introducen consideraciones de conversión electroóptica, potencia, térmicas y de latencia. Especifica el enfoque que requiera tu presupuesto de enlace y define qué significa un rendimiento equivalente para cualquier alternativa que consideres.

Lista de verificación de especificación para cables

- Impedancia diferencial y skew.

- IL y RL en función de la frecuencia, incluidas las transiciones en cada extremo.

- Eficacia del apantallamiento y enfoque de puesta a tierra.

- Restricciones de radio de curvatura y alivio de tensión.

- Requisitos de ciclos de acoplamiento y acceso para servicio.

- Comportamiento pasivo frente a activo, si corresponde. Para flyovers ópticos, especifica longitud de onda, presupuesto de potencia óptica, latencia y consumo de potencia por lane.

- Requisitos de calificación y lista de cables aprobados.

Conjunto flyover óptico activo destacado

Samtec ECUO-B04-14-015-0-2-1-2-01 (el FireFly ECUO) es un conjunto flyover óptico activo disponible como transceptor full-duplex de 4 canales a 28 Gbps por canal, o como transmisor o receptor de 12 canales a 16 Gbps por canal. Con fibra multimodo OM3, puede alcanzar hasta 100 metros. Evita por completo la pérdida en trazas de PCB y utiliza el mismo sistema de microconector que los conjuntos flyover de cobre de Samtec, por lo que la huella se mantiene igual si cambias entre óptico y cobre.

Paso 7. Materiales de baja pérdida y cobre: incluye el stackup en la especificación

Los enlaces de mayor ancho de banda requieren que el stackup sea una entrada de diseño controlada. La especificación de tu canal debe incluir objetivos de material y rangos aceptables, y debe indicar explícitamente qué estás asumiendo sobre la rugosidad del cobre y la capacidad del proceso.

Lista de verificación de especificación para materiales y stackup

- Objetivos de Dk y Df en las frecuencias relevantes, además de la variación permitida.

- Suposiciones sobre el perfil de la lámina de cobre cuando la pérdida del conductor es el factor limitante.

- Controles del riesgo por tejido de vidrio y skew para recorridos diferenciales largos.

- Tg, Td y CTE en eje Z si tu entorno o perfil de ensamblaje es exigente.

- Suposiciones sobre la capacidad del fabricante: relaciones de aspecto de taladrado, registro, relleno de vías y ciclos de laminación.

- Fija el sistema de laminado y exige una revisión explícita antes de cualquier sustitución.

Laminados de baja pérdida destacados

Las familias de laminados MEGTRON 7 de Panasonic e I-Tera MT40 de Isola son ejemplos representativos de materiales de pérdidas ultrabajas y muy bajas utilizados en canales digitales de alta velocidad. Use estos productos como puntos de referencia para definir lo que espera de cualquier laminado que seleccione: datos eléctricos estables, orientación de proceso y una identidad de producto clara que pueda fijar en las notas de fabricación.

Paso 8. Plan de medición. Haga de la correlación el objetivo

Su plan de medición necesita planos de referencia definidos, fixtures, calibración y de-embedding, para que pueda comparar los resultados de simulación con los datos de banco sin ambigüedades. IEEE 370-2020 es una referencia práctica para este trabajo, ya que cubre la calidad de los datos, las consideraciones sobre fixtures y el de-embedding para la caracterización de PCB e interconexiones hasta 50 GHz.

Lista de verificación del plan de medición

- Qué medirá: TDR para el perfil de impedancia, parámetros S de VNA para segmentos de interconexión, y diagrama de ojo o jitter en puntos definidos.

- Dónde medirá: Defina los planos de referencia y asígneles un nombre.

- Cómo calibrará: Indique el método de calibración y la trazabilidad.

- Cómo realizará el de-embedding: Elija métodos que pueda ejecutar con sus fixtures y herramientas.

- Cómo correlacionará: Defina criterios de aceptación para la alineación entre simulación y medición.

Plataforma de medición destacada

Los analizadores de redes Keysight PNA-X cubren rangos de frecuencia desde 900 Hz hasta 67 GHz (según el modelo), con múltiples fuentes internas, receptores de parámetros S y de ruido, y compatibilidad con el software PLTS de Keysight para caracterización de interconexiones y de-embedding.

Dónde encaja Octopart en el flujo de trabajo

Las piezas relacionadas con la integridad de canal suelen tener menos alternativas reales. Las familias de conectores, los CI especializados de acondicionamiento y ciertos conjuntos de cables pueden convertirse en los componentes que retrasan una fabricación. Use Octopart y la herramienta BOM para mantener conectados tres elementos mientras el diseño aún es flexible:

- El número de pieza y el estado de ciclo de vida actualizado.

- La documentación de soporte: hojas de datos, modelos y diseños de referencia.

- Productos alternativos y opciones de proveedores antes de que las huellas y las interfaces queden definidas.

Cuanto antes incorpore datos reales de componentes a su modelo de canal, menos suposiciones llegarán al layout. Un archivo de parámetros S de un conector, una ficha técnica resumida de un retimer o una tabla Dk/Df de un laminado valen más que un marcador de posición y un plan para definirlo todo más adelante. Octopart le ofrece un lugar práctico para comprobar disponibilidad, obtener hojas de datos y confirmar el estado del ciclo de vida mientras el diseño todavía es lo bastante flexible como para absorber lo que encuentre.

La disciplina que evita re-spins

La integridad de canal se construye mediante un conjunto de decisiones que se toman durante la arquitectura, el stackup y la selección de interconexiones, y luego se verifica mediante simulación, medición y correlación antes y después del layout. El hilo conductor en todo esto es el mismo: defina lo que necesita, especifíquelo con números, elija componentes que vengan con datos que respalden esos números y redacte el plan de medición antes de que el layout quede cerrado. Los equipos que hacen esto de forma consistente son los que evitan una nueva iteración de la placa.