Aspectos básicos del análisis de integridad de la señal en tu PCB

Los fundamentos del análisis de la integridad de la señal en una PCB pueden ser cualquier cosa menos básicos. Las herramientas de simulación de la integridad de la señal son excelentes para calcular el comportamiento de las señales en diferentes redes durante el diseño esquemático y de maquetación, pero, incluso en ese caso, tendrás que seguir algunos pasos para interpretar los resultados. Por muy avanzadas que puedan llegar a ser algunas herramientas de simulación de la integridad de la señal y de EM, no se pueden comparar con la información que puedes obtener de las mediciones. Sea cual sea el método que utilices para examinar la integridad de la señal en tu placa de PCB (yo te recomiendo utilizar ambos), hay algunos pasos importantes que puedes seguir para analizar el comportamiento de las señales e identificar problemas en la placa de circuito impreso.

Introducción al análisis de integridad de la señal

El análisis de integridad de la señal empieza con simulaciones en la fase previa al diseño. Una vez creado el diseño, puedes utilizar algunas simulaciones importantes posteriores al diseño para analizar la integridad de la señal de la placa en función de la geometría. En algún momento, tendrás que comparar los resultados de la simulación de la integridad de la señal con las mediciones reales, así que ten los resultados a mano para poder compararlos.

Análisis previos al diseño de PCB

Esta parte trata principalmente del diseño de circuitos, selección de componentes y la forma en que las señales viajan entre las E/S de dos componentes. Hay tres análisis importantes que te proporcionan una cantidad significativa de información sobre el comportamiento de la placa de PCB.

-

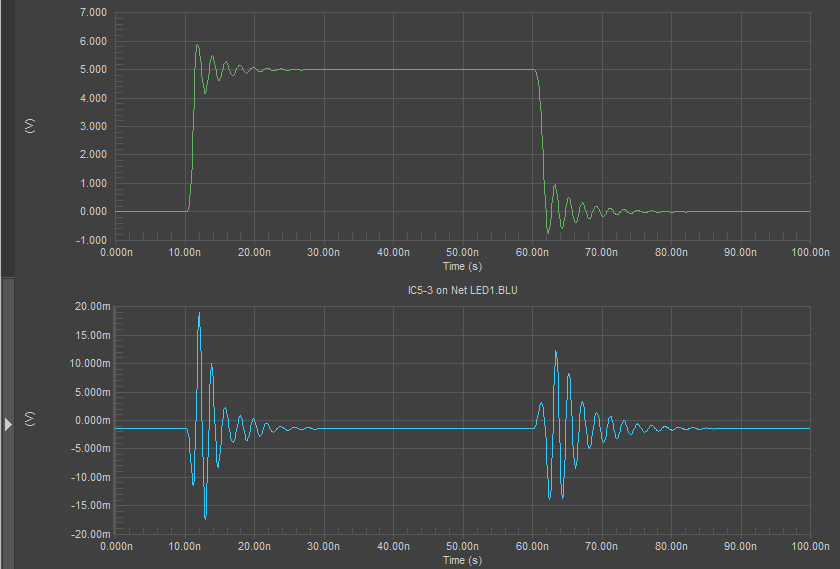

Comportamiento transitorio. Las respuestas transitorias en la conexión entre dos zonas de búfer también pueden modelarse en el tiempo utilizando el análisis transitorio, o puedes determinar el comportamiento de los transitorios a partir de análisis de polos y ceros. Esto te mostrará el sobreimpulso o subimpulso debido a la sobreoscilación y la aproximación al nivel de señal deseado. Las versiones más precisas de estas simulaciones con circuitos integrados implican modelos IBIS, aunque podrían utilizarse subcircuitos SPICE para modelar búferes de E/S.

-

Parámetros S y función de transferencia. Ciertos bloques funcionales de la placa de circuito impreso se pueden modelar como redes multipuerto, lo que significa que su comportamiento lineal se puede describir en términos de parámetros S a una frecuencia determinada. Puedes determinar los parámetros S a partir de un coeficiente de reflexión en el dominio del tiempo, que en las líneas de transmisión implica la impedancia de entrada dada por la capacitancia de carga. Puedes calcular la función de transferencia para tu red a partir de los parámetros S, y viceversa. Esta es una guía excelente que indica todos los cálculos matemáticos necesarios.

-

Respuesta al impulso. Esta simulación tiene dos objetivos: evaluar la causalidad de los modelos de parámetros S y de la función de transferencia en un ancho de banda definido y examinar el comportamiento de la respuesta al impulso para un tiempo de subida determinado. Las respuestas al impulso también te permiten extraer la dispersión y el retardo de propagación a lo largo del diseño de interconexión. Esto cualifica un modelo de canal previsto para un par de búfer de entrada/salida determinado en una situación ideal antes de diseñar la PCB.

-

Diagrama de ojo. Los modelos de búfer y el diseño de interconexión pueden utilizarse para simular un diagrama de ojo. El diagrama de ojo es una parte importante del cumplimiento del canal, ya que mostrará el nivel de señal, el sobreimpulso, la interferencia entre símbolos (ISI), la fluctuación y la tasa de error de binario esperados bajo una secuencia de bits pseudoaleatoria.

En canales más complejos, el conjunto anterior de análisis previos al diseño puede ayudarte a cualificar aspectos como las transiciones de vía planificadas,

Siempre que conozcas la estructura de cada uno de estos elementos antes de crear el diseño, puedes

Análisis posteriores al diseño de PCB

Esta parte trata principalmente de examinar cómo influyen los efectos parásitos de la placa a la integridad de la señal. Como los efectos parásitos de integridad de la señal son funciones de la geometría de la placa, deberás examinar los siguientes problemas de integridad de la señal que dependen de la geometría:

-

Diafonía. La diafonía, la pesadilla de muchos diseñadores, surge del acoplamiento inductivo y capacitivo. Si estás examinando los efectos de la diafonía en pistas víctima y agresor, el acoplamiento capacitivo solo se producirá cuando ambas sean adyacentes. La diafonía inductiva no está limitada por el alcance y todas las pistas de tu placa pueden acoplarse entre sí a través del campo magnético.

-

Comportamiento de la línea de transmisión. Si bien puedes utilizar modelos de líneas de transmisión para examinar las pistas de señales durante la fase previa al diseño de PCB, lo mejor es hacerlo directamente desde el diseño. Si tus líneas no tienen impedancia controlada, tendrás que comprobar si los reflejos en la línea (si los hay) degradan los niveles de señal en el receptor y provocan una respuesta escalonada con las señales digitales. Con señales analógicas, esto puede ser más complicado, ya que lo que estás buscando son interferencias y la formación de ondas estacionarias en la línea. Sin embargo, un simulador de integridad de señal adecuado puede separar las ondas incidentes de las reflejadas, lo que te permite examinar el comportamiento de cada una de ellas de forma individual. Luego podrás determinar el nivel de reflexión y comprobar si el nivel de la señal cumple con tus requisitos de señalización.

-

Todo lo que examinaste antes del diseño. De lo que se trata aquí es de comprobar que los efectos parásitos, la trama de fibras, etc., no alteren drásticamente el comportamiento de las señales en tu placa. Si fallan varias pistas, será necesario modificar el diseño. El primer punto de partida es la geometría de los stackups y de las pistas.

Herramientas para análisis de integridad de la señal

Los puntos anteriores podrían dar la impresión de que vas a necesitar un complejo programa de simulación para construir y poner en marcha todas estas herramientas de análisis de la integridad de la señal. Las herramientas específicas que necesites para el análisis de la integridad de la señal dependerán de lo que desees simular y evaluar. Dentro de la herramienta EDA, algunas de estas simulaciones pueden llevarse a cabo simplemente con algo como la IBIS, mientras que las simulaciones más complejas con múltiples redes podrían requerir de una calculadora de campos en 3D o de una calculadora comparable en 2D.

Buses de un solo extremo sin especificación de impedancia

En los buses más lentos de salida simple sin terminación, es posible observar cierto comportamiento transitorio (sobreoscilación) que podría deberse a la estructura de la interconexión (su capacitancia e inductancia). Esto es algo que se puede observar en la SPI cuando la pista es eléctricamente corta. En estos buses, es posible comprobar la sobreoscilación previamente al diseño siempre que tengas un modelo de línea de transmisión aplicado en tus esquemáticos y siempre que esté definida la especificación de los pines (ya sea un subcircuito SPICE o un modelo IBIS).

Cuando el bus de un solo extremo esté enrutado, podrás llevar a cabo una simulación posterior al diseño con el analizador de integridad de señal de tus herramientas EDA. Estos analizadores de integridad de la señal pueden utilizar una asignación de familia lógica o un modelo IBIS para simular los pines y redes relevantes:

- Formas de onda de diafonía e identificación de regiones de acoplamiento fuerte.

- Formas de onda de reflexión.

- Otras métricas de comportamiento de la señal (tiempo de subida/bajada, sobreimpulso/subimpulso, etc.).

- Cálculo de la impedancia media a lo largo de la longitud de la pista.

En los buses de salida simple sin especificación de impedancia, es posible observar reflexiones en el extremo del controlador cuando el bus se alarga o sobreoscilaciones debidas a la capacitancia e inductancia del bus. Si la sobreoscilación produce un aumento excesivo, reducir la inductancia de la pista y añadir amortiguación son las dos formas principales de atenuar la amplitud de la sobreoscilación. Otra opción es aumentar la amortiguación añadiendo una resistencia en serie, algo que harías con la salida de un búfer de baja impedancia a una línea de transmisión desajustada más larga.

Buses de impedancia controlada

En los buses de salida simple y diferenciales de impedancia controlada, la impedancia de terminación podría estar en el chip, por lo que una simulación basada en la familia lógica posterior al diseño no es eficaz, ya que no describe correctamente la impedancia del bus. Todavía es posible simular la diafonía, puesto que solo estás observando el acoplamiento entre dos interconexiones en función del tiempo de subida, y la magnitud de la diafonía aumentará en proporción inversa al tiempo de subida en consecuencia, aunque solo asignes una familia lógica.

En el caso de una simulación posterior al diseño para reflexiones y violaciones de impedancia, esta debe al menos utilizar modelos IBIS para definir el comportamiento del búfer en lugar de depender de descripciones de familias lógicas. Siempre que la descripción del búfer sea conocida y esté disponible, se puede aplicar para modelar el comportamiento del componente en el editor de PCB. La herramienta de análisis de la integridad de señal estándar en un editor de PCB para formas de onda de diafonía y reflexión puede ayudar mucho en la calificación inicial del comportamiento de la señal (tiempo de subida/bajada, sobreimpulso, diafonía, impedancia constante y sobreoscilación) antes de pasar a una herramienta de análisis de integridad de la señal más avanzada.

Para simular aspectos como los diagramas de ojo, la diafonía entre varias redes y las desviaciones de impedancia a lo largo de una red, tienes a tu disposición herramientas externas. Las calculadoras de campo son una opción, y muchas de estas herramientas están disponibles con diferentes niveles de especialización. No siempre es necesario disponer de una calculadora de campo de onda completa, a menos que quieras simular emisiones radiadas o algo más profundo con SI/PI o extraer parámetros S en la red simulada.

Las potentes herramientas de diseño y análisis de PCB de Altium Designer® te proporcionan un punto de partida útil para el análisis de integridad de la señal con herramientas de simulación de integridad de la señal previas y posteriores al diseño. Estos cálculos precisos te ofrecen una referencia para comparar tus mediciones. También tendrás acceso a un conjunto completo de funciones para la planificación de la fabricación y la documentación en una única plataforma.

Ahora ya puedes descargarte una versión de prueba gratuita de Altium Designer y descubrir cómo funcionan las mejores herramientas del sector para diseño, simulación de la integridad de la señal y planificación de la producción. Habla con un experto de Altium hoy mismo para obtener más información sobre Altium Designer.