Qu'est-ce que la norme JESD204C pour les ADC/DAC ?

JESD204C fournit une interface standardisée pour les ADC RF à taux d'échantillonnage élevé, qui apparaissent désormais plus fréquemment dans les applications spatiales commerciales.

Les interfaces série ont eu du mal à suivre le rythme des besoins des composants de conversion de données à taux d'échantillonnage élevé, à savoir les ADCs et les DACs. Une option pour cela était autrefois les liens LVDS entre les convertisseurs de données et un contrôleur hôte. Ces liens fourniraient des débits de données élevés sur des paires différentielles à un seul appareil, offrant un transfert de données à haut débit à partir d'ADCs à échantillonnage rapide. Plus tard, la JEDEC a publié la spécification JESD204, et elle a depuis été incorporée dans de nombreux composants comme une interface de convertisseur de données.

La version la plus récente des normes d'interface JESD204, actuellement JESD204C, apporte des débits de données extrêmes aux composants ADC/DAC rapides qui sont utilisés pour échantillonner des signaux à des taux d'échantillonnage très élevés. Maintenant que la dernière itération de la norme existe depuis un peu plus de 2 ans, de nombreux composants disponibles peuvent être utilisés avec des FPGAs pour fournir un échantillonnage ultra-rapide, une transmission et un DSP dans les systèmes RF.

Aperçu de JESD204C

La norme JESD204C est la dernière itération de la norme générale JESD204, qui est publiée et maintenue par JEDEC. Cette norme a été développée pour remplacer l'utilisation de liens LVDS entre les convertisseurs de données et leurs hôtes systèmes. Elle définit une interface série et un protocole utilisés dans les ADC/DAC à taux d'échantillonnage élevé pour l'échantillonnage de signaux, la synthèse et la synchronisation. L'aspect de synchronisation est important pour cette interface car elle permet à un seul contrôleur hôte de synchroniser l'échantillonnage de signaux et la synthèse à travers plusieurs dispositifs.

Certains des principaux paramètres opérationnels implémentés dans la couche physique sont listés dans le tableau ci-dessous. L'itération actuelle JESD204C améliore le débit de données et les caractéristiques de codage de l'itération précédente JESD204B, qui utilisait un codage 8b/10b avec un débit de données maximal de 12,5 Gbps. Cette interface peut être trouvée dans les ADC/DAC qui fonctionnent de 100 MSps à 1 GSps ou plus.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Exemple de topologie

La topologie d'une interface JESD204C dépend de la Sous-classe de l'interface. JESD204B a introduit les Sous-classes 1 et 2 pour mettre en œuvre une stratégie de synchronisation connue sous le nom de latence déterministe. Cette stratégie permet d'atteindre la synchronisation entre les appareils en déterminant le déphasage entre les flux de données transmis au contrôleur hôte.

- Sous-classe 0 - Pas de support de latence déterministe (rétrocompatible avec JESD204A)

- Sous-classe 1 - Latence déterministe obtenue en utilisant un oscillateur de référence externe (SYSREF) comme signal de synchronisationSous-classe 2 - Latence déterministe obtenue en utilisant une broche SYNC entre le contrôleur hôte et l'ADC/DAC

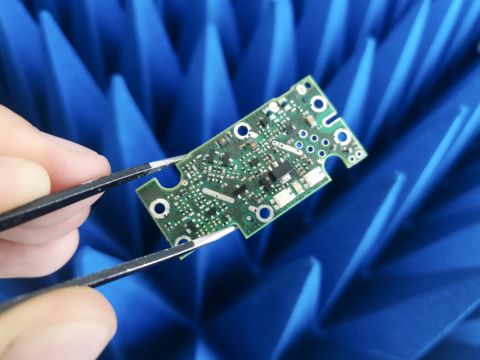

Deux implémentations de l'interface sont montrées dans le graphique ci-dessous.

DATA1 et DATA2 sont routés en tant que paires différentielles ; chaque voie dans ces groupes d'E/S est une paire différentielle et un dispositif donné peut avoir plusieurs voies (certains produits en ont jusqu'à 8 par dispositif). Dans les deux sous-classes, la source d'horloge est routée vers tous les dispositifs de manière source-synchrone. Le timing et la latence déterministe sont atteints dans chaque sous-classe par un appariement approprié de SYSREF et DCLK/SYNC aux temps de setup-et-hold, ainsi qu'entre eux lorsqu'ils sont distribués à travers plusieurs convertisseurs de données.

Routage, Désalignement et Latence

La latence déterministe a été mentionnée ci-dessus : c'est la technique par laquelle un seul contrôleur hôte peut synchroniser la collecte et la synthèse de données à travers plusieurs dispositifs avec un timing précis de sorte que le décalage de timing entre les cadres d'échantillonnage est connu. Ceci est corrigé en ajustant les retards des traces les uns par rapport aux autres de sorte que les retards entre eux sont appariés. Une interface JESD204B ou JESD204C utilise l'appariement des retards dans les bits de contrôle provenant de SYSREF (dans la sous-classe 1) ou des broches SYNC (dans la sous-classe 2).

Le tableau ci-dessous décrit les exigences d'appariement de longueur/délai dans les signaux de timing pour chaque sous-classe dans les interfaces JESD204B et JESD204C.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

La principale différence ici concerne le traitement des réseaux SYNC. Dans la Sous-classe 1, ces réseaux sont uniquement utilisés pour la synchronisation des groupes de codes, tandis qu'ils sont également utilisés pour le timing dans la Sous-classe 2. Par conséquent, JESD204C nécessite moins de signaux pour un nombre donné de canaux d'E/S dans les convertisseurs de données.

Pourquoi JESD204C plutôt que LVDS ?

L'avantage de l'interface JESD204C pour l'échantillonnage et la synthèse à haute vitesse à des fréquences en GHz est sa capacité à éliminer le décalage et le désaccord de latence à travers plusieurs convertisseurs. Il existe un budget de décalage pour toute interface JESD204, qui est la quantité maximale de décalage qui peut être compensée dans le schéma de synchronisation du système afin de garantir une latence déterministe dans les limites du bruit de phase. L'objectif est de s'assurer que le contrôleur hôte connaît les décalages de phase des flux de données entrants résultants et peut compenser cela en logique, établissant ainsi le véritable timing entre les signaux échantillonnés.

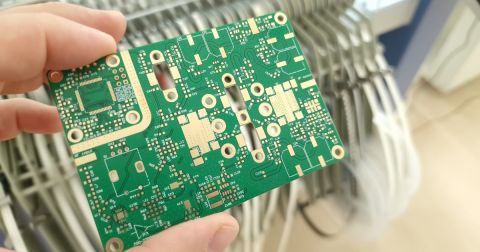

L'autre raison de l'utilisation de JESD204C est qu'elle réduit les exigences de routage et de timing dans la disposition du PCB. Dans une mise en œuvre typique, les paires différentielles DATA1 et DATA2 provenant du Dispositif 1 et du Dispositif 2 auront un certain décalage entre elles. Avec LVDS, cela nécessiterait des paires différentielles correspondantes se déroulant en parallèle l'une à l'autre. Dans JESD204C, nous avons seulement besoin d'éliminer le décalage à travers les réseaux DCLK et SYSREF/SYNC, mais pas les réseaux de données à travers les dispositifs. Cela rend l'interface essentielle dans les dispositifs à signaux mixtes de haute densité.

Les concepteurs développant des technologies avancées pour l'aérospatiale peuvent mettre en œuvre la norme JESD204C en utilisant les meilleurs outils de conception de produits de l'industrie dans Altium Designer®. Lorsque vous avez terminé votre conception et que vous souhaitez envoyer les fichiers à votre fabricant, la plateforme Altium 365™ facilite la collaboration et le partage de vos projets.

Nous n'avons fait qu'effleurer la surface de ce qui est possible avec Altium Designer sur Altium 365. Commencez votre essai gratuit d'Altium Designer + Altium 365 dès aujourd'hui.