Cosa specificare per l’integrità del canale: checklist pratiche per collegamenti ad alta velocità

La maggior parte dei team scopre i problemi di integrità del canale durante il bring-up: un eye diagram che in simulazione sembrava pulito si chiude sul banco, un connettore dichiarato idoneo alla velocità dati fallisce nella topologia reale, oppure una modifica allo stackup si traduce in una perdita di margine che nessuno aveva messo a budget. Ognuno di questi casi è un fallimento di specifica che si manifesta come un problema di signal integrity (SI). La soluzione è definire l’integrità del canale come un insieme di requisiti misurabili abbastanza presto da influenzare l’architettura, e poi verificare tali requisiti in ogni fase del progetto.

Punti chiave

- L’integrità del canale è prima di tutto un problema di requisiti. Il margine si guadagna o si perde con le scelte di topologia, stackup e interconnessione.

- Retimer, redriver, connettori e cavi consumano ciascuno una parte del budget del canale. Specificateli con valori di IL, RL, crosstalk e jitter che si colleghino direttamente al margine del link.

- Un piano di misura fa parte della specifica del canale. La strategia delle fixture e il de-embedding devono essere definiti prima che il layout venga congelato.

Cosa comprende davvero l’integrità del canale

Un canale ad alta velocità comprende l’intero percorso elettrico dai pin del trasmettitore ai pin del ricevitore, inclusi breakout del package, via, transizioni tra piani di riferimento, tracce, connettori, cavi ed eventuale condizionamento attivo lungo il percorso. L’integrità del canale è la capacità di quel percorso di soddisfare un bit error rate (BER) target in presenza di variazioni di tensione, temperatura, processo e condizioni reali di interconnessione. Topologia, componenti e metodo di validazione devono tutti reggere, e i risultati devono essere riproducibili.

Ogni elemento del percorso consuma una parte del budget di margine. Quando anche uno solo di essi è sottospecificato, i problemi emergono tardi e il ciclo di debug diventa costoso. In questo articolo presentiamo un processo in otto fasi per aiutarti a capire cosa specificare, come specificarlo e cosa pretendere dai fornitori di componenti affinché i risultati di simulazione e di laboratorio convergano. Inoltre, forniamo checklist pratiche per ogni fase del processo.

Per uno sguardo più approfondito su come PCIe 7.0, 800G Ethernet, USB4 e Wi-Fi 7 stiano spingendo questi requisiti a monte, vedi Gli standard ad alta velocità continuano ad alzare l’asticella.

Fase 1. Definisci il link che stai realmente progettando

Inizia con un breve blocco di definizione del link da includere nei requisiti e nel piano di test.

Checklist di definizione del link

- Standard e obiettivo di velocità (esempio: PCIe, Ethernet, USB4 o un SerDes proprietario).

- Numero di lane e aspettative di lane bonding.

- Portata e topologia. Solo on-board, board-to-board, cablato o flyover.

- Budget di latenza (soprattutto se potresti aggiungere retimer).

- Vincoli di potenza e termici nei probabili punti di condizionamento.

- Vincoli ambientali e meccanici (vibrazioni, accesso per manutenzione).

Queste decisioni costituiscono la baseline dei requisiti per ogni scelta successiva. Fissale presto e mantienile nel piano di test.

Fase 2. Costruisci un budget prima di iniziare il layout

Il budget del canale è la struttura portante della specifica. Trasforma ipotesi ottimistiche in numeri concreti che stackup, scelta dei connettori e piano di condizionamento possano davvero soddisfare.

Voci di budget da includere

- Insertion loss (IL) in funzione della frequenza.

- Return loss (RL) in funzione della frequenza.

- Obiettivi di crosstalk: NEXT, FEXT e metriche mixed-mode (se le utilizzi).

- Budget di skew: inclusi i contributi della glass weave e dei connettori.

- Obiettivi di conversione di modo perché l’energia di modo comune spesso si manifesta come EMI.

- Ipotesi sul budget di jitter e quanto ti aspetti che l’equalizzazione riesca a recuperare.

Se non riesci a esprimere un requisito come una voce di budget e un piano di riferimento, non riuscirai a validarlo in modo pulito.

Fase 3. Retimer. Cosa specificare quando serve il CDR

Quando hai bisogno di clock and data recovery (CDR), un retimer fornisce un punto di reset nel canale. Ritrasmette una versione pulita del segnale, ripristinando margine che la sola equalizzazione non può recuperare. Questa capacità comporta vincoli progettuali che devi specificare fin dall’inizio.

Checklist di specifica del retimer

- Velocità dati e protocolli supportati.

- Numero di lane e flessibilità nella mappatura delle lane.

- Latenza (tipica e worst-case).

- Tolleranza al jitter e comportamento di trasferimento del jitter (come il dispositivo filtra o lascia passare il jitter).

- Comportamento e controlli di equalizzazione: preset statici rispetto a comportamento adattivo; modalità di configurazione e monitoraggio.

- Stati di potenza e caratteristiche termiche.

- Requisiti del clock di riferimento, se presenti.

- Requisiti del percorso del segnale: aspettative di accoppiamento AC, vincoli di escape del package e linee guida di routing.

- Disponibilità dei modelli: IBIS-AMI dove pertinente, oltre a reference design e materiale di valutazione.

Retimer in evidenza

Broadcom BCM85667 è un retimer PCIe Gen 6 e CXL 3.1 a 16 lane, realizzato a 5 nm e operante a 64 GT/s PAM4. Il suo product brief documenta velocità dati supportate, opzioni di bifurcation, controlli EQ e compatibilità del footprint. Questo è il livello di dettaglio di specifica che dovresti aspettarti da qualsiasi retimer che intendi qualificare.

Fase 4. Redriver. Cosa specificare quando vuoi EQ lineare

Un redriver fornisce equalizzazione lineare e condizionamento dell’uscita. Non esegue il recupero del clock. Questo compromesso in genere significa latenza inferiore e integrazione più semplice, ma minore capacità di recuperare un canale seriamente degradato.

Checklist di specifica del redriver

- Velocità dati e larghezza di banda supportate.

- Intervallo di equalizzazione e dimensione dei passi.

- Intervallo di swing in uscita e controlli di flat gain.

- Comportamento di rumore e linearità, soprattutto se potresti amplificare il rumore insieme al segnale.

- Sensibilità in ingresso e gestione del modo comune.

- Interfaccia di configurazione e telemetria.

- Package e vincoli di escape.

- Disponibilità dei modelli e linee guida per il layout di riferimento.

Redriver in evidenza

PI3EQX32908ZRIEX di Diodes è un redriver lineare PCIe 5.0 a 8 canali che supporta da 5 a 32 Gbps con EQ programmabile per canale, swing in uscita e controlli di flat gain; supporta anche i protocolli SAS4 e CXL.

Fase 5. I connettori come componenti del canale

Alle alte velocità, il connettore e le sue transizioni possono consumare una quota sproporzionata del margine, quindi meritano lo stesso rigore di specifica di qualsiasi altro componente del canale.

Checklist di specifica del connettore

- Obiettivo di impedenza differenziale e relativa tolleranza.

- IL e RL in funzione della frequenza per la coppia accoppiata e per le transizioni PCB.

- Comportamento di crosstalk e linee guida per l’isolamento del campo pin.

- Opzioni di altezza stack e tolleranze cumulative.

- Cicli di accoppiamento e ipotesi di durabilità meccanica.

- Footprint PCB e vincoli di breakout.

- Disponibilità dei parametri S e di eventuali linee guida di reference design.

- Piano di second source a livello di interfaccia.

Connettori in evidenza

Molex Mirror Mezz 202828-1506 è un connettore mezzanino board-to-board ermafrodita con 404 circuiti, altezza stack di 2,50 mm e montaggio BGA-attach, che supporta velocità dati fino a 56 Gbps per coppia differenziale. Utilizza un footprint raccomandato da OCP condiviso in tutta la famiglia Mirror Mezz, offrendo dati S-parameter, documentazione del footprint e visibilità presso i distributori che puoi collegare al tuo modello di canale e alla revisione della BOM.

Fase 6. Cavi e flyover: specifica l’estensione del canale

Gli assiemi di cavi in rame e i flyover ottici attivi estendono entrambi la portata del canale oltre ciò che le tracce on-board possono offrire, ma risolvono problemi diversi. I cavi in rame si comportano come linee di trasmissione con vincoli di impedenza, schermatura e raggio di curvatura. I flyover ottici eliminano completamente la perdita dielettrica, ma introducono considerazioni di conversione elettro-ottica, potenza, termiche e latenza. Specifica l’approccio richiesto dal tuo budget di link e definisci cosa significhi prestazione equivalente per eventuali alternative considerate.

Checklist di specifica del cavo

- Impedenza differenziale e skew.

- IL e RL in funzione della frequenza, incluse le transizioni a ciascuna estremità.

- Efficacia della schermatura e approccio di messa a terra.

- Vincoli di raggio di curvatura e strain relief.

- Requisiti di cicli di accoppiamento e accesso per manutenzione.

- Comportamento passivo o attivo, se applicabile. Per i flyover ottici, specifica lunghezza d’onda, budget di potenza ottica, latenza e consumo di potenza per lane.

- Requisiti di qualificazione ed elenco dei cavi approvati.

Assieme flyover ottico attivo in evidenza

Samtec ECUO-B04-14-015-0-2-1-2-01 (FireFly ECUO) è un assieme flyover ottico attivo disponibile come transceiver full-duplex a 4 canali a 28 Gbps per canale, oppure come trasmettitore o ricevitore a 12 canali a 16 Gbps per canale. Con fibra multimodale OM3 può raggiungere fino a 100 metri. Elimina completamente la perdita delle tracce PCB e utilizza lo stesso sistema di micro-connettori degli assiemi flyover in rame di Samtec, quindi il footprint rimane invariato se passi dall’ottico al rame.

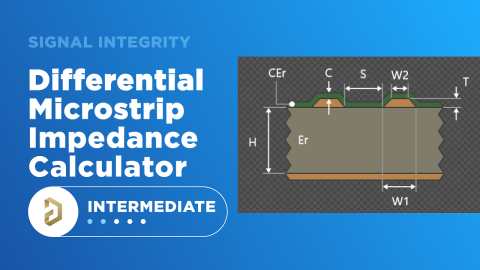

Fase 7. Materiali low-loss e rame: inserisci lo stackup nella specifica

I link a maggiore larghezza di banda richiedono che lo stackup sia un input progettuale controllato. La specifica del canale dovrebbe includere obiettivi sui materiali e intervalli accettabili, e dovrebbe indicare esplicitamente quali ipotesi stai facendo sulla rugosità del rame e sulla capacità di processo.

Checklist di specifica di materiali e stackup

- Obiettivi di Dk e Df alle frequenze rilevanti, oltre alla variazione ammessa.

- Ipotesi sul profilo del foglio di rame quando la perdita del conduttore è il fattore limitante.

- Controlli del rischio di glass weave e skew per lunghe tratte differenziali.

- Tg, Td e CTE sull’asse Z se l’ambiente o il profilo di assemblaggio sono impegnativi.

- Ipotesi sulla capacità del fabbricante: rapporti d’aspetto di foratura, registrazione, riempimento delle via e cicli di laminazione.

- Blocca il sistema di laminato e richiedi una revisione esplicita prima di qualsiasi sostituzione.

Laminate low-loss in evidenza

Le famiglie di laminati Panasonic MEGTRON 7 e Isola I-Tera MT40 sono esempi rappresentativi di materiali ultra-low-loss e very-low-loss utilizzati nei canali digitali ad alta velocità. Usa questi prodotti come punti di riferimento per capire cosa desideri da qualsiasi laminato tu scelga: dati elettrici stabili, indicazioni di processo e una chiara identità di prodotto da poter fissare nelle note di fabbricazione.

Passaggio 8. Piano di misura. Fai della correlazione l’obiettivo

Il tuo piano di misura deve includere piani di riferimento definiti, fixture, calibrazione e de-embedding, così da poter confrontare i risultati della simulazione con i dati di laboratorio senza ambiguità. IEEE 370-2020 è un riferimento pratico per questo lavoro e copre qualità dei dati, considerazioni sui fixture e de-embedding per la caratterizzazione di PCB e interconnessioni fino a 50 GHz.

Checklist del piano di misura

- Cosa misurerai: TDR per il profilo di impedenza, parametri S del VNA per i segmenti di interconnessione, ed eye diagram o jitter in punti definiti.

- Dove misurerai: Definisci i piani di riferimento e assegna loro un nome.

- Come calibrerai: Indica il metodo di calibrazione e la tracciabilità.

- Come eseguirai il de-embedding: Scegli metodi che puoi applicare con i tuoi fixture e strumenti.

- Come effettuerai la correlazione: Definisci i criteri di accettazione per l’allineamento tra simulazione e misura.

Piattaforma di misura in evidenza

Gli analizzatori di rete Keysight PNA-X coprono gamme di frequenza da 900 Hz fino a 67 GHz (a seconda del modello), con più sorgenti interne, ricevitori per parametri S e rumore, e compatibilità con il software PLTS di Keysight per la caratterizzazione delle interconnessioni e il de-embedding.

Dove si inserisce Octopart nel flusso di lavoro

I componenti per l’integrità del canale spesso hanno meno alternative realmente equivalenti. Famiglie di connettori, IC specializzati per il conditioning del segnale e alcuni assiemi di cavi possono diventare i componenti che rallentano una build. Usa Octopart e il BOM Tool per mantenere collegate tre cose mentre il progetto è ancora flessibile:

- Il codice componente e lo stato del ciclo di vita aggiornato.

- La documentazione di supporto: datasheet, modelli e reference design.

- Prodotti alternativi e opzioni di fornitura prima che footprint e interfacce vengano definiti in modo rigido.

Prima associ dati reali dei componenti al tuo modello di canale, meno ipotesi sopravvivranno fino al layout. Un file di parametri S di un connettore, una product brief di un retimer o una tabella Dk/Df di un laminato valgono più di un segnaposto e di un piano per finalizzare tutto in seguito. Octopart ti offre un unico posto pratico in cui verificare la disponibilità, recuperare datasheet e confermare lo stato del ciclo di vita mentre il progetto è ancora abbastanza flessibile da assorbire ciò che scopri.

La disciplina che evita le re-spin

L’integrità del canale si costruisce attraverso una serie di decisioni prese durante l’architettura, lo stackup e la selezione delle interconnessioni, e poi viene verificata tramite simulazione, misura e correlazione prima e dopo il layout. Il filo conduttore di tutto questo è sempre lo stesso: definisci ciò di cui hai bisogno, specificalo con numeri, scegli componenti supportati da dati che confermino quei numeri e scrivi il piano di misura prima che il layout venga congelato. I team che lo fanno con costanza sono quelli che evitano la re-spin.