Nozioni di base sull'analisi dell'integrità del segnale nel tuo PCB

Comprendere le basi dell'analisi dell'integrità del segnale nei PCB (signal integrity analysis) è tutt'altro che semplice. Gli strumenti di simulazione dell'integrità del segnale sono ottimi per calcolare il comportamento dei segnali in diverse reti durante la progettazione di schemi e layout, ma è comunque necessario compiere alcuni passi per interpretare i risultati. Per quanto avanzati possano essere alcuni strumenti di simulazione per l'integrità del segnale e di simulazione EM, non possono essere paragonati alle informazioni che si possono ricavare dalle misurazioni. Qualunque sia il metodo che usi per esaminare l'integrità del segnale nella tua scheda (dovresti fare entrambe le cose), ci sono alcuni passaggi importanti che puoi compiere per analizzare il comportamento dei segnali e identificare i problemi nella tua scheda.

Introduzione all'analisi dell'integrità del segnale

L'analisi dell'integrità del segnale inizia con le simulazioni nella fase di pre-layout. Una volta creato il layout, puoi utilizzare alcune importanti simulazioni post-layout per analizzare l'integrità del segnale dipendente dalla geometria della tua scheda. A un certo punto dovrai confrontare i risultati della simulazione dell'integrità del segnale con le misurazioni reali, quindi tieni i risultati a portata di mano per il confronto.

Analisi pre-layout

Questa parte riguarda la progettazione dei circuiti, la selezione dei componenti e l'esame del modo in cui i segnali viaggiano tra gli I/O di due componenti. Esistono tre analisi importanti che forniscono una quantità significativa di informazioni sul comportamento della tua scheda.

-

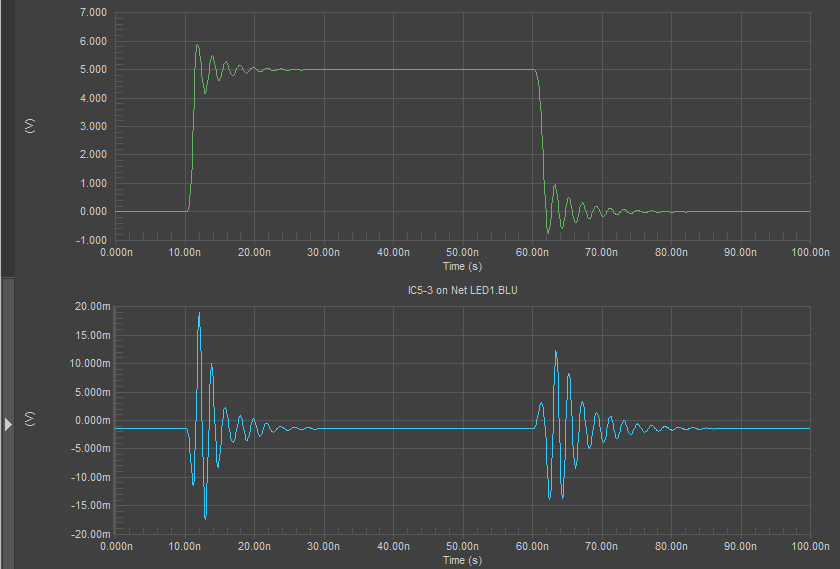

Comportamento transitorio. Le risposte transitorie nella connessione tra due buffer possono essere modellate anche nel dominio del tempo utilizzando l'analisi transitoria, oppure puoi determinare il comportamento dei transitori dall'analisi dei polo zero. Questo ti mostrerà l'overshoot/undershoot dovuto al ringing e l'avvicinamento al livello di segnale previsto. Le versioni più accurate di queste simulazioni con circuiti integrati coinvolgono modelli IBIS, sebbene i sottocircuiti SPICE possano essere utilizzati per modellare i buffer I/O.

-

Parametri S e funzione di trasferimento. Alcuni blocchi funzionali della scheda possono essere modellati come reti multiporta, pertanto il loro comportamento lineare può essere descritto in termini di parametri S a una particolare frequenza. Puoi determinare i parametri S da un coefficiente di riflessione nel dominio temporale, che nelle linee di trasmissione coinvolge l'impedenza di input data dalla capacità di carico. Puoi calcolare la funzione di trasferimento della tua rete dai parametri S e viceversa. Ecco un'ottima guida che illustra tutti i passaggi matematici.

-

Risposta all'impulso. Questa simulazione prevede due obiettivi: qualificare i modelli/funzioni di trasferimento dei parametri S per la causalità nella larghezza di banda definita ed esaminare il comportamento della risposta agli impulsi per un tempo di salita definito. Le risposte agli impulsi consentono inoltre di estrarre la dispersione e la propagazione lungo il progetto di interconnessione. Questo qualifica un modello di canale previsto per una determinata coppia di buffer di input/output in una situazione ideale prima di configurare il PCB.

-

Diagramma a occhio. I modelli di buffer e la progettazione dell'interconnessione possono essere utilizzati per simulare un diagramma ad occhio. Il diagramma ad occhio è una parte importante della conformità del canale poiché mostra il livello del segnale previsto, l'overshoot, l'interferenza intersimbolica (ISI), il jitter e il tasso di errore di bit previsto in una sequenza di bit pseudocasuale.

Nei canali più complessi, la serie di analisi pre-layout di cui sopra può aiutarti a qualificare aspetti come le transizioni dei via pianificate,

Se conosci la struttura di ciascuno di questi elementi prima di creare la progettazione, puoi

Analisi post-layout

Questa parte riguarda l'esame di come gli elementi parassiti presenti nella tua scheda influiscano sull'integrità del segnale. Poiché gli effetti parassiti dell'integrità del segnale sono funzioni della geometria della scheda, dovrai esaminare i seguenti problemi di integrità del segnale dipendenti dalla geometria:

-

Diafonia. La diafonia (crosstalk) è la rovina di molti progettisti e deriva dall'accoppiamento induttivo e capacitivo. Se stai esaminando gli effetti della diafonia su una traccia vittima e una aggressore, l'accoppiamento capacitivo si verifica solo quando le due tracce sono adiacenti. La diafonia induttiva non è limitata dal raggio d'azione e tutte le tracce della scheda possono accoppiarsi tra loro attraverso il campo magnetico.

-

Comportamento della linea di trasmissione. Sebbene sia possibile utilizzare i modelli di linea di trasmissione per esaminare le tracce del segnale durante la fase di pre-layout, è meglio farlo direttamente dal layout. Se le tue linee non sono a impedenza controllata, dovrai verificare se le riflessioni sulla linea (se presenti) degradano i livelli del segnale al ricevitore e portano a una risposta a gradini con i segnali digitali. Con i segnali analogici, questo può essere più complicato, in quanto si cerca l'interferenza e la formazione di onde stazionarie sulla linea. Tuttavia, il giusto simulatore di integrità del segnale può separare l'incidente e le onde riflesse, consentendo di esaminare il comportamento di ciascuno individualmente. Potrai quindi determinare il livello di riflessione e verificare se il livello del segnale soddisfa i tuoi requisiti di segnalazione.

-

Tutto ciò che hai esaminato prima del layout! Il punto qui è verificare che i parassiti, la trama delle fibre, o altro, non alterino drasticamente il comportamento dei segnali nella scheda. Se più tracce non funzionano, allora il tuo layout dovrà essere modificato. Il primo punto di partenza è la geometria dello stack-up e della traccia.

Strumenti per la signal integrity analysis

I punti precedenti potrebbero far pensare che sia necessario un programma di simulazione complesso per costruire ed eseguire questi strumenti di signal integrity analysis. Gli strumenti esatti di cui avrai bisogno dipenderanno da ciò che desideri simulare e valutare. All'interno del tuo strumento EDA, alcune di queste simulazioni possono essere effettuate semplicemente con qualcosa come IBIS, mentre le simulazioni più complesse con reti multiple possono richiedere un field solver 3D o uno strumento solver 2D analogo.

Bus single-ended senza specifiche di impedenza

Nei bus single-ended più lenti senza terminazione, è possibile osservare un comportamento transitorio (ringing) che potrebbe essere dovuto alla struttura dell'interconnessione (la sua capacità e induttanza). Questo è un fenomeno che si può osservare nell'SPI quando la traccia è elettricamente corta. In questi bus è possibile osservare il ringing pre-layout, a patto che sia applicato un modello di linea di trasmissione negli schematici e che siano definite le specifiche dei pin (sottocircuito SPICE o modello IBIS).

Quando il bus single-ended viene effettivamente instradato, puoi eseguire una simulazione post-layout con l'analizzatore di integrità del segnale nei tuoi strumenti EDA. Questi analizzatori possono utilizzare l'assegnazione di una famiglia logica o un modello IBIS per i pin/le reti per simulare:

- Forme d'onda di diafonia e per identificare le regioni di forte accoppiamento

- Forme d'onda di riflessione

- Altre metriche di comportamento del segnale (tempo di salita/discesa, overshoot/undershoot, ecc.)

- Calcolare l'impedenza media lungo la lunghezza della traccia

Nei bus single-ended senza specifiche di impedenza, è possibile osservare riflessioni all'estremità del driver quando il bus si allunga, oppure ringing dovuto alla capacità e all'induttanza del bus. Se il ringing produce un eccessivo overshoot, la riduzione dell'induttanza della traccia e l'aggiunta di smorzamento sono le due strade principali per ridurre l'ampiezza del ringing. L'altra possibilità è quella di aumentare lo smorzamento aggiungendo una resistenza in serie, cosa che si farebbe con un buffer a bassa impedenza in uscita su una linea di trasmissione più lunga non corrispondente.

Bus con controllo dell'impedenza

Nei bus single-ended e con controllo dell'impedenza differenziale, l'impedenza di terminazione potrebbe essere on-die, quindi una simulazione basata sulla famiglia logica nel post-layout non è efficace in quanto non descrive correttamente l'impedenza del bus. La diafonia può ancora essere simulata perché si sta considerando solo l'accoppiamento tra due interconnessioni in funzione del tempo di salita, e l'entità della diafonia crescerà di conseguenza in modo inversamente proporzionale al tempo di salita, anche se si assegna solo una famiglia logica.

Nel caso di una simulazione post-layout per le riflessioni e le violazioni dell'impedenza, una simulazione dovrebbe utilizzare almeno i modelli IBIS per definire il comportamento del buffer piuttosto che affidarsi alle descrizioni delle famiglie logiche. Finché la descrizione del buffer è nota e disponibile, può essere applicata per modellare il comportamento del componente nell'editor PCB. Lo strumento standard per l'integrità del segnale in un editor PCB per le forme d'onda di diafonia e riflessione può aiutare con molte qualificazioni iniziali del comportamento del segnale (tempo di salita/discesa, overshoot, diafonia, impedenza costante e ringing) prima di passare a uno strumento di analisi più avanzato.

Per simulare elementi come i diagrammi a occhio, la diafonia tra più reti e le deviazioni di impedenza lungo la lunghezza di una rete, è possibile utilizzare strumenti esterni. I field solver sono un'opzione e sono disponibili molti strumenti con diversi livelli di specializzazione. Un field solver a onda intera non è sempre necessario, a meno che non si voglia simulare le emissioni irradiate, qualcosa di più profondo con SI/PI, o estrarre i parametri S nella rete simulata.

I potenti strumenti di progettazione e analisi PCB di Altium Designer® forniscono un utile punto di partenza per l'analisi dell'integrità del segnale con strumenti di simulazione dell'integrità del segnale pre-layout e post-layout. Questi calcoli accurati offrono una base per confrontare le misurazioni. Avrai inoltre accesso a una serie completa di funzioni di pianificazione e documentazione della produzione in un'unica piattaforma.

Puoi scaricare una versione di prova gratuita di Altium Designer e approfondire le tue conoscenze sui migliori strumenti per la creazione di layout PCB, la simulazione dell'integrità del segnale e la produzione disponibili sul mercato. Contatta subito un esperto di Altium per saperne di più su Altium Designer.