HDI so với Ultra HDI: Những điều nhà thiết kế PCB phải lưu ý trên sàn sản xuất

Công nghệ HDI (High Density Interconnect) từ lâu đã là nền tảng trong thiết kế và chế tạo PCB mật độ cao . Hầu hết các nhà thiết kế đều đã quen thuộc với microvia, ép lớp tuần tự, cũng như các giới hạn về trace và spacing của quy trình ăn mòn trừ trong chế tạo PCB. Điều từng được xem là một đường cong học tập dốc đối với cả nhà thiết kế lẫn nhà chế tạo nay chủ yếu là vấn đề thực thi thay vì phát triển quy trình.

Ngày nay, “Ultra HDI” đang nổi lên như một mô hình mới trong chế tạo PCB siêu tinh và thiết kế liên kết tiên tiến, với đường cong học tập dốc cho cả nhà thiết kế và nhà chế tạo. Thoạt nhìn, có thể Ultra HDI chỉ là sự tiến hóa của công nghệ HDI.

Ultra HDI khác với HDI tiêu chuẩn không chỉ ở kích thước đặc tính mà còn ở cách tiếp cận sản xuất. Trong khi HDI dựa vào các quy trình ăn mòn trừ đã trưởng thành và các cấu trúc microvia đã được hiểu rõ, Ultra HDI đòi hỏi quy trình đồng bán cộng, kiểm soát vật liệu chặt chẽ hơn và mức dung sai cho biến thiên thấp hơn đáng kể để đạt được năng suất sản xuất lặp lại.

Tuy nhiên, xét từ góc độ xưởng chế tạo, Ultra HDI hoàn toàn không chỉ đơn giản là thế hệ tiếp theo của các quy trình HDI. Đây là một mô hình vận hành mới và riêng biệt, với các ranh giới quy trình, vật liệu và yếu tố rủi ro hoàn toàn mới. Dù bạn có thể kết hợp các lớp Ultra HDI và các lớp HDI trong cùng một stack-up, việc sử dụng Ultra HDI thành công đòi hỏi kiến thức chuyên sâu về các quy trình và tham số quy trình.

Hãy cùng xem một cách thực tế điều gì thực sự phân biệt HDI với Ultra HDI khi bạn đưa thiết kế vào sản xuất.

Điểm chính cần nhớ

- Ultra HDI đưa ra một mô hình sản xuất mới, trong đó các phương pháp HDI truyền thống (ăn mòn trừ, solder mask tiêu chuẩn, các stack microvia cơ bản) trở nên thiếu ổn định và không còn đủ đáp ứng ở các hình học siêu tinh.

- Sản xuất đáng tin cậy là thước đo thành công, vì UHDI đòi hỏi quy trình đồng bán cộng, kiểm soát dung sai chặt chẽ hơn nhiều và phụ thuộc sâu hơn vào tính lặp lại trên toàn bộ panel và giữa các lô sản xuất.

- Vật liệu và độ đăng ký trở thành các yếu tố giới hạn yield chính, khi kiểu dệt sợi thủy tinh, giãn nở theo trục Z, độ nhám đồng và sai lệch kích thước tích lũy tác động trực tiếp đến căn chỉnh, trở kháng, độ tin cậy của microvia và khả năng chế tạo tổng thể.

- Các giao diện lắp ráp đặt ra những ràng buộc nghiêm ngặt hơn, thường yêu cầu solder mask màng khô, lớp hoàn thiện bề mặt được lựa chọn cẩn thận và sự phối hợp sớm với nhà chế tạo để giảm thiểu rủi ro liên quan đến xếp chồng microvia, định nghĩa pad và hàn fine-pitch.

Cách nhà chế tạo phân biệt HDI và Ultra HDI trong sản xuất

Về mặt chế tạo, HDI vẫn gắn chặt với quy trình xử lý đa lớp thông thường. Các đặc tính nhỏ hơn và dung sai chặt hơn, nhưng nhiều phương pháp cốt lõi vẫn quen thuộc. Ăn mòn trừ, microvia khoan laser và solder mask LPI tiêu chuẩn vẫn có thể đáp ứng yêu cầu nếu được áp dụng cẩn thận.

Với Ultra HDI, kích thước đặc tính thu nhỏ đến mức các quy trình truyền thống trở nên thiếu ổn định, biên độ đăng ký gần như biến mất, và những vật liệu vốn hoạt động tốt ở kích thước HDI bắt đầu trở thành bất lợi. Ở quy mô đó, thành công không còn phụ thuộc vào việc một quy tắc có thể đạt được một lần hay không, mà là liệu nó có thể được lặp lại trên toàn bộ panel, hết lô này đến lô khác hay không. Các quy trình chế tạo cần có sự thay đổi rõ rệt để giúp nhà chế tạo tạo ra sản phẩm có độ tin cậy cao.

Thực tế về kích thước đặc tính và tạo hình mạch

Phần lớn các thiết kế HDI hoạt động trong phạm vi kích thước trace và spacing đã được thiết lập vững chắc trong các quy trình chế tạo PCB thông thường, sử dụng các quy trình trưởng thành, yield có thể dự đoán và các phương pháp kiểm tra đã được chứng minh. Tuy nhiên, công nghệ Ultra HDI đẩy các kích thước đặc tính này vào một vùng thách thức hơn, nơi ăn mòn trừ truyền thống gặp khó khăn trong việc duy trì tính nhất quán do độ nhạy tăng lên với các yếu tố như biến thiên chiều dày đồng, hệ số ăn mòn và độ chính xác ghi ảnh.

- HDI: Sử dụng các quy trình trưởng thành, ổn định với yield có thể dự đoán.

- Ultra HDI: Yêu cầu các quy trình như bán cộng hoặc bán cộng cải tiến để tạo các đặc tính đồng do giới hạn của ăn mòn trừ ở kích thước đặc tính cực nhỏ.

- Quy tắc thiết kế tối thiểu không đồng nghĩa với năng lực sản xuất ổn định; kiểm tra DFM không đảm bảo yield lặp lại trong Ultra HDI.

Đối với nhà thiết kế PCB, thông điệp quan trọng là các quy tắc thiết kế tối thiểu, ngay cả khi vượt qua kiểm tra DFM, cũng không đảm bảo yield sản xuất ổn định và có thể lặp lại trong Ultra HDI. Các nhà chế tạo nhấn mạnh rằng năng lực sản xuất đáng tin cậy khác với mức tối thiểu tuyệt đối mà một quy tắc cho phép, và nhà thiết kế nên ưu tiên hiểu đặc tính đó sẽ được chế tạo như thế nào thay vì chỉ quan tâm nó có thể nhỏ đến mức nào về mặt lý thuyết.

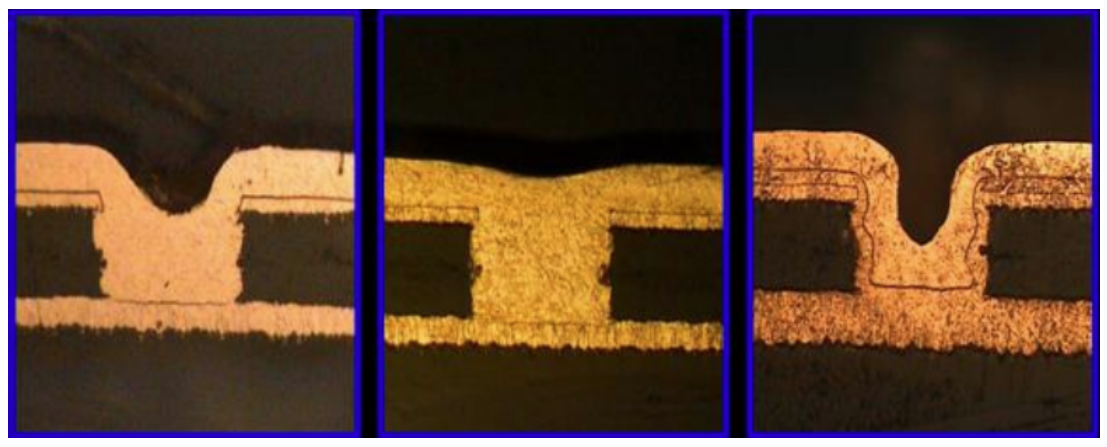

Cấu trúc via: Hình dạng quen thuộc, hệ quả mới

Các nhà thiết kế HDI hẳn đã quen với microvia, thường là dạng so le và đôi khi xếp chồng sâu một hoặc hai lớp. Độ tin cậy ở mức đó đã được đặc trưng khá rõ, đặc biệt khi vật liệu và quy trình mạ được phối hợp tốt.

Ultra HDI phụ thuộc nhiều hơn vào microvia xếp chồng, thường được lấp đầy bằng đồng và kéo dài qua hơn 2 lớp build-up. Tỷ lệ hình học trở nên chặt hơn, độ đồng đều mạ trở nên cực kỳ quan trọng, và ngay cả các lỗ rỗng nhỏ cũng có thể làm suy giảm độ tin cậy. Ở quy mô này, hình học via, hóa học lấp đầy và hành vi nhiệt là những yếu tố không thể tách rời.

Từ phía chế tạo, các stack sâu hơn làm tăng độ nhạy khi khoan, độ phức tạp khi mạ và khó khăn trong kiểm tra. Từ phía thiết kế, mỗi lớp xếp chồng bổ sung đều làm tăng nguy cơ microvia hỏng trong quá trình lắp ráp hoặc khi vận hành thực tế. Câu hỏi chuyển từ “Có thể chế tạo được không?” sang “Nó có thể chịu được reflow và điều kiện vận hành thực tế một cách ổn định hay không?”

Vật liệu: Ràng buộc và lựa chọn trong Ultra HDI

Trong các thiết kế Ultra HDI, việc lựa chọn vật liệu xác lập giới hạn hiệu năng của chế tạo PCB fine-line, bao gồm kích thước đặc tính, dung sai đăng ký và độ tin cậy liên kết. Các laminate và lá đồng chấp nhận được trong HDI thông thường thường trở thành yếu tố giới hạn yield khi chiều rộng trace, capture pad và đường kính microvia thu nhỏ xuống mức vài chục micron. Ở quy mô này, độ ổn định kích thước và đặc tính bề mặt quan trọng hơn hiệu năng điện danh định.

Một số ảnh hưởng liên quan đến vật liệu cần được tính đến rõ ràng trong quá trình xác định stackup và layout:

- Độ không đồng đều của kiểu dệt sợi thủy tinh gây ra biến dạng kích thước cục bộ và biến thiên điện môi, ảnh hưởng trực tiếp đến kiểm soát trở kháng và căn chỉnh đặc tính ở các hình học siêu tinh.

- Giãn nở theo trục Z tích lũy qua các chu kỳ ép lớp tuần tự, làm tăng ứng suất cơ học trong các microvia xếp chồng hoặc đặt gần nhau.

- Độ nhám bề mặt đồng làm thay đổi chiều rộng dẫn điện hiệu dụng và biên dạng cạnh đường mạch khi sử dụng trọng lượng đồng rất thấp, làm tăng biến thiên về trở kháng và độ chính xác ăn mòn.

Các hệ vật liệu phù hợp với Ultra HDI giảm thiểu các ảnh hưởng này thông qua kiểm soát sợi thủy tinh chặt chẽ hơn, giá trị Tg cao hơn để giảm dịch chuyển do nhiệt, và lá đồng rất nhẵn hoặc được xử lý ngược. Những vật liệu này quyết định giới hạn hình học và đăng ký có thể đạt được, vì vậy phải được lựa chọn trước khi chốt chiều rộng trace, cấu trúc via và chiến lược ép lớp.

Đăng ký: Quản lý sai số kích thước tích lũy

Đăng ký trở thành một rủi ro thiết kế chính trong layout Ultra HDI do biên độ chồng lấp rất hạn chế giữa via, pad và trace. Mỗi bước ép lớp và ghi ảnh đều tạo ra dịch chuyển kích thước, và sai số phát sinh mang tính tích lũy chứ không ngẫu nhiên. Khác với HDI tiêu chuẩn, thường không có đủ biên độ để hấp thụ các dịch chuyển này bằng cách tăng kích thước pad hoặc tăng khoảng cách.

Độ chính xác vị trí của khoan laser không loại bỏ được rủi ro đăng ký, vì vị trí khoan phụ thuộc vào trạng thái kích thước của vật liệu tại thời điểm gia công. Sự giãn của phim ảnh, sự thư giãn của lõi và dòng chảy nhựa đều góp phần gây lệch giữa các lớp. Khi capture pad và các đặc tính trace được xác định ở kích thước mức micron, ngay cả các quy trình chế tạo được kiểm soát chặt chẽ cũng có thể vượt quá dung sai cho phép.

Nhà thiết kế tác động trực tiếp đến độ vững của đăng ký thông qua cấu trúc layout. Giảm số chu kỳ ép lớp, hạn chế xếp chồng via và duy trì căn chỉnh nhất quán của các đặc tính quan trọng giữa các lớp sẽ làm giảm độ nhạy với sai lệch kích thước. Chừa khoảng cách thực tế giữa các cấu trúc liền kề giúp tạo dung sai cho chuyển động vật liệu không thể tránh khỏi mà không làm giảm yield.

Giới hạn của solder mask và lớp hoàn thiện bề mặt

Hình học pad trong Ultra HDI thường vượt quá giới hạn độ phân giải của các loại solder mask quang ảnh lỏng truyền thống. Khi các cửa mở pad thu nhỏ và các vách mask hẹp lại, việc kiểm soát chiều dày và định nghĩa cạnh trở nên cực kỳ quan trọng đối với yield lắp ráp. Những biến thiên có thể chấp nhận ở kích thước lớn hơn lại trở thành cơ chế lỗi chủ đạo ở fine pitch.

Trong nhiều ứng dụng Ultra HDI, solder mask màng khô là bắt buộc để duy trì hình học khẩu độ và đăng ký nhất quán. Việc trộn pad định nghĩa bởi solder mask và pad không định nghĩa bởi solder mask ở fine pitch làm tăng biến thiên về thể tích hàn và hành vi thấm ướt, và nên tránh trừ khi đã được xác nhận rõ ràng với nhà chế tạo và đơn vị lắp ráp.

Lựa chọn lớp hoàn thiện bề mặt cũng bị ràng buộc tương tự. Độ đồng đều chiều dày và tính nhất quán của lớp phủ ảnh hưởng trực tiếp đến khả năng hàn và độ đồng phẳng khi pad và trace cực nhỏ. Những ảnh hưởng này thường bộc lộ trong quá trình lắp ráp và kiểm tra, dù chúng bắt nguồn từ các quyết định ở cấp độ layout.

Trong các thiết kế Ultra HDI, lựa chọn solder mask, lớp hoàn thiện bề mặt, quy trình chế tạo và yêu cầu lắp ráp có mối liên hệ chặt chẽ với nhau. Các lựa chọn được đưa ra trong giai đoạn layout sẽ lan truyền xuống các công đoạn sau với rất ít cơ hội sửa chữa, vì vậy việc phối hợp sớm xuyên suốt toàn bộ luồng sản xuất là điều thiết yếu.

Nhà thiết kế nên làm gì khác đi

Thiết kế Ultra HDI thành công đòi hỏi sự thay đổi trong tư duy. Hãy làm việc với đối tác chế tạo sớm hơn so với khi làm HDI. Hãy hỏi các đặc tính được tạo ra như thế nào, chứ không chỉ liệu chúng có đạt quy tắc hay không. Hãy tạo biên độ an toàn ở bất cứ đâu hệ thống cho phép, ngay cả khi áp lực mật độ rất cao. Ultra HDI là một lĩnh vực riêng, với các thực hành tốt nhất và các chế độ hỏng hóc riêng.

Dù bạn cần chế tạo điện tử công suất đáng tin cậy hay các hệ thống số tiên tiến, Altium Develop kết nối mọi chuyên ngành thành một lực lượng cộng tác thống nhất. Không còn silo. Không còn giới hạn. Đây là nơi các kỹ sư, nhà thiết kế và nhà đổi mới làm việc như một thể thống nhất để đồng sáng tạo mà không bị ràng buộc. Trải nghiệm Altium Develop ngay hôm nay!

Câu hỏi thường gặp

Sự khác biệt chính giữa HDI và Ultra HDI là gì?

Ultra HDI không chỉ đơn thuần là thu nhỏ các đặc tính của HDI, mà còn đòi hỏi các quy trình sản xuất, vật liệu và dung sai hoàn toàn khác. Ăn mòn trừ truyền thống, solder mask LPI tiêu chuẩn và xếp chồng microvia cơ bản trở nên thiếu ổn định ở các hình học siêu tinh. Thay vào đó, Ultra HDI phụ thuộc vào quy trình đồng bán cộng, kiểm soát đăng ký cực kỳ chặt chẽ và các vật liệu chuyên biệt cao để duy trì yield đáng tin cậy.

Tại sao một thiết kế có thể vượt qua kiểm tra DFM nhưng vẫn thất bại trong sản xuất Ultra HDI?

Kiểm tra DFM xác minh rằng thiết kế đáp ứng các quy tắc cho phép ở mức tối thiểu, nhưng Ultra HDI đòi hỏi tính lặp lại chứ không chỉ là khả năng thực hiện một lần. Các yếu tố như dịch chuyển vật liệu, độ chính xác ghi ảnh, biến thiên chiều dày đồng, độ đồng đều của lấp đầy microvia và sai lệch đăng ký tích lũy có thể đẩy các đặc tính vượt ra ngoài năng lực sản xuất ổn định. Việc vượt qua DFM không đảm bảo rằng thiết kế có thể được sản xuất nhất quán trên các panel và giữa các lô.

Có bao nhiêu lớp microvia xếp chồng là khả thi trong Ultra HDI, và những yếu tố nào ảnh hưởng đến độ tin cậy của chúng?

Trong các thiết kế Ultra HDI, thường cần dùng microvia xếp chồng, được lấp đầy bằng đồng, qua nhiều lớp build-up, nhưng độ tin cậy sẽ giảm mạnh khi chiều cao chồng tăng lên. Tỷ lệ khía cạnh, hóa chất mạ, chu kỳ nhiệt, độ giãn nở theo trục Z và giới hạn kiểm tra đều ảnh hưởng đến khả năng sống sót của cấu trúc này. Câu hỏi then chốt chuyển từ “Có chế tạo được không?” sang “Nó có chịu được quá trình reflow và điều kiện vận hành thực tế không?”. Trong thực tế, giảm độ sâu xếp chồng sẽ cải thiện yield, độ tin cậy và độ ổn định chế tạo trong quy trình sản xuất PCB Ultra HDI, nơi độ phức tạp của microvia xếp chồng tác động trực tiếp đến tính lặp lại của quy trình.

Nên chọn vật liệu nào để đạt hiệu năng Ultra HDI ổn định?

Lựa chọn vật liệu là một trong những yếu tố quyết định lớn nhất đến thành công của UHDI. Điều này bao gồm các vật liệu laminate có cấu trúc sợi thủy tinh được kiểm soát chặt chẽ, độ giãn nở theo trục Z thấp, và lá đồng rất nhẵn hoặc được xử lý ngược để duy trì độ chính xác của đường mạch và khả năng đăng ký lớp. Những vật liệu này giúp giảm thiểu biến thiên trở kháng, độ nhám cạnh đường mạch và độ trôi kích thước — các yếu tố có thể làm giảm yield ở các hình học siêu mịn.