Können Sie Serien- und Parallelschlusswiderstände im gleichen Netz verwenden?

Serielle und parallele Abschlusswiderstände sind die gängigsten resistiven Abschlussoptionen für digitale Signale. Der Grund dafür ist, dass der Widerstand eine breitbandige Größe ist und erst im GHz-Bereich durch parasitäre Effekte beeinflusst zu werden beginnt. Bei der Kanalbandbreite, die mit den meisten digitalen Signalen verbunden ist, gibt es Fälle, in denen eine unterminierte Leitung tatsächlich einen Abschluss benötigt, auch wenn es keine Impedanzspezifikation für die Schnittstelle gibt.

Da beide Optionen für digitale Signale geeignet sind, welche sollten Sie verwenden, um eine lange Übertragungsleitung ohne Impedanzspezifikation zu terminieren? Manchmal gibt es die Wahrnehmung, dass beide verwendet werden sollten, oder dass beide bei jedem Netz verwendet werden können. Es gibt Fälle, in denen beide gleichzeitig verwendet werden können, aber typischerweise wird nur eine ausgewählt, da sie die Notwendigkeit für die andere eliminieren kann.

In diesem Artikel werde ich die Signalgebung, die in beiden seriellen und parallelen Abschlüssen involviert ist, und den Spezialfall, in dem Sie beide Abschlüsse sehen könnten, betrachten.

Serielle und parallele Abschlüsse über Transferfunktionen

Die nachfolgende Erklärung basiert nicht per se auf der Dynamik von Signalen. Dafür können Sie diesen guten Artikel von Kella Knack lesen, der Beispielwellenformen zeigt. Stattdessen werde ich aus der Perspektive der Übertragungsfunktion betrachten, um genau zu zeigen, was mit den Spannungspegeln in einer Übertragungsleitung passiert. Dies enthüllt auch den Effekt der Bandbreite auf digitale Signale.

Was ich unten bezüglich dieser beiden Abschlüsse zeigen werde und warum sie oft nicht zusammen im selben Netz verwendet werden, basiert auf den folgenden Annahmen:

- Die Schnittstellen haben kein spezifiziertes Impedanzziel, was bedeutet, dass die Leiterbahnenimpedanz beliebig sein könnte

- Die Treiberimpedanz ist im Allgemeinen ein niedriger Wert, und die Lastimpedanz wird als einfache Lastkapazität modelliert

- Die Ausgangsimpedanz des Treibers ist bekannt oder kann ermittelt werden, beispielsweise durch Messung oder Simulation (IBIS)

Lassen Sie uns nun jede dieser Abschlüsse im Detail betrachten.

Serienabschluss Übertragungsfunktion

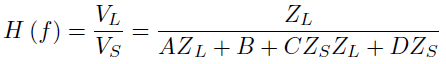

Die unten gezeigte Schaltung illustriert den Formalismus, der verwendet wird, um die Übertragungsfunktion der Übertragungsleitung aus ABCD-Parametern zu bestimmen. Beachten Sie, dass wir auch S-Parameter verwenden könnten, aber ABCD-Parameter sind viel einfacher.

Die Übertragungsfunktion ist das Verhältnis der Lastspannung zur Quellenspannung. Das Tolle an einem Ansatz mit Übertragungsfunktion ist, dass die Lastspannung explizit in Bezug auf die Quellenimpedanz definiert ist, wie oben gezeigt. Jetzt können wir unsere Quellenimpedanzen und jeden Serienwiderstand einsetzen.

Wenn der Serienwiderstand verwendet wird, um die Übertragungsleitung perfekt abzuschließen, wird der Widerstand so dimensioniert, dass R = ZS - Z0 ist. Dieser Widerstand wird normalerweise am Treiber-IO-Pin platziert, und wir haben nun die Beziehung, bei der die gesamte Quellenimpedanz ZS = Z0 ist, da dies die neue gesamte Ausgangsimpedanz ist. Unter Verwendung der Definition der ABCD-Parameter für eine Übertragungsleitung haben wir:

Hier haben wir eine Übertragungsfunktion, die wie ein Spannungsteiler aussieht, der die Lastimpedanz und die Impedanz der Übertragungsleitung einbezieht. Die Spannung an der Last ist:

Wenn wir die Lastimpedanz sehr groß machen, hätten wir den folgenden Wert für die Spannung an der Last:

Dies gilt innerhalb der Kanalbandbreite, wie sie durch die Lastkapazität definiert ist. Wie wird das Signal vom Treiber beeinflusst, nachdem es mit der gesamten Quellenimpedanz interagiert hat, die den Serienwiderstand einschließt? Wenn Sie die Definition der ABCD-Parameter verwenden und V1 berechnen, erhalten Sie folgendes, wenn ZS + R = Z0:

Nun sehen wir die Funktion des Serienwiderstands: Bei perfekter Anpassung wirken die Quellenimpedanz und die Leiterbahnenimpedanz wie ein Spannungsteiler. Wenn die Quellenimpedanz unter oder über der Leiterbahnenimpedanz liegt, würden wir nach der Reflexion an der Last ein Überschwingen oder Unterschwingen beobachten.

Erst durch die Reflexion an der Last wird das halbierte Signalniveau auf das volle Niveau wiederhergestellt. Deshalb würden wir typischerweise auch keine Parallelschaltung am gleichen Netz anwenden, wenn die Empfängerspannung denselben Wert wie die Quellenspannung sehen muss. Jetzt schauen wir uns die Parallelschaltung alleine an.

Parallelschaltung

Bei der Parallelschaltung geht es darum, die Reflexion am Empfänger zu unterdrücken, wie ich oben erwähnt habe. In einem impedanzspezifizierten Bus wird die Terminierung üblicherweise auf dem Halbleiterchip platziert. In allgemeineren Fällen, wie bei bestimmten Leitungstreibern, ist die Impedanz nicht spezifiziert, und daher könnte eine Terminierung manuell angebracht werden müssen.

Die Parallelabschluss ohne Serienwiderstandsabschluss funktioniert wie folgt:

- Da kein Serienwiderstand vorhanden ist, bewirkt die Spannungsteilungsfunktion, dass das gesamte Signal auf die Übertragungsleitung gelegt wird (V1 = VS)

- Das Signal breitet sich dann zur Last aus und reflektiert nicht, sodass es vollständig über den Parallelwiderstand absorbiert wird

Wenn wir eine perfekte Quellenimpedanz von ZS = 0 annehmen, gibt die Übertragungsfunktion für den Parallelabschluss die folgende Beziehung für die Last- und Quellenspannungen an:

Beim Parallelabschluss sehen wir, dass im Zähler ein Faktor 2 steht. Die Abschlussschaltung erzeugt einen Widerstand parallel zu einer Lastkapazität, wobei der Widerstand R = Z0 ist. Innerhalb derBandbreitengrenze des Kanalkniefrequenzbereichs, wie durch diese kapazitive Last definiert, ist die Lastimpedanz nahezu gleich dem Parallelwiderstand. Dies ergibt erneut die Spannung, die an der Last gesehen wird, wenn R = Z0 und somit ZL = Z0 ist:

Wir erhalten erneut das vollständige Stärkesignal, das wir in die Verbindung gesendet haben.

Wenn die Quellenimpedanz nicht null ist, gehen Sie zurück in die Definition der Übertragungsfunktion und setzen Sie den Wert für Ihre Quellenimpedanz ein. Dies könnte aus Messungen oder aus Simulationen extrahiert werden.

Können Sie sowohl Serien- als auch Parallelabschluss verwenden?

Wenn wir die allgemeine Form der Übertragungsfunktion des Serienabschlusswiderstands vergleichen, sollte sehr klar sein, warum wir nicht absichtlich auch einen Parallelwiderstand platzieren, wenn bereits ein Serienwiderstand vorhanden ist. Wenn Sie mit einem diskreten Serienwiderstand perfekt abgleichen und dann auch mit einem Parallelwiderstand abgleichen, dann gelangt nur die Hälfte des Signalpegels auf die Leitung und dies wird vom Parallelwiderstand absorbiert. Mit anderen Worten, die an der Last gesehene Spannung ist:

Wenn Sie eine Komponente mit einem 3,3 V Signalpegel verwenden und der Empfänger ebenfalls einen 3,3 V Signalpegel verlangt, dann könnten Sie möglicherweise nicht gleichzeitig sowohl Serien- als auch Parallelabschluss verwenden. Sie müssten sorgfältig die Logikschwellen im Empfänger prüfen, um sicherzustellen, dass die Spannung an der Last nicht zu niedrig ist.

Der Sonderfall tritt auf, wenn Sie beabsichtigen, von einer Quellspannung auf eine niedrigere Lastspannung herunterzuregeln. Zum Beispiel, bei einer 3,3 V Quelle und einer Last, die eine Amplitude von 1,8 V benötigt, wäre das Signalniveau, das an der Last ankommt, 1,65 V bei sowohl serieller als auch paralleler Terminierung. Dies könnte am unteren Ende der Spannung liegen, die erforderlich ist, um als HIGH-Logikzustand im Empfänger zu registrieren. Wir können andere Beispiele für gängige Logikpegel finden, bei denen wir das gleiche Ergebnis erhalten.

Anstatt zu versuchen, mit Terminierungswiderständen herunterzuregeln, würden Sie normalerweise zwischen zwei verschiedenen Signalpegeln mit einem Pegelwandler wechseln. Diese Komponenten sind entweder für spezifische Schnittstellen konzipiert oder sie können mit einer Reihe möglicher Schnittstellen kompatibel sein. Diese Komponenten akzeptieren unterschiedliche Versorgungsspannungen und erzeugen eine Replik des eingehenden Signals am Ausgang, jedoch mit einer höheren oder niedrigeren Spannung. Ein Beispiel für den SN65DP159 von Texas Instruments wird unten gezeigt.

Gilt all dies auch für differentielle Paare?

Die Antwort lautet "ja" mit einem Sternchen; wenn ein Differentialpaar verwendet wird, dann ersetze die charakteristische Impedanz in den oben genannten Übertragungsfunktionen durch die ungerade Modusimpedanz und berechne den Unterschied in den gegensätzlich polarisierten Signalen auf der Empfängerseite der Verbindung.

Die meisten differentiellen Schnittstellen haben spezifische Abschlussanforderungen und Spurimpedanzanforderungen, die bereits auf dem Chip auf der Treiberseite der Leitung implementiert sind (mindestens). Wenn eine Gleichstromkopplung erforderlich ist, verhindert dieser On-Die-Abschluss auf der Treiberseite die Verwendung eines Serienwiderstands. In anderen Fällen könnte eine parallele Terminierung verwendet werden, wenn die Empfängerkomponente keinen On-Die-Abschluss hat, was nicht üblich ist. Die Verwendung von Terminierung (Serie, parallel oder beides) kann immer noch in Spezialfällen angewendet werden, aber es würde in Datenblättern spezifiziert, durch Tests bestimmt oder es wäre bereits On-Die enthalten.

Sobald Sie die Übertragungsfunktion der Übertragungsleitung gefunden haben und bereit sind, Ihren Kanal zu layouten, verwenden Sie die Design- und Layout-Tools in Altium Designer®. Um die Zusammenarbeit in der heutigen fachübergreifenden Umgebung zu implementieren, nutzen innovative Unternehmen die Altium 365™-Plattform, um Design-Daten einfach zu teilen und Projekte in die Fertigung zu bringen.

Wir haben nur an der Oberfläche dessen gekratzt, was mit Altium Designer auf Altium 365 möglich ist. Starten Sie heute Ihre kostenlose Testversion von Altium Designer + Altium 365.