Routing mit Fly-By-Netzwerktopologie bei DDR3- und DDR4-Speicher

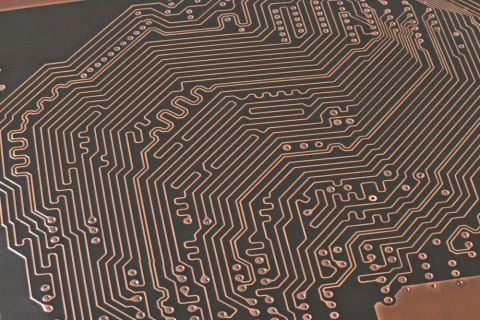

Die Netzwerktopologie des PCB-Layouts für einen DDR-Speicher sieht aus der “Vogelperspektive” komplex aus: Wenn Sie beim Aufrüsten Ihres PCs oder Laptops schon eimal Ihre RAM-Chips angeschaut haben, sehen Sie - womöglich mithilfe einer Lupe - auf der Oberfläche eine Vielzahl an Leiterbahnen, aber diese sind nur der Anfang eines komplizierten Netzwerks zwischen dem Randstecker und den eigentlichen RAM-Chips. Dennoch ist die Netzwerktopologie, wenn man sie einmal richtig verstanden hat, relativ simpel.

Eine dieser relativ einfachen Netzwerk-Topologien ist die Fly-By-Topologie. Das Layoutschema in der Fly-By-Topologie ist einer Doppel-T-Topologie aus verschiedenen Signalintegritätsgründen vorzuziehen. Die Fly-By-Netzwerktopologie verursacht weniger simultane Schaltgeräusche und die DDR-Protokolle können durch Unterstützung von Write-Leveling den Versatz verarbeiten, der im Fly-By-Routing entsteht. Außerdem funktioniert die Topologie auch bei Hochfrequenzanwendungen und reduziert die Anzahl und die Länge der Via-Stichleitungen.

Da die Fly-By-Topologie die beste Signalintegrität für DDR3- und DDR4-Speicher bietet, sollten wir darüber sprechen, was das für Ihre DDR-Routing-Richtlinien bedeutet. Sehen Sie sich unsere Routing-Richtlinien für die DDR3 und DDR4 Fly-By-Topologie an, um mehr zu erfahren.

DDR-Layout: Doppel-T- vs. Fly-By-Topologie

Die Fly-By-Topologie nutzt eine Verkettungsstruktur, die entweder sehr kurze oder gar keine Stichleitungen enthält. Aufgrund dieser Struktur weist die Fly-By-Topologie weniger Verzweigungen und Punktverbindungen auf. Beim Routing von DDR3 und DDR4 beginnt die Fly-By-Topologie mit dem Controller bei Chip 0 und führt das Routing bis Chip N bzw. bis zum oberen Datenbit fort. Das Routing erfolgt in der Reihenfolge der Byte-Lane-Zahlen, und die Daten-Byte-Lanes werden jeweils auf derselben Lage geführt. Das Routing kann bei Bedarf vereinfacht werden, indem die Daten-Bits innerhalb einer Byte-Lane ausgetauscht werden. Eine Darstellung der Fly-By-Topologie finden Sie unten.

Eine alternative Topologie für das Layout und Routing von DDR-Speicher ist die Doppel-T-Topologie. In dieser Topologie verzweigen sich die differentiellen Takt-, Befehls- und Adressleitungen vom Speicher-Controller alle in einer T-Struktur, die 2 Chips unterstützen kann. Jede Verzweigung könnte sich nochmals aufteilen, um jeweils 2 Chips zu unterstützen – also insgesamt 4 Chips. Allgemein können mit einer Doppel-T-Topologie 2^N Chips verbunden werden (N = Anzahl der Verzweigungen). Jeder Abschnitt wird dann an einen einzelnen RAM-Chip geroutet. Die Strobe- und Datenleitungen werden direkt vom Speichercontroller zu den jeweiligen RAM-Chips geroutet. Die Darstellung dazu finden Sie im folgenden Diagramm.

T-Topologien waren beim Routing von DDR2-Speicher gängig, doch jede Verzweigung erzeugte mit den DDR2-Frequenzen aufschaukelnde Impedanzunterschiede. Aus diesem Grund wird die Fly-By-Topologie bei DDR3 und späteren Generationen vorgezogen; pro Gerät entsteht hier nur eine Verzweigung für die CLK-/Befehls-/ADDR-Leitungen. Insbesondere eignet sich die Fly-By-Topologie für RAM-Geräte mit einer Matrix. Bei Geräten mit mehreren Matrizen können beide Topologien eingesetzt werden. Sie haben etwas Wahlfreiheit zwischen diesen Topologievarianten, jedoch ist das Routing bei DDR3 und DDR4-Speichern mit der Fly-By-Topologie einfacher und es gibt deutliche Vorteile für die Signalintegrität.

Fly-By-Technologie im DDR-Layout und Routing-Richtlinien

Bei der Verwendung einer Fly-By-Topologie sollten Sie einige grundlegende Richtlinien beim Routing von Leiterbahnen berücksichtigen, um die Signalintegrität zu gewährleisten. Die erste Richtlinie betrifft Ihren Lagenaufbau und die Chip-Ausrichtung. Wenn Sie genug Platz auf der Platine haben, sollten die ADDR-/Befehls-/Steuerungs-/CLK-Leitungen in derselben Lage geroutet werden. Sie können bei Bedarf jedoch Platz sparen, indem Sie das Routing auf verschiedenen Lagen durchführen. Das Routing für ADDR/Befehl/Steuerung/CLK erfolgt vom niedrigsten Datenbit-Chip zum höchsten Datenbit-Chip. Sie sollten mindestens 200 mils Platz zwischen den Speicherchips haben. Zudem sollten Sie am letzten SDRAM-Gerät in der Kette einen Differenzialendpunkt mit 100 Ω platzieren.

Wenn Sie Ihre Komponenten platzieren, müssen Sie Platz für Fanout, Endpunktwiderstände und Endpunktstromversorgung lassen. Außerdem sollten Sie das Routing über leere Vias in der Ebene vermeiden. Sie sollten die Vias verteilen und Platz für das Routing von mindestens zwei Leiterbahnen zwischen den Vias lassen. Wenn Sie den Fanout verteilen, steigern Sie die Anzahl der Leiterbahnkanäle.

Beachten Sie, dass bei der Fly-By-Topologie mit Absicht etwas Versatz zwischen den Lanes geschaffen wird. Auf diese Weise wird das gleichzeitige Schaltrauschen reduziert, wenn ein Chip schaltet. Das wiederum sorgt dafür, dass naheliegende Chips nicht vom Rauschen betroffen sind, weil es eine Verzögerung zwischen den Schaltereignissen in den verschiedenen Chips gibt. Zusätzlich zu diesem Vorteil für die Signalintegrität gibt es weitere Punkte, die Sie beim Routing von DDR3- und DDR4-Geräten berücksichtigen sollten.

Signalintegrität im Fly-By-Routing für DDR3 und DDR4

Wenn Sie das Routing in den inneren Lagen vornehmen, können Sie für die differentiellen Paare Streifenleitungen und doppelte Streifenleitungen verwenden. Leiterbahnen an der Oberfläche sollten als Mikrostreifen geroutet werden. Alle Leitungen benötigen eine Impedanzregelung, um Reflektionen an Verbindungsstellen und am Empfänger zu unterdrücken. Für die Leiterbahnen werden 50–60 Ω Widerstand an einzelnen Endpunkten (100–120 Ω für differentielle Endpunkte) bei den meisten Schnittstellen empfohlen. Beachten Sie, dass die JEDEC-Spezifikation für DDR3 mit 34 und 40 Ω zwei Stärken für I/Os mit Einzelendpunkten vorgibt. Allerdings nutzen moderne Geräte die On-Die-Terminierung, um die Widerstandswerte der entsprechenden Eigenschaft zu übernehmen. Sehen Sie sich unbedingt die Widerstandswerte Ihrer Komponenten am Eingang und Ausgang an und setzen Sie gegebenenfalls Endpunkte.

Für eine bessere Signalintegrität und engere Grenzen können Sie die Daten-Byte-Lanes bündeln. Das vereinfacht Ihr Routing-Verfahren. Achten Sie jedoch auf die Abstände zwischen den Leiterbahnen in den Lanes, um ein Übersprechen auf der Lane zu verhindern. Die Länge gebündelter Signale sollte basierend auf den Richtlinien in Ihren Gerätedatenblättern sorgsam angeglichen werden. Aber passen Sie auf: Bei den Datenblättern wird normalerweise ein Dk-Wert von 4 für das Substratmaterial angenommen. Wenn Sie auf einem alternativen PCB-Substratmaterial routen, müssen Sie den Längenabgleichswert anpassen, um die zulässige Zeitverzögerung (oder Phasenverzögerung bei differentiellen Paaren) auszugleichen.

Beim Leiterbahnabstand geben viele Richtlinien unterschiedliche Werte an, diese können jedoch leicht aus dem Kontext gerissen werden. Achten Sie bei der Auswahl des Abstands zwischen Leiterbahnen und Paaren auf Anwendungshinweise, da oft ein bestimmter Lagenaufbau vorausgesetzt wird. Der genaue Abstand zwischen den jeweiligen Enden differentieller Paare sollte so gewählt werden, dass Sie den nötigen differentiellen Widerstandswert wahren. Breitere Leiterbahnen können ein dichteres Routing verkraften, da sie eine geringere Induktivität aufweisen – die Hauptursache von Übersprechen bei DDR-Frequenzen. Am besten führen Sie Übersprechungssimulationen durch und loten Ihre Grenzen bei den Abständen zwischen differentiellen Leiterbahnen und solchen mit einzelnen Endpunkten aus.

Altium Designer® beim Fly-By-Routing

Angesichts der Komplexität vieler Leiterbahnen sollten Sie den Schaltplan als Grundlage für Ihr Design nutzen. Mit dem Schaltplan können Sie wichtige Komponenten und Netze ausmachen. Mit diesem Verfahren können Sie die Querauswahl und das Cross-Probing von Schaltplankomponenten und -netzen anwenden, um das Element auch auf der Leiterplatte zu markieren. Diese Funktionen helfen Ihnen gemeinsam mit Ihren Designregeln dabei, differentielle Paare zu erkennen, die einen Längenabgleich benötigen, und den vorgegebenen Widerstandswert und die nötigen Abstände beim Routing einzuhalten.

Lesen Sie diese weiterführenden Artikel, um mehr über DDR3/DDR4-Routing und -Layout zu erfahren:

- DDR3-Speicherschnittstellen und -Topologien im PCB-Design

- Routing von DDR3-Speicher und CPU-Fanout

- Altium Academy – virtuelle Sessions: Tech Track – DDR- und BGA-Routing und -Fanout

Hochgeschwindigkeits-PCB-Designs sind komplex und erfordern eine ausgefeilte Planung für die Platzierung von Komponenten und das Widerstandsmanagement. Altium Designer bietet Ihnen ein umfassendes, regelbasiertes Toolset für das interaktive Routing der Fly-By-Topologie in Ihren DDR3- und DDR4-Layouts. Allgemein sollten Sie Leiterbahnen anlegen, die einen direkten Pfad und eine Verbindungslösung für jede Bus-Seite ergeben. Die CAD-Funktionen im PCB Editor von Altium Design erleichtern Ihnen das Erstellen Ihres DDR3- oder DDR4-Layouts, um für Signalintegrität und einfaches Routing zu sorgen.

Wenn Sie mehr über das Routing einer Fly-By-Topologie für Ihre DDR3- und DDR4-Speichergeräte erfahren möchten, sprechen Sie mit einem Experten bei Altium.