Leitfaden zur Kantenmetallisierung bei PCBs in HF-Design

Einige Designs nutzen eine Randbeschichtung um das Äußere einer Leiterplatte, bei der die Seitenwände des PCB-Substrats mit Kupfer beschichtet werden. Die bei HF-PCBs verwendete Kupferbeschichtung wird aus mehreren Gründen aufgebracht, wie zum Beispiel die Bereitstellung einer Erdungsverbindung zu einem abgeschirmten Gehäuse oder das Eindämmen elektromagnetischer Felder. Wenn Sie feststellen, dass Sie eine Randbeschichtung einbeziehen müssen, wie sollten Sie dies in Ihrem PCB-Layout und den Fertigungsdaten spezifizieren?

Dieser Artikel gibt einen kurzen Überblick darüber, wie Sie eine Randbeschichtung in Ihrem PCB-Layout anwenden, sowie darüber, wie die Randbeschichtung in Ihren Fertigungslieferungen aussehen wird. Stellen Sie sicher, dass Sie diese Designregeln für eine erfolgreiche Anwendung der Randbeschichtung in Ihrem PCB-Layout befolgen.

Designregeln für Randbeschichtung

DFM-Regeln

Die erste wichtige Gruppe von Designregeln sind die DFM-Regeln für Randbeschichtung. Die Randbeschichtung wird typischerweise auf zwei Arten angewendet. Die erste Methode wendet die Randbeschichtung als separate Kupferstruktur an, die von anderen Kupferflächen auf der PCB getrennt ist. Dies kann durchgeführt werden, wenn ein Schutzring um den Rand einer Leiterplatte angebracht wird, was typischerweise beim Anbringen eines Chassis-Erde erfolgt.

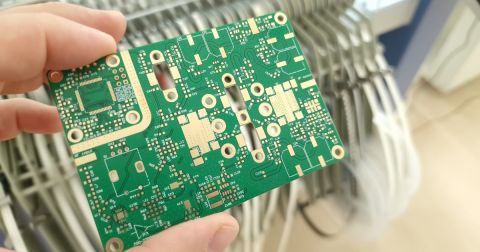

Das Bild unten zeigt typische Anbringungsabstände und Freiräume, die zwischen dem Kupferauftrag im Inneren der Platine und der Randbeschichtung angewendet werden müssen. Beachten Sie, dass der Auftrag, der die Randbeschichtung definiert, um etwa 0,5 mm über den Platinenrand hinausgeht; dies kann im PCB-Layout mit einer Designregel widergespiegelt werden (siehe unten).

Im oben genannten Fall würde die Randbeschichtung angewendet, indem sie ihrem eigenen Netz zugewiesen wird. Wenn Sie dem Ring einen eigenen Netznamen geben, können Sie eine netzspezifische Freiraumregel für den Platinenrand erstellen, die es dem Auftrag erlaubt, über den Platinenumriss hinauszugehen. Sie können diese Regel auch verwenden, um den erforderlichen Freiraum zwischen der Randbeschichtung und dem nicht verbundenen Kupfer festzulegen.

Die andere Option besteht darin, eine Polygon-Pour-Schicht komplett um den gesamten Rand der PCB herum und zurück zur anderen Oberflächenschicht zu wickeln. In diesem Fall würde der gleiche Freiraum auf der oberen Schicht immer noch gelten, genau wie wir es in der anderen Anordnung hatten. Das oben Genannte würde typischerweise nicht mit einem Gehäusegrund verwendet, sondern würde nur für ein System GND gelten.

Im PCB-Layout

Um die Randbeschichtung im PCB-Layout anzuwenden, muss die Beschichtung mit einem Polygonzug definiert werden. Der Polygonzug kann dann bis zum Rand der Leiterplatte geführt werden. Die übliche Praxis in ECAD-Software besteht darin, den Kupferzug über den Rand der Leiterplatte hinaus zu erweitern. Die Erweiterungsdistanz der Kupferbeschichtung über den Rand kann klein sein, typischerweise um den in den obigen Bildern gezeigten Abstand von 20 mil/0,5 mm.

Um dies in Altium Designer zu tun, können Sie eine Board Outline Clearance-Regel festlegen. Wenn Sie den Freiraum auf einen negativen Wert setzen, wird es dem Polygon erlaubt, außerhalb des Platinenrands zu fließen.

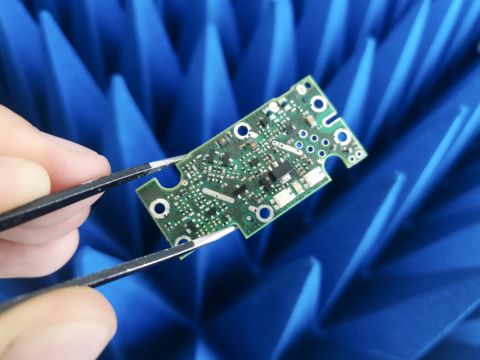

Wenn Sie randmontierte Steckverbinder im PCB-Layout haben, seien Sie vorsichtig, nachdem Sie die Polygonerweiterung über den Platinenrand angewendet haben. Das Polygon kann sich um das Pad erweitern und das Potenzial für einen Kurzschluss schaffen; dies könnte bei der Mittelmontage für einen SMA-Randsteckverbinder erwartet werden. Um dieses Problem zu verhindern, verwenden Sie eine Polygon-Ausschnittregion um das Pad, um die Randbeschichtung in dieser Region zu verhindern.

Der oben beschriebene Prozess wird für die Kantenmetallisierung gezeigt, gilt aber auch für Ausschnitte im Innenbereich der Leiterplatte. Sobald der Metallisierungsbereich definiert und die Designregeln festgelegt sind, entfernen Sie die Lötstopplack entlang der Kante, damit der Bereich für die Metallisierung zugänglich ist. Dies stellt auch sicher, dass die Metallisierung bei Bedarf Kontakt mit externem Metall aufnehmen kann, wie es beispielsweise in einem abgeschirmten Gehäuse erforderlich ist.

Fertigungsdaten

Sobald Sie Ihre Fertigungsdateien exportieren, erscheint das Kupfer über den Rand der Platinenkonturschicht. Typischerweise würde Ihnen ein Fertiger eine E-Mail senden, um Fragen zu stellen und sicherzustellen, dass es keinen Fehler in Ihren Design-Dateien gab. Um sicherzustellen, dass Sie schnell in die Fertigung kommen können, ohne diese Designfragen zu bekommen, sollten Sie sicherstellen, dass Ihre Bauanforderungen richtig kommuniziert werden.

Um dies zu tun, fügen Sie eine Notiz in Ihre Fertigungszeichnung ein. Sie sollten etwas wie Folgendes einbeziehen:

- METALLISIERUNG ENTLANG DER PLATINENKANTE. FERTIGE DICKE DER KANTENMETALLISIERUNG X MIL +/- Y MILS.

Schließlich, wenn Sie ein Angebotsformular für Ihre Bestellung ausfüllen müssen, stellen Sie sicher, dass die Kantenmetallisierung auf dem Angebotsformular enthalten ist, damit es keine Unklarheiten bezüglich Ihrer Designabsicht gibt.

Immer wenn Sie einzigartige Kupferstrukturen in einem RF-PCB-Layout platzieren müssen, einschließlich Kantenmetallisierung, nutzen Sie das komplette Set an PCB-Design- und Produktionswerkzeugen in Altium Designer®. Sobald Sie Ihr PCB-Layout fertiggestellt haben und bereit sind, Ihre Fertigungsunterlagen zu teilen, können Sie Daten einfach austauschen und Dateien mit Ihrem Team über die Plattform Altium 365™ freigeben.

Wir haben nur an der Oberfläche dessen gekratzt, was mit Altium Designer auf Altium 365 möglich ist. Starten Sie heute Ihre kostenlose Testversion von Altium Designer + Altium 365.