Was ist der JESD204C-Standard für ADCs/DACs?

Serielle Schnittstellen hatten Schwierigkeiten, mit den Anforderungen von Hochgeschwindigkeits-Datenwandlerkomponenten, nämlich ADCs und DACs, Schritt zu halten. Eine Möglichkeit, dies zu bewerkstelligen, waren früher LVDS-Verbindungen zwischen Datenwandlern und einem Host-Controller. Diese Verbindungen würden hohe Datenraten über differentielle Paare zu einem einzelnen Gerät bieten und so einen schnellen Datentransfer von schnell abtastenden ADCs ermöglichen. Später veröffentlichte JEDEC die JESD204-Spezifikation, und sie wurde seitdem in viele Komponenten als Datenwandler-Schnittstelle integriert.

Die aktuellste Iteration der JESD204-Schnittstellenstandards, derzeit JESD204C, bringt extreme Datenraten zu schnellen ADC/DAC-Komponenten, die verwendet werden, um Signale mit sehr hohen Abtastraten zu sampeln. Jetzt, da die neueste Iteration des Standards seit etwas mehr als 2 Jahren existiert, gibt es viele Komponenten, die mit FPGAs verwendet werden können, um ultraschnelles Sampling, Übertragung und DSP in RF-Systemen zu ermöglichen.

Übersicht über JESD204C

Der JESD204C-Standard ist die neueste Iteration des allgemeinen JESD204-Standards, der von JEDEC veröffentlicht und gepflegt wird. Der Standard wurde entwickelt, um die Verwendung von LVDS-Verbindungen zwischen Datenwandlern und ihren Systemhosts zu ersetzen. Er definiert eine serielle Schnittstelle und ein Protokoll, das bei ADCs/DACs mit hoher Abtastrate für die Signalerfassung, -synthese und -synchronisation verwendet wird. Der Aspekt der Synchronisation ist für diese Schnittstelle wichtig, da sie es einem einzelnen Host-Controller ermöglicht, die Signalerfassung und -synthese über mehrere Geräte hinweg zu synchronisieren.

Einige der primären Betriebsparameter, die in der physischen Schicht implementiert sind, sind in der untenstehenden Tabelle aufgeführt. Die aktuelle JESD204C-Iteration verbessert die Datenrate und die Kodierungseigenschaften der vorherigen JESD204B-Iteration, die eine 8b/10b-Kodierung mit einer maximalen Datenrate von 12,5 Gbps verwendete. Diese Schnittstelle findet sich in ADCs/DACs, die mit einer Geschwindigkeit von 100 MSps bis 1 GSps oder höher arbeiten.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Beispieltopologie

Die Topologie einer JESD204C-Schnittstelle hängt von der Unterklasse der Schnittstelle ab. JESD204B führte die Unterklasse 1 und 2 ein, um eine Synchronisationsstrategie namens deterministische Latenz zu implementieren. Diese Strategie erreicht eine Synchronisation über Geräte hinweg, indem die Phasenabweichung zwischen den Datenströmen, die an den Host-Controller gesendet werden, bestimmt wird.

- Unterklasse 0 - Keine Unterstützung für deterministische Latenz (rückwärtskompatibel mit JESD204A)

- Unterklasse 1 - Deterministische Latenz erreicht durch Verwendung eines externen Referenzoszillators (SYSREF) als Zeitsignal

- Unterklasse 2 - Deterministische Latenz erreicht durch Verwendung eines SYNC-Pins zwischen dem Host-Controller und dem ADC/DAC

Zwei Implementierungen der Schnittstelle werden in der Grafik unten gezeigt.

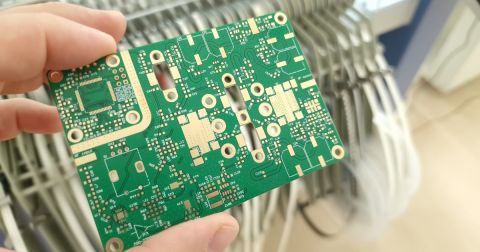

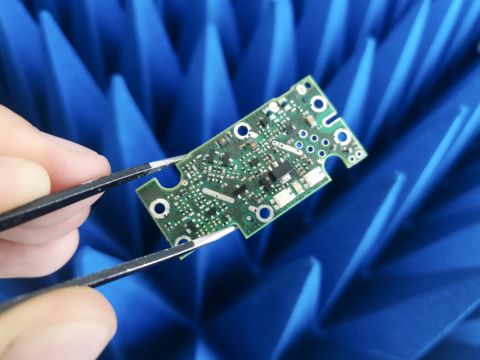

DATA1 und DATA2 werden als differentielle Paare geroutet; jede Spur in diesen I/O-Gruppen ist ein differentielles Paar, und ein gegebenes Gerät könnte mehrere Spuren haben (einige Produkte haben bis zu 8 pro Gerät). In beiden Untergruppen wird die Taktquelle auf alle Geräte in einer quellsynchronen Weise geroutet. Zeitliches Timing und deterministische Latenz werden in jeder Untergruppe durch angemessenes Abgleichen von SYSREF und DCLK/SYNC zu Setup- und Haltezeiten erreicht, sowie zueinander, wenn sie über mehrere Datenwandler verteilt sind.

Routing, Deskew und Latenz

Deterministische Latenz wurde oben erwähnt: Dies ist die Technik, mit der ein einzelner Host-Controller die Datenerfassung und -synthese über mehrere Geräte mit präzisem Timing synchronisieren kann, sodass die Zeitverzögerung zwischen den Abtastframes bekannt ist. Dies wird korrigiert, indem Spurverzögerungen aufeinander abgestimmt werden, so dass die Verzögerungen zwischen ihnen angeglichen sind. Eine JESD204B- oder JESD204C-Schnittstelle verwendet Verzögerungsabgleich in den Steuerbits, die von SYSREF (in Untergruppe 1) oder von den SYNC-Pins (in Untergruppe 2) stammen.

Die Tabelle unten skizziert die Anforderungen an die Längen-/Verzögerungsabgleichung in den Timing-Signalen für jede Untergruppe in den JESD204B- und JESD204C-Schnittstellen.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Der Hauptunterschied hier ist, wie die SYNC-Netze behandelt werden. In Unterklasse 1 werden diese Netze nur für die Synchronisation von Codegruppen verwendet, während sie in Unterklasse 2 auch für das Timing verwendet werden. Daher hat JESD204C weniger Signale für eine gegebene Anzahl von I/O-Kanälen in den Datenwandlern.

Warum JESD204C gegenüber LVDS?

Der Vorteil der JESD204C-Schnittstelle für Hochgeschwindigkeits-Sampling und -Synthese bei GHz-Frequenzen liegt in der Fähigkeit, Skew und Latenzunterschiede über mehrere Wandler hinweg zu eliminieren. Es gibt ein gewisses Skew-Budget für jede JESD204-Schnittstelle, welches die maximale Menge an Skew darstellt, die im System-Timing-Schema kompensiert werden kann, um deterministische Latenz innerhalb der Grenzen des Phasenrauschens zu garantieren. Das Ziel ist es, sicherzustellen, dass der Host-Controller die Phasenunterschiede der resultierenden eingehenden Datenströme kennt und diese in der Logik kompensieren kann, um so das wahre Timing zwischen den abgetasteten Signalen herzustellen.

Ein weiterer Grund für die Verwendung von JESD204C ist, dass es die Routing- und Timing-Anforderungen im PCB-Layout reduziert. In einer typischen Implementierung werden die DATA1 und DATA2 Differenzpaare, die von Gerät 1 und Gerät 2 kommen, etwas Skew aufweisen. Mit LVDS würde dies erfordern, dass passende Differenzpaare parallel zueinander verlaufen. Bei JESD204C müssen wir nur den Skew über die DCLK- und SYSREF/SYNC-Netze eliminieren, aber nicht die Daten-Netze über die Geräte hinweg. Dies macht die Schnittstelle unerlässlich in hochdichten Mixed-Signal-Geräten.

Designer, die fortschrittliche Technologien für die Luft- und Raumfahrt entwickeln, können den JESD204C-Standard mit den branchenführenden Produktdesign-Tools in Altium Designer® implementieren. Wenn Sie Ihr Design abgeschlossen haben und Dateien an Ihren Hersteller weitergeben möchten, erleichtert die Altium 365™-Plattform die Zusammenarbeit und das Teilen Ihrer Projekte.

Wir haben nur an der Oberfläche dessen gekratzt, was mit Altium Designer auf Altium 365 möglich ist. Starten Sie heute Ihre kostenlose Testversion von Altium Designer + Altium 365.