Pautas para la colocación de condensadores de desacoplamiento y bypass

Los problemas de integridad de potencia normalmente se ven desde la perspectiva de la fuente de alimentación, pero observar la salida de los circuitos integrados es igual de importante. Los capacitores de desacoplamiento y bypass (o derivación) están destinados a compensar las fluctuaciones de potencia observadas en la PDN, lo que asegura que tus niveles de señal sean consistentes y se vea una tensión constante en los pines de alimentación/tierra en un circuito integrado. Hemos compilado algunas pautas de diseño importantes para capacitores de bypass y condensadores de desacoplo (o capacitores de desacoplamiento) para ayudarte a utilizar estos componentes con éxito en tu próxima PCB. En este artículo, abordaremos la diferencia entre capacitor de bypass y capacitor de desacoplamiento, conocido también como condesador de desacoplo).

Dos Problemas Relacionados con la Integridad de Potencia

Los capacitores de desacoplamiento y de derivación se utilizan para resolver dos problemas diferentes de integridad de potencia. Aunque estos problemas de integridad de potencia están relacionados, se manifiestan de manera distinta. El primer punto a tener en cuenta es que los términos "capacitor de desacoplamiento" y "capacitores de derivación" cuando se usan para la integridad de potencia son inapropiados; no desacoplan ni derivan nada. Tampoco pasan el "ruido" a tierra; simplemente se cargan y descargan con el tiempo para compensar las fluctuaciones de ruido. Estos términos se refieren a las funciones de estos capacitores como parte de una estrategia de integridad de potencia.

Primero, considera los capacitores de desacoplamiento. Generalmente se afirma que el propósito de la colocación de capacitores o condensadores de desacoplamiento en la placa de circuito impreso (PCB) es asegurar que la tensión entre el riel/plano de potencia y el plano de tierra permanezca constante frente al ruido de baja frecuencia de la fuente de alimentación, el resonar en la PDN, y cualquier otra fluctuación tensión en la PDN. Cuando se colocan entre los planos de potencia y tierra, un capacitor de desacoplamiento está en paralelo con los planos, lo que aumenta la capacitancia total de la PDN. En efecto, compensan la insuficiente capacitancia entre planos y reducen la impedancia de la PDN de tal manera que cualquier resonancia en la tensión de la PDN se minimiza.

Ahora consideremos los capacitores o condensadores de desacoplo.También están destinados a mantener una tensión constante dentro de una PDN y un circuito integrado (IC) de control, pero la tensión que compensan es entre el pin de salida y el plano de tierra del PCB. Aunque los condensadores de desacoplo se colocan entre un pin de alimentación y una conexión a tierra en un IC, estos realizan una función diferente, que es combatir el rebote de tierra del capacitor. A medida que un IC digital cambia, la inductancia parásita en el alambre de unión, el paquete y el pin hace que la tensión entre la salida del controlador y la tierra aumente. Los capacitores de desacoplo emiten una tensión que apunta en dirección opuesta a la tensión de rebote de tierra, idealmente causando que la fluctuación total de tensión sume cero.

En el modelo anterior, hay un bucle cerrado que incluye el condensador de derivación (CB) y la inductancia parásita L1 en la conexión del paquete del IC/tierra. Nota que el la tensión de rebote de tierra V(GB) se mide entre el pin de salida y el plano de tierra. Las demás inductancias son todas parásitas, las cuales afectan el tiempo de respuesta del condensador de derivación para compensar un rebote de tierra. En un modelo ideal, el voltaje visto por el condensador de derivación compensará el voltaje de rebote de tierra creado por el inductor parásito L1 durante el conmutación.

Guía para la Colocación del Condensador de Derivación

Si observas la forma en que ocurre el rebote del capacitor a tierra, debería ser obvio dónde colocar los condensadores de desacoplo. Debido a la inductancia parásita en el modelo de circuito anterior, un condesnador de desacoplo debe colocarse lo más cerca posible de los pines de alimentación y tierra para minimizar estas inductancias. Esto es consistente con el consejo que encontrarás en muchas notas de aplicación y hojas de datos de componentes.

Hay otro aspecto a considerar, relacionado con las inductancias parásitas, que es cómo se realiza la conexión al CI. En lugar de trazar una pista corta desde el capacitor hasta los pines del CI, debes conectar el condesnador directamente a los planos de tierra y alimentación a través de vías. Asegúrate de cumplir con los requisitos de espaciado de pads y pistas en esta disposición.

¿Por qué es este el caso? La razón es que la disposición de las capas de tierra/alimentación (siempre que las capas estén adyacentes) tendrá una inductancia parásita muy baja. De hecho, esta es la fuente más baja de inductancia parásita en tu placa. Podrías ser capaz de implementar una mejor disposición si puedes colocar tu condesnador de desacoplo en el lado inferior de la placa de PCB.

Directrices de Diseño de Capacitores o Condensadores de Desacoplo

Después de determinar el tamaño del condensador de desacoplamiento del PCB que necesitas en tu PDN, necesitarás colocarlo en algún lugar para asegurarte de que pueda compensar las fluctuaciones de la tensión de entrada. De hecho, es mejor usar varios, ya que se dispondrán en paralelo, y la disposición en paralelo proporcionará una inductancia en serie efectiva más baja.

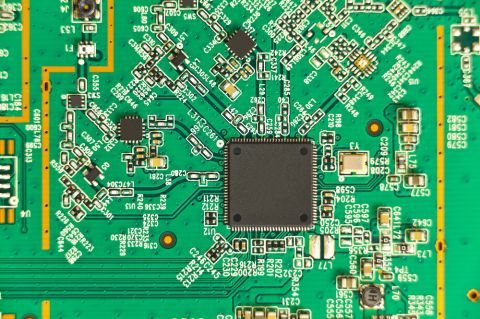

Las guías antiguas indicarían que puedes colocarlos en cualquier parte de la placa de PCB. Sin embargo, ten cuidado con esto ya que esto puede aumentar la inductancia parásita vista entre el condensador de desacoplamiento y el CI objetivo, lo que aumenta la impedancia de la PDN y la susceptibilidad a la EMI. En cambio, para los CI con tasas de transición rápidas, deberías colocarlos más cerca del CI objetivo. La imagen a continuación muestra una disposición típica de bypass y capacitor de desacoplamiento cerca de un CI. Esta es una disposición óptima para circuitos de PCB alta velocidad ya que habrá muy baja inductancia parásita entre los condensadores y el CI para todos los caminos de señal.

Tenga en cuenta que esta es una vista lateral y muestra una disposición aparentemente extraña de las almohadillas, pero los puntos importantes son las conexiones entre los planos y la capa superficial. Enrutar de vuelta hacia la capa interior en lugar de la capa superficial mantiene la inductancia de bucle al mínimo.

Ten Cuidado al Modelar la Impedancia de PDN

Recuerda que la impedancia de la PDN determina el tamaño de cualquier resonancia de tensión transitoria en la PDN (medida entre alimentación y tierra). Sin embargo, los condesadores de derivación (bypass) también están conectados entre alimentación y tierra, ¡así que también son parte de la PDN! La colocación de los capacitores o condensadores de derivación y desacoplamiento, así como las capacitancias e inductancias parásitas, determinarán colectivamente el espectro de impedancia de la PDN, creando una estructura complicada de resonancias y anti-resonancias.

Aunque puedes encontrar algunas herramientas de optimización de PDN online, asumen que todos los elementos de circuito parásitos son cero, lo cual no coincide con la realidad. En un modelo de circuito, no importa cómo organices tus condensadores de desacoplamiento y derivación (de pequeño a grande o de grande a pequeño). En un diseño de PCB real, los parásitos importan (como se discutió anteriormente), especialmente para ICs de alta velocidad/bajo nivel.

Con las herramientas de diseño de esquemáticos y distribución en Altium Designer®, puedes implementar fácilmente las mejores pautas de diseño de condesadores de desacoplo y derivación (bypass) en tu próximo PCB. El conjunto de herramientas de simulación de circuitos puede ayudarte a tener una idea de la estructura de resonancia de tu PDN. También tendrás acceso a una amplia gama de herramientas para la gestión de datos de componentes y la preparación para la producción, así como información sobre la elección entre un capacitor de volumen y un capacitor o condesador de desacoplo.

Ahora puedes descargar una prueba gratuita de Altium Designer y aprender más sobre las mejores herramientas de diseño de distribución, simulación y planificación de producción de la industria. Habla hoy mismo con un experto de Altium para saber más.