Diretrizes para Colocação de Capacitores de Desacoplamento e Bypass

Problemas de integridade de energia são normalmente vistos sob a perspectiva da fonte de alimentação, mas observar a saída dos ICs é igualmente importante. Capacitores de desacoplamento e bypass são destinados a compensar flutuações de energia vistas na PDN, o que garante que seus níveis de sinal sejam consistentes e uma tensão constante seja observada nos pinos de alimentação/terra de um IC. Compilamos algumas diretrizes importantes de design de capacitores de bypass e desacoplamento para ajudá-lo a usar esses componentes com sucesso em sua próxima PCB. Neste blog, abordaremos a diferença entre capacitor de bypass e capacitor de desacoplamento.

Dois Problemas Relacionados à Integridade de Energia

Capacitores de desacoplamento e de bypass são usados para resolver dois diferentes problemas de integridade de energia. Embora esses problemas de integridade de energia estejam relacionados, eles se manifestam de formas diferentes. O primeiro ponto a ser observado é que os termos “capacitor de desacoplamento” e “capacitores de bypass” quando usados para integridade de energia são imprecisos; eles não desacoplam ou fazem bypass de nada. Eles também não transmitem “ruído” para o terra; eles simplesmente carregam e descarregam ao longo do tempo para compensar as flutuações de ruído. Esses termos referem-se às funções desses capacitores como parte de uma estratégia de integridade de energia.

Primeiramente, considere os capacitores de desacoplamento. Geralmente se afirma que o propósito da colocação de capacitores de desacoplamento em PCB é garantir que a tensão entre o trilho/plano de alimentação e o plano de terra permaneça constante contra ruídos de baixa frequência da fonte de alimentação, ressonância na PDN, e quaisquer outras flutuações de tensão na PDN. Quando colocados entre os planos de alimentação e terra, um capacitor de desacoplamento está em paralelo com os planos, o que aumenta a capacitância total da PDN. Na prática, eles compensam a insuficiente capacitância entre planos e reduzem a impedância da PDN de tal forma que qualquer ressonância na tensão da PDN é minimizada.

Agora considere os capacitores de desacoplamento. Eles também têm como objetivo manter uma tensão constante dentro de uma PDN e um CI de controle, mas a tensão que compensam é entre o pino de saída e o plano de terra do PCB. Embora sejam colocados entre um pino de alimentação e uma conexão de terra em um CI, eles desempenham uma função diferente, que é combater o salto de tensão do capacitor para o terra. À medida que um CI digital comuta, a indutância parasita no fio de ligação, no encapsulamento e no pino faz com que a tensão entre a saída do driver e o terra aumente. Os capacitores de desacoplamento emitem uma tensão que aponta na direção oposta à tensão de salto para o terra, idealmente fazendo com que a flutuação total da tensão some zero.

No modelo acima, existe um loop fechado que inclui o capacitor de desvio (CB) e a indutância parasita L1 na conexão do pacote do CI/terra. Note que a tensão de salto de terra V(GB) é medida entre o pino de saída e o plano de terra. As demais indutâncias são todas parasitas, que afetam o tempo de resposta do capacitor de desvio para compensar um salto de terra. Em um modelo ideal, a tensão vista pelo capacitor de desvio compensará a tensão de salto de terra criada pelo indutor parasita L1 durante a comutação.

Diretrizes para Posicionamento do Capacitor de Desvio

Se você observar a maneira como ocorre o salto do capacitor para o terra, deveria ser óbvio onde colocar capacitores de desacoplamento. Devido à indutância parasita no modelo de circuito acima, um capacitor de desacoplamento deve ser colocado o mais próximo possível dos pinos de alimentação e terra para minimizar essas indutâncias. Isso está de acordo com o conselho que você encontrará em muitas notas de aplicação e folhas de dados de componentes.

Há outro aspecto a considerar, relacionado às indutâncias parasitas, que é como a conexão é roteada para o CI. Em vez de rotear um traço curto do capacitor para os pinos do CI, você deve conectar o capacitor diretamente aos planos de terra e alimentação através de vias. Certifique-se de cumprir com os requisitos de espaçamento de pad e traço nesta disposição.

Por que isso acontece? A razão é que a disposição da placa de terra/energia (contanto que as placas estejam em camadas adjacentes) terá uma indutância parasita muito baixa. De fato, esta é a fonte de indutância parasita mais baixa na sua placa. Você pode ser capaz de implementar um arranjo melhor se conseguir colocar seu capacitor de desacoplamento no lado inferior da placa.

Diretrizes de Design de Capacitores de Desacoplamento

Após determinar o tamanho do capacitor de desacoplamento da PCB que você precisa em sua PDN, será necessário posicioná-lo em algum lugar para garantir que ele possa compensar as flutuações de tensão de entrada. Na verdade, é melhor usar vários, pois eles serão dispostos em paralelo, e o arranjo paralelo fornecerá uma indutância série efetiva menor.

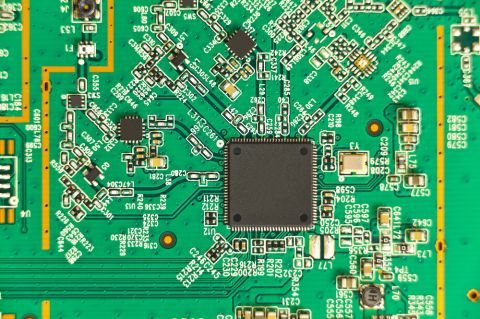

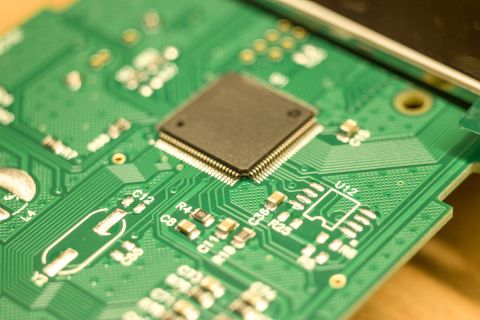

As orientações mais antigas afirmariam que você pode colocá-los em qualquer lugar na placa. No entanto, tenha cuidado com isso, pois isso pode aumentar a indutância parasita vista entre o capacitor de desacoplamento e o CI alvo, o que aumenta a impedância da PDN e a suscetibilidade a EMI. Em vez disso, para CIs com taxas de transição rápidas, você deve colocá-los mais próximos ao CI alvo. A imagem abaixo mostra um arranjo típico de colocação de capacitor de bypass e desacoplamento próximo a um CI. Este é um arranjo ótimo para circuitos de alta velocidade, pois haverá uma indutância parasita muito baixa entre os capacitores e o CI para todos os caminhos de sinal.

Note que esta é uma visão lateral e mostra um arranjo aparentemente estranho de pads, mas as conexões entre os planos e a camada superficial são os pontos importantes. Roteamento de volta para a camada interna em vez da camada superficial mantém a indutância de loop no mínimo.

Tenha Cuidado ao Modelar a Impedância da PDN

Lembre-se de que a impedância da PDN determina o tamanho de qualquer oscilação de tensão transitória na PDN (medida entre alimentação e terra). No entanto, os capacitores de desvio também estão conectados entre alimentação e terra, então eles também fazem parte da PDN! A colocação de capacitores de desvio e desacoplamento, bem como capacitâncias e indutâncias parasitas, determinarão coletivamente o espectro de impedância da PDN, criando uma estrutura complicada de ressonâncias e antirressonâncias.

Embora você possa encontrar algumas ferramentas de otimização de PDN online, elas assumem que todos os elementos de circuito parasitas são zero, o que não corresponde à realidade. Em um modelo de circuito, não importa como você organiza seus capacitores de desacoplamento/desvio (de pequeno para grande ou de grande para pequeno). Em um layout real, os parasitas importam (como foi discutido acima), especialmente para ICs de alta velocidade/baixo nível.

Com as ferramentas de layout e design esquemático no Altium Designer®, você pode facilmente implementar as melhores diretrizes de design para capacitores de desacoplamento e bypass em sua próxima PCB. O conjunto de ferramentas de simulação de circuitos pode ajudar a dar uma ideia da estrutura de ressonância da sua PDN. Você também terá acesso a uma ampla gama de ferramentas para gerenciamento de dados de componentes e preparação para produção, bem como informações sobre a escolha entre um capacitor de grande porte e um capacitor de desacoplamento.

Agora você pode baixar uma versão de avaliação gratuita do Altium Designer e aprender mais sobre as melhores ferramentas de layout, simulação e planejamento de produção do setor. Fale com um especialista da Altium hoje para saber mais.