Que spécifier pour l’intégrité des canaux : listes de contrôle pratiques pour les liaisons haut débit

La plupart des équipes découvrent les problèmes d’intégrité de canal lors de la mise sous tension initiale : un diagramme de l’œil qui paraissait propre en simulation se referme sur le banc, un connecteur donné pour le débit visé échoue dans la topologie réelle, ou une modification de l’empilage dégrade la marge sans que personne ne l’ait budgétée. Chacun de ces cas correspond à un échec de spécification qui se manifeste comme un problème d’intégrité du signal (SI). La solution consiste à définir l’intégrité de canal comme un ensemble d’exigences mesurables suffisamment tôt pour influencer l’architecture, puis à vérifier ces exigences à chaque phase de la conception.

Points clés

- L’intégrité de canal est d’abord un problème d’exigences. La marge se gagne ou se perd avec les choix de topologie, d’empilage et d’interconnexion.

- Les retimers, redrivers, connecteurs et câbles consomment chacun une partie de votre budget de canal. Spécifiez-les avec des valeurs d’IL, de RL, de diaphonie et de gigue directement liées à votre marge de liaison.

- Un plan de mesure fait partie de la spécification du canal. La stratégie de fixture et le de-embedding doivent être définis avant que le routage ne soit figé.

Ce que couvre réellement l’intégrité de canal

Un canal haut débit englobe l’ensemble du trajet électrique, des broches de l’émetteur à celles du récepteur, y compris les sorties de boîtier, les vias, les transitions entre plans de référence, les pistes, les connecteurs, les câbles et tout conditionnement actif présent sur le trajet. L’intégrité de canal est la capacité de ce trajet à respecter un taux d’erreur binaire (BER) cible dans des conditions réelles de tension, de température, de variation de procédé et d’interconnexion. Votre topologie, vos composants et votre méthode de validation doivent tous tenir la route, et les résultats doivent être reproductibles.

Chaque élément du trajet consomme une partie du budget de marge. Dès qu’un seul d’entre eux est sous-spécifié, les problèmes apparaissent tardivement et le cycle de débogage devient coûteux. Dans cet article, nous présentons un processus en huit étapes pour vous aider à comprendre quoi spécifier, comment le spécifier et ce qu’il faut exiger des fournisseurs de composants afin que vos résultats de simulation et de laboratoire convergent. En complément, nous fournissons des check-lists pratiques pour chaque étape du processus.

Pour examiner de plus près comment PCIe 7.0, l’Ethernet 800G, USB4 et le Wi-Fi 7 font remonter ces exigences en amont, consultez Les normes haut débit ne cessent de relever la barre.

Étape 1. Définissez la liaison que vous construisez réellement

Commencez par un court bloc de définition de liaison inclus dans vos exigences et dans votre plan de test.

Check-list de définition de la liaison

- Norme et objectif de débit (exemple : PCIe, Ethernet, USB4 ou SerDes propriétaire).

- Nombre de voies et attentes en matière d’agrégation de voies.

- Portée et topologie. Uniquement sur carte, carte à carte, câblé ou flyover.

- Budget de latence (en particulier si vous pourriez ajouter des retimers).

- Contraintes de puissance et thermiques aux emplacements probables de conditionnement.

- Contraintes environnementales et mécaniques (vibrations, accès pour maintenance).

Ces décisions constituent la base des exigences pour tous les choix en aval. Figez-les tôt et conservez-les dans votre plan de test.

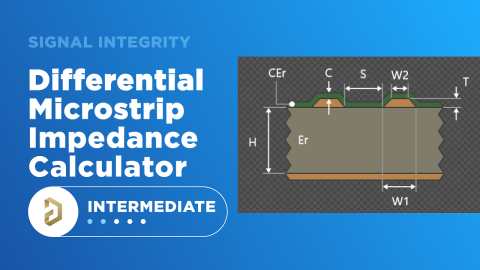

Étape 2. Établissez un budget avant le début du routage

Un budget de canal est l’ossature de la spécification. Il transforme des hypothèses optimistes en chiffres concrets que votre empilage, vos choix de connecteurs et votre plan de conditionnement peuvent réellement satisfaire.

Éléments du budget à inclure

- Perte d’insertion (IL) en fonction de la fréquence.

- Perte de retour (RL) en fonction de la fréquence.

- Objectifs de diaphonie : NEXT, FEXT et métriques en mode mixte (si vous les utilisez).

- Budget de skew : y compris les contributions du tissage de verre et des connecteurs.

- Objectifs de conversion de mode car l’énergie en mode commun se manifeste souvent sous forme d’EMI.

- Hypothèses de budget de gigue et niveau de récupération attendu grâce à l’égalisation.

Si vous ne pouvez pas exprimer une exigence sous forme de ligne budgétaire et de plan de référence, vous ne pourrez pas la valider proprement.

Étape 3. Retimers. Que spécifier lorsque vous avez besoin de CDR

Lorsque vous avez besoin de récupération d’horloge et de données (CDR), un retimer fournit un point de réinitialisation dans un canal. Il retransmet une version propre du signal, restaurant une marge que l’égalisation seule ne peut pas récupérer. Cette capacité s’accompagne de contraintes de conception que vous devez spécifier dès le départ.

Check-list de spécification d’un retimer

- Débits de données et protocoles pris en charge.

- Nombre de voies et flexibilité de mappage des voies.

- Latence (typique et pire cas).

- Tolérance à la gigue et comportement de transfert de gigue (comment le composant filtre ou laisse passer la gigue).

- Comportement et contrôles d’égalisation : préréglages statiques versus comportement adaptatif ; méthode de configuration et de supervision.

- États de puissance et caractéristiques thermiques.

- Exigences d’horloge de référence, le cas échéant.

- Exigences du trajet du signal : attentes en matière de couplage AC, contraintes de sortie de boîtier et recommandations de routage.

- Disponibilité des modèles : IBIS-AMI lorsque pertinent, ainsi que conceptions de référence et documentation d’évaluation.

Retimer mis en avant

Broadcom BCM85667 est un retimer PCIe Gen 6 et CXL 3.1 en technologie 5 nm, 16 voies, fonctionnant à 64 GT/s PAM4. Son descriptif produit documente les débits pris en charge, les options de bifurcation, les contrôles d’EQ et la compatibilité d’empreinte. C’est le niveau de détail de spécification que vous devriez attendre de tout retimer que vous qualifiez.

Étape 4. Redrivers. Que spécifier lorsque vous voulez une EQ linéaire

Un redriver fournit une égalisation linéaire et un conditionnement de sortie. Il n’effectue pas de récupération d’horloge. Ce compromis se traduit généralement par une latence plus faible et une intégration plus simple, avec une capacité moindre à réhabiliter un canal fortement dégradé.

Check-list de spécification d’un redriver

- Débit de données et bande passante pris en charge.

- Plage d’égalisation et taille des pas.

- Plage d’amplitude de sortie et contrôles de gain plat.

- Comportement en bruit et linéarité, surtout si vous risquez d’amplifier le bruit en même temps que le signal.

- Sensibilité d’entrée et gestion du mode commun.

- Interface de configuration et télémétrie.

- Contraintes de boîtier et de sortie de boîtier.

- Disponibilité des modèles et recommandations de routage de référence.

Redriver mis en avant

Le PI3EQX32908ZRIEX de Diodes est un redriver linéaire PCIe 5.0 à 8 canaux prenant en charge de 5 à 32 Gbit/s avec EQ programmable par canal, amplitude de sortie et contrôles de gain plat ; il prend également en charge les protocoles SAS4 et CXL.

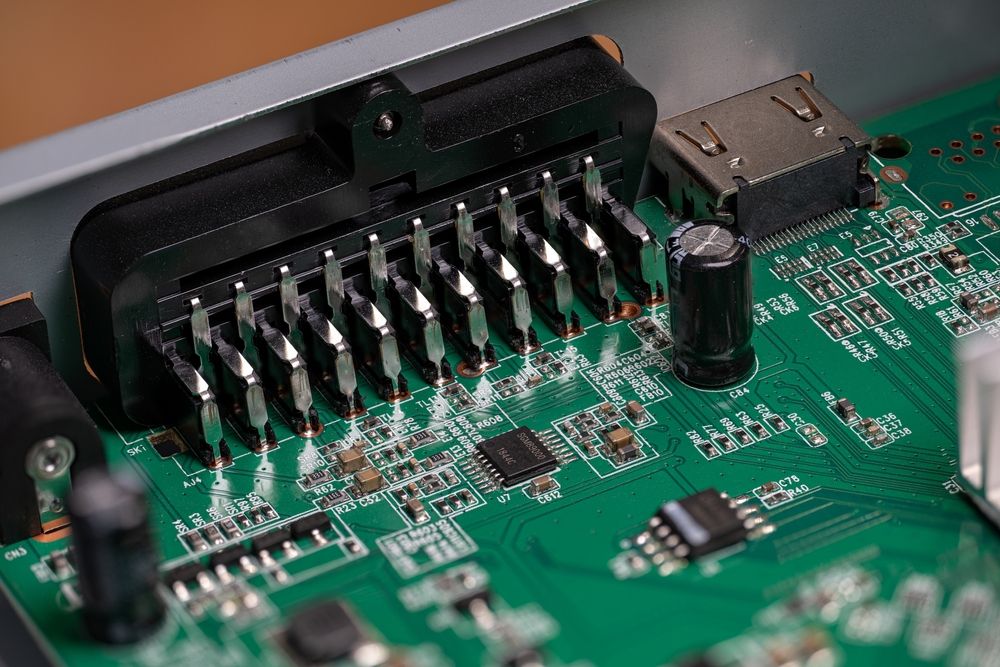

Étape 5. Les connecteurs comme composants du canal

À haute vitesse, le connecteur et ses transitions peuvent consommer une part disproportionnée de la marge ; ils méritent donc la même rigueur de spécification que n’importe quel autre composant du canal.

Check-list de spécification d’un connecteur

- Impédance différentielle cible et tolérance.

- IL et RL en fonction de la fréquence pour la paire accouplée et pour les transitions PCB.

- Comportement de diaphonie et recommandations d’isolation du champ de broches.

- Options de hauteur d’empilage et cumul des tolérances.

- Cycles d’accouplement et hypothèses de durabilité mécanique.

- Contraintes d’empreinte PCB et de breakout.

- Disponibilité des paramètres S et éventuelles recommandations de conception de référence.

- Plan de seconde source au niveau de l’interface.

Connecteurs mis en avant

Molex Mirror Mezz 202828-1506 est un connecteur mezzanine carte à carte hermaphrodite de 404 circuits, avec une hauteur d’empilage de 2,50 mm et un montage BGA, prenant en charge des débits jusqu’à 56 Gbit/s par paire différentielle. Il utilise une empreinte recommandée par l’OCP, commune à la famille Mirror Mezz, ce qui vous donne des données de paramètres S, une documentation d’empreinte et une visibilité chez les distributeurs que vous pouvez rattacher à votre modèle de canal et à votre revue de nomenclature.

Étape 6. Câbles et flyovers : spécifiez l’extension du canal

Les assemblages de câbles cuivre et les flyovers optiques actifs étendent tous deux la portée du canal au-delà de ce que les pistes sur carte peuvent offrir, mais ils résolvent des problèmes différents. Les câbles cuivre se comportent comme des lignes de transmission avec des contraintes d’impédance, de blindage et de rayon de courbure. Les flyovers optiques contournent entièrement les pertes diélectriques, mais introduisent des considérations de conversion électro-optique, de puissance, de thermique et de latence. Spécifiez l’approche exigée par votre budget de liaison et définissez ce que signifie une performance équivalente pour toute alternative envisagée.

Check-list de spécification d’un câble

- Impédance différentielle et skew.

- IL et RL en fonction de la fréquence, y compris les transitions à chaque extrémité.

- Efficacité du blindage et approche de mise à la masse.

- Contraintes de rayon de courbure et de soulagement de traction.

- Exigences de cycles d’accouplement et accès pour maintenance.

- Comportement passif versus actif, le cas échéant. Pour les flyovers optiques, spécifiez la longueur d’onde, le budget de puissance optique, la latence et la consommation par voie.

- Exigences de qualification et liste des câbles approuvés.

Assemblage flyover optique actif mis en avant

Samtec ECUO-B04-14-015-0-2-1-2-01 (le FireFly ECUO) est un assemblage flyover optique actif disponible en transceiver full-duplex 4 canaux à 28 Gbit/s par canal, ou en émetteur ou récepteur 12 canaux à 16 Gbit/s par canal. Avec de la fibre multimode OM3, il peut atteindre jusqu’à 100 mètres. Il contourne entièrement les pertes des pistes PCB et utilise le même système de micro-connecteurs que les assemblages flyover cuivre de Samtec, de sorte que l’empreinte reste identique si vous passez de l’optique au cuivre.

Étape 7. Matériaux à faibles pertes et cuivre : intégrez l’empilage dans la spécification

Les liaisons à plus large bande passante exigent que l’empilage soit une entrée de conception maîtrisée. Votre spécification de canal doit inclure des objectifs de matériaux et des plages acceptables, et elle doit préciser ce que vous supposez concernant la rugosité du cuivre et la capacité du procédé.

Check-list de spécification des matériaux et de l’empilage

- Objectifs de Dk et Df aux fréquences pertinentes, ainsi que la variation admissible.

- Hypothèses sur le profil de feuille de cuivre lorsque la perte conducteur est le facteur limitant.

- Contrôles du risque lié au tissage de verre et au skew pour les longues liaisons différentielles.

- Tg, Td et CTE selon l’axe Z si votre environnement ou votre profil d’assemblage est exigeant.

- Hypothèses sur les capacités du fabricant : rapports d’aspect de perçage, alignement, remplissage des vias et cycles de stratification.

- Figez le système de stratifié et exigez une revue explicite avant toute substitution.

Stratifiés faibles pertes mis en avant

Les familles de stratifiés Panasonic’s MEGTRON 7 et Isola’s I-Tera MT40 sont des exemples représentatifs de matériaux à pertes ultra-faibles et très faibles utilisés dans les canaux numériques à haute vitesse. Utilisez ces produits comme points de référence pour définir ce que vous attendez de tout stratifié sélectionné : des données électriques stables, des recommandations de mise en œuvre et une identification produit claire que vous pouvez figer dans les notes de fabrication.

Étape 8. Plan de mesure. Faire de la corrélation l’objectif

Votre plan de mesure doit définir les plans de référence, les montages, l’étalonnage et le de-embedding, afin de pouvoir comparer les résultats de simulation aux mesures sur banc sans ambiguïté. IEEE 370-2020 constitue une base pratique pour ce travail, en couvrant la qualité des données, les considérations liées aux montages et le de-embedding pour la caractérisation des PCB et des interconnexions jusqu’à 50 GHz.

Liste de contrôle du plan de mesure

- Ce que vous mesurerez : TDR pour le profil d’impédance, paramètres S mesurés au VNA pour les segments d’interconnexion, et diagramme de l’œil ou gigue à des points définis.

- Où vous mesurerez : Définissez les plans de référence et nommez-les.

- Comment vous étalonnerez : Indiquez la méthode d’étalonnage et la traçabilité.

- Comment vous ferez le de-embedding : Choisissez des méthodes que vous pouvez mettre en œuvre avec vos montages et vos outils.

- Comment vous corrélerez : Définissez les critères d’acceptation pour l’alignement entre simulation et mesure.

Plateforme de mesure mise en avant

Les analyseurs de réseau Keysight PNA-X couvrent des plages de fréquence allant de 900 Hz à 67 GHz (selon le modèle), avec plusieurs sources internes, des récepteurs de paramètres S et de bruit, ainsi qu’une compatibilité avec le logiciel PLTS de Keysight pour la caractérisation des interconnexions et le de-embedding.

Où Octopart s’intègre dans le flux de travail

Les composants liés à l’intégrité de canal ont souvent moins de véritables alternatives. Les familles de connecteurs, les circuits intégrés spécialisés de conditionnement et certains assemblages de câbles peuvent devenir les composants qui retardent une fabrication. Utilisez Octopart et le BOM Tool pour garder trois éléments liés tant que la conception reste flexible :

- La référence du composant et son statut de cycle de vie à jour.

- La documentation associée : fiches techniques, modèles et conceptions de référence.

- Les produits alternatifs et les options fournisseurs avant que les empreintes et les interfaces ne soient figées.

Plus tôt vous associez des données réelles de composants à votre modèle de canal, moins il restera d’hypothèses jusqu’à l’étape du routage. Un fichier de paramètres S de connecteur, une fiche produit de retimer ou un tableau Dk/Df de stratifié a plus de valeur qu’un simple espace réservé accompagné d’un plan visant à finaliser les choix plus tard. Octopart vous offre un emplacement pratique unique pour vérifier la disponibilité, récupérer les fiches techniques et confirmer le statut du cycle de vie pendant que la conception est encore suffisamment flexible pour intégrer ce que vous découvrez.

La discipline qui évite les nouvelles itérations de carte

L’intégrité de canal se construit à travers un ensemble de décisions prises lors de l’architecture, de la définition de l’empilage et de la sélection des interconnexions, puis se vérifie par simulation, mesure et corrélation avant et après le routage. Le fil conducteur est toujours le même : définissez ce dont vous avez besoin, spécifiez-le en chiffres, choisissez des composants accompagnés de données qui étayent ces chiffres, et rédigez le plan de mesure avant que le routage ne soit figé. Les équipes qui appliquent cela de manière constante sont celles qui évitent une nouvelle itération.