Projet de conception de PCB pour module ADC double

Les ADC dans un PCB sont examinés dans ce projet, y compris le placement et le routage impliquant un ADC isolé.

Cliquez ici pour accéder à l'intégration du visualiseur et parcourir ce projet

Si votre carte inclut un CAN (Convertisseur Analogique-Numérique), alors votre carte se qualifie comme un système à signaux mixtes et nécessitera certaines pratiques de disposition particulières pour éviter un excès de bruit sur les lignes analogiques. Les CAN sont normalement des composants non isolés, mais ils existent également en variété isolée, où le composant fournit une isolation galvanique entre les côtés analogique et numérique.

Dans ce projet, je vais montrer un exemple de conception qui utilise les deux types de CAN dans la même disposition de PCB. Ces composants nécessitent des pratiques de disposition différentes, mais nous les mettrons en œuvre sur la même carte pour fournir une bonne comparaison.

Comme c'est le cas dans tous nos projets, il y a un lien pour télécharger les fichiers sources de ce projet à la fin de l'article. Pour en savoir plus sur l'utilisation de ces types de composants et pour suivre l'ensemble du processus de disposition, vous pouvez regarder la playlist ci-dessous.

Démarrage du module CAN

Le module CAN que je présenterai dans ce projet est destiné à collecter deux signaux et à transmettre les données à un connecteur à broches, qui pourrait ensuite se connecter à une carte externe comme un module de microcontrôleur. Le module inclura l'ensemble suivant de composants principaux :

- ISL75051ASEHVFE - Module régulateur de puissance rad-hard de 5V à 3V3

- ADC128S102CIMTX - ADC 12 bits de 8 canaux, de 0,5 à 1 MSps

- AMC1203BPSA - ADC de mesure de courant isolé sigma-delta 8 bits à canal unique de 40 kSps

Les signaux à collecter sont destinés à être à basses fréquences, comme en témoignent leurs faibles taux d'échantillonnage. Les deux ADC supposent des sources à faible impédance, donc nous n'avons pas besoin d'un filtre actif avec un tampon d'impédance, et nous pouvons nous connecter directement aux entrées ADC si désiré. Enfin, toute personne familière avec les composants d'Intersil notera que l'ISL75051ASEHVFE est un régulateur rad-hard ; ce module pourrait être utilisé dans un système spatial tant que les deux autres composants peuvent être qualifiés pour l'aérospatiale.

Schémas des ADC isolés et non isolés

Les images ci-dessous montrent les deux principales parties des schémas pour ce module : les ADC isolés et non isolés. Les autres composants et circuits peuvent être consultés dans les fichiers du projet.

Les schémas sont simples ; nous avons besoin d'une seule page pour tous les circuits. Nous avons deux entrées d'alimentation séparées, une pour le côté isolé passant par un SMA, et une autre pour le côté non isolé passant par le connecteur à broches.

Tout d'abord, examinez les schémas pour l'ADC isolé (AMC1203BPSA) comme montré ci-dessous.

La référence analogique pour ce composant est définie en interne, donc nous n'avons pas besoin d'une puce de référence de précision pour définir la plage de mesure. Notez que l'ADC isolé nécessite deux réseaux d'alimentation différents (+5V et +5V_AN), tous deux à +5V selon la fiche technique ; ces derniers doivent provenir de sources différentes afin de garantir que l'isolation galvanique est maintenue à travers l'espace d'isolation de ce composant. J1 et J3 sont les connecteurs pour le signal analogique entrant et l'alimentation d'entrée pour le côté analogique de l'ADC.

Pour protéger correctement les signaux entrants, les signaux arrivant aux ADCs isolé et non isolé sont fournis en utilisant un câble coaxial avec des connecteurs SMA verticaux (73251-1350 de Molex). Ces connecteurs et les câbles coaxiaux attachés auront une impédance de 50 Ohms, mais les signaux d'entrée seront suffisamment faibles pour que la seule interaction appréciable existe entre la source et la charge dans le système.

Ensuite, examinez le circuit pour l'ADC standard.

Dans ce circuit, l'alimentation est fournie par le régulateur (réseau 3V3), qui à son tour reçoit son alimentation de la connexion +5V du connecteur à broches. La sortie SPI utilise une résistance pour ralentir légèrement le taux de montée avant de router le signal hors de la carte. Des condensateurs sont également placés spécifiquement pour le découplage/contournement des broches VA et VD.

Il y a certaines hypothèses dans les schémas ci-dessus :

- Le réseau +5V_AN n'aura jamais besoin de beaucoup de courant sur cette carte, donc utiliser un câble SMA + coaxial pour l'alimentation est approprié. Des tensions/courants plus élevés nécessiteraient des composants différents.

- La bande passante du signal d'entrée est uniquement limitée par le taux d'échantillonnage de chaque ADC. Si une bande passante inférieure est nécessaire, ajoutez un filtre passe-bas RC et fonctionnez à la vitesse d'échantillonnage maximale pour l'anti-aliasing.

- La connexion +5V sur le connecteur à broches est supposée être régulée et relativement exempte de bruit. Si non régulée, un régulateur +5V sera nécessaire à l'entrée.

- Les broches VA et VD sur U2 ne sont pas isolées car U2 est le seul composant générant des bords numériques rapides pour son interface SPI. S'il y avait plus de composants sur le bus 3V3, alors nous voudrions certainement envisager de limiter la bande passante de l'alimentation à la broche VA près de 1 MHz.

Avec ces points écartés, nous pouvons passer à l'empilement. Notre empilement devra supporter 2 interfaces numériques raisonnablement rapides (une pour chaque ADC) et deux lignes d'alimentation séparées vers les ADCs.

Planification de l'espace et empilement PCB

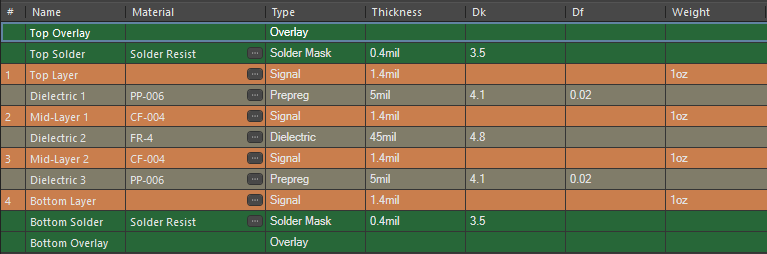

Comme cette carte contient un composant isolé, elle doit avoir un plan d'implantation particulier qui permet une région isolée. Nous pouvons tout faire sur cette carte sur une seule couche, mais nous avons besoin de la terre pour éviter le couplage inductif entre les sections analogiques et numériques, ce qui exige un plan de masse interne. Par conséquent, nous pouvons utiliser un empilement PCB simple à 4 couches avec GND interne.

L'empilement finalisé est montré ci-dessous. Dans cet empilement, nous avons utilisé un empilement SIG+PWR/GND/GND/SIG ; les composants seront sur le côté supérieur et le côté inférieur peut être utilisé pour un routage supplémentaire selon les besoins.

Dans cet empilement, la valeur Dk n'est pas si importante car nous n'avons pas de besoins en impédance contrôlée. Le point important ici est la couche externe mince, ainsi que GND sur L2 et L3. La couche externe mince avec la terre adjacente est clé pour supprimer le bruit, comme je l'ai souligné dans un autre article sur l'extraction parasitaire.

Ensuite, la section isolée doit être placée dans sa propre zone avec ses connecteurs SMA fournissant alimentation et signal. J'ai isolé ceci dans le côté gauche de la carte, tandis que les composants restants seront situés sur le côté droit. Le placement initial est montré ci-dessous.

Le placement initial aligne toutes les sections analogiques sur le côté gauche de la carte, tandis que le régulateur et les lignes d'E/S sont dirigés directement vers la droite (principalement sur la couche arrière). C'est une stratégie typique pour minimiser le couplage de bruit entre les lignes numériques et les lignes d'alimentation analogiques. La barrière d'isolation court verticalement sous U3, c'est donc là que nous allons séparer les réseaux de masse en GND et AGND pour maintenir l'isolation requise.

Pour réaliser cette séparation, j'ai mis en œuvre une petite région de coulée de cuivre qui s'étend à travers les 4 couches dans le PCB. La région fournit des connexions AGND sur J1 et J3, et les couches seront connectées avec des vias de brochage.

Les connexions thermiques sur les pads SMA seront supprimées en modifiant les règles de conception. J'utilise une stratégie similaire dans la section non isolée, mais avec la différence que la coulée sur L2 passe sous toute la connexion ADC. J'ajouterai également des vias de liaison à cette section pour la suppression du bruit. Avec ce point complété, nous pouvons maintenant router le reste des connexions.

Un point que je voudrais souligner ici concerne le placement des condensateurs. Comme c'est le cas pour un composant numérique, il est important de placer tous les condensateurs qui alimentent la broche d'alimentation analogique près de ces broches. De cette manière, le sous-système analogique pourra tirer suffisamment de puissance pendant son intervalle d'échantillonnage et il y aura un minimum de chute pour toute référence interne. Un exemple est montré ci-dessous. Spécifiquement, nous avons placé C18 et C19 pour l'alimentation numérique, et C16 et C17 pour le côté analogique.

Itinéraire et agencement finalisés

Après quelques déplacements de composants, j'ai réussi à déplacer les gros condensateurs (C9 et C13) de manière à ce qu'ils se trouvent plus au centre de la carte. Cela me permet de réduire quelque peu la taille de la carte afin de ne pas avoir une grande zone ouverte sans composants ni routage. Ensuite, sur L2 et L3, j'ai mis à la terre partout pour maintenir la distribution du cuivre dans l'empilement principalement symétrique. Le routage finalisé, avec les vias de liaison inclus, est montré ci-dessous.

Dans cette vue, vous pouvez voir l'entrée +5V et la sortie +3V3 routées comme de grands polygones, tandis que les autres polygones sur la couche supérieure sont GND ou AGND. Tous les signaux numériques sont routés sur la couche inférieure, sauf aux points où ils doivent se connecter aux ADCs sur L1.

Une vue 3D de la disposition finale du PCB est montrée dans l'image ci-dessous. Comme d'habitude, nous avons quelques logos, ainsi qu'une légende de sérigraphie pour le brochage sur l'en-tête à broches. Les SMA placés sur le côté gauche ont des vias de liaison pour relier cette région de terre sur toutes les couches et pour empêcher l'interférence RF errante de se propager dans cette partie du substrat. Ces lignes ne sont également pas conçues pour une impédance spécifique, et l'hypothèse ici est que les signaux d'entrée seront de fréquences si basses que les lignes de transmission sont électriquement courtes.

Que pouvons-nous ajouter de plus à ce module ?

Le design tel qu'il est présenté ci-dessus est destiné à s'interfacer avec un module microcontrôleur externe pour collecter et traiter les données via le connecteur à broches. Pour continuer le développement de cette carte, on pourrait placer une section numérique avec un microcontrôleur sur la couche arrière, où le microcontrôleur accepte les données fournies par les sorties des CAN. Un petit microcontrôleur comme le PIC (de Microchip) ou un STM32 plus petit (ST Microelectronics) serait approprié pour ce module.

Le design, tel qu'il est actuellement, suppose une faible impédance de source et aucun filtrage pour limiter la bande passante du signal collecté par l'appareil. Cela est déjà limité par le taux d'échantillonnage basé sur le taux d'échantillonnage de Nyquist, mais les signaux de basse fréquence pourraient être suréchantillonnés et passés à travers un filtre anti-repliement RC pour réduire davantage le bruit.

Si vous utilisez un microcontrôleur sur la couche arrière, il aura probablement une interface de sortie pour envoyer des données à un autre appareil, tel qu'un ordinateur. Cela pourrait être fait via une interface UART, ou directement via USB. L'option UART est utile car elle pourrait ensuite être routée vers un connecteur à 2 broches, qui serait alors connecté à l'appareil de destination. Comme tant de microcontrôleurs disposent d'une option UART, le prochain projet que je présenterai sera un module convertisseur UART vers USB qui pourrait accepter des données d'un microcontrôleur comme je l'ai décrit ici.

Suivez ce lien pour télécharger une archive ZIP avec les fichiers sources du projet. Vous pouvez également utiliser le lien de téléchargement dans l'encart ci-dessus pour accéder aux fichiers sources.

Les composants de haute densité avec sections RF sont faciles à placer et à router avec l'ensemble complet d'utilitaires CAO dans Altium Designer®. Lorsque vous avez terminé votre conception, et que vous souhaitez remettre les fichiers à votre fabricant, la plateforme Altium 365™ facilite la collaboration et le partage de vos projets.

Nous n'avons fait qu'effleurer les possibilités offertes par Altium Designer sur Altium 365. Lancez votre essai gratuit d'Altium Designer + Altium 365 dès aujourd'hui.