Projeto de Placa de Circuito Impresso com Módulo ADC Duplo

Neste projeto, são examinados os ADCs em uma PCB, incluindo o posicionamento e o roteamento envolvendo um ADC isolado.

Clique aqui para acessar o visualizador embutido e navegar por este projeto

Se a sua placa inclui um ADC, então ela se qualifica como um sistema de sinal misto e precisará de algumas práticas de layout específicas para evitar ruído excessivo nas linhas analógicas. ADCs normalmente não são componentes isolados, mas também existem em variedade isolada, onde o componente fornece isolamento galvânico entre os lados analógico e digital.

Neste projeto, vou mostrar um exemplo de design que usa ambos os tipos de ADCs no mesmo layout de PCB. Esses componentes requerem práticas de layout diferentes, mas vamos implementá-los na mesma placa para fornecer uma boa comparação.

Como é o caso em todos os nossos projetos, há um link para baixar os arquivos fonte deste projeto no final do artigo. Para aprender mais sobre o uso desses tipos de componentes e acompanhar todo o processo de layout, você pode assistir à playlist abaixo.

Iniciando o Módulo ADC

O módulo ADC que apresentarei neste projeto é destinado a coletar dois sinais e passar os dados para um cabeçalho de pinos, que poderia então se conectar a uma placa externa como um módulo de microcontrolador. O módulo incluirá o seguinte conjunto de componentes principais:

- ISL75051ASEHVFE - Módulo regulador de energia rad-hard de 5V para 3V3

- ADC128S102CIMTX - ADC de 12 bits e 8 canais, de 0,5 a 1 MSps

- AMC1203BPSA - ADC de corrente isolada sigma-delta de 8 bits e 40 kSps de canal único

Os sinais que estão sendo coletados destinam-se a ser de baixas frequências, conforme evidenciado por suas baixas taxas de amostragem. Ambos os ADCs assumem fontes de baixa impedância, portanto, não precisamos de um filtro ativo com um buffer de impedância, e podemos conectar diretamente aos entradas do ADC se desejado. Finalmente, qualquer pessoa familiarizada com os componentes da Intersil notará que o ISL75051ASEHVFE é um regulador rad-hard; este módulo poderia ser usado em um sistema espacial desde que os outros dois componentes possam ser qualificados para aeroespacial.

Esquemas de ADCs Isolados e Não Isolados

As imagens abaixo mostram as duas principais partes dos esquemas para este módulo: os ADCs isolados e não isolados. Os demais componentes e circuitos podem ser vistos nos arquivos do projeto.

Os esquemáticos são simples; precisamos apenas de uma página para todos os circuitos. Temos duas entradas de energia separadas, uma para o lado isolado que vem através de um SMA, e outra para o lado não isolado que vem através do conector de pinos.

Primeiro, dê uma olhada nos esquemáticos para o ADC isolado (AMC1203BPSA) conforme mostrado abaixo.

A referência analógica para este componente é definida internamente, então não precisamos de um chip de referência de precisão para definir a faixa de medição. Note que o ADC isolado requer duas redes de energia diferentes (+5V e +5V_AN), ambas a +5V baseadas na ficha técnica; estas devem vir de fontes diferentes para garantir que a isolação galvânica seja mantida através do espaço de isolamento neste componente. J1 e J3 são os conectores para o sinal analógico de entrada e a energia de entrada para o lado analógico do ADC.

Para proteger adequadamente os sinais de entrada, os sinais que vêm para os ADCs isolado e não isolado são fornecidos usando cabo coaxial com conectores SMA verticais (73251-1350 da Molex). Esses conectores e os cabos coaxiais anexados terão impedância de 50 Ohms, mas os sinais de entrada serão baixos o suficiente que a única interação apreciável existe entre a fonte e a carga no sistema.

A seguir, dê uma olhada no circuito para o ADC padrão.

Neste circuito, a energia é fornecida pelo regulador (rede 3V3), que por sua vez recebe sua energia da conexão +5V do cabeçalho de pinos. A saída SPI usa um resistor para diminuir ligeiramente a taxa de borda antes de encaminhar o sinal para fora da placa. Capacitores também são colocados especificamente para desacoplamento/bypass dos pinos VA e VD.

Existem algumas suposições nos esquemáticos acima:

- A rede +5V_AN nunca precisará de alta corrente nesta placa, portanto, usar um cabo SMA + coaxial para energia é apropriado. Tensões/correntes mais altas exigirão componentes diferentes.

- A largura de banda do sinal de entrada é limitada apenas pela taxa de amostragem de cada ADC. Se uma largura de banda menor for necessária, adicione um filtro RC passa-baixa e opere na taxa de amostragem máxima para anti-aliasing.

- A conexão +5V no cabeçalho de pinos é assumida como regulada e relativamente livre de ruídos. Se não regulada, um regulador de +5V será necessário na entrada.

- Os pinos VA e VD no U2 não são isolados porque o U2 é o único componente que puxa bordas digitais rápidas para sua interface SPI. Se houvesse mais componentes no barramento 3V3, então definitivamente consideraríamos limitar a banda de energia para o pino VA próximo a 1 MHz.

Com esses pontos esclarecidos, podemos prosseguir para o empilhamento. Nosso empilhamento precisará suportar 2 interfaces digitais razoavelmente rápidas (uma para cada ADC) e duas linhas de alimentação separadas para os ADCs.

Planejamento de Layout e Empilhamento de PCB

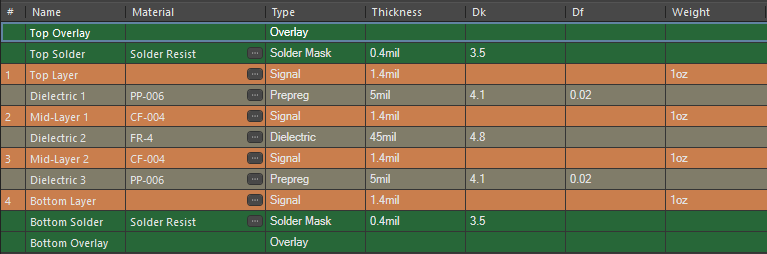

Como esta placa contém um componente isolado, ela precisa ter um plano de layout específico que permita uma região isolada. Podemos fazer tudo nesta placa em uma única camada, mas precisamos de terra para evitar o acoplamento indutivo entre as seções analógica e digital, o que exige um plano de terra interno. Portanto, podemos usar um empilhamento de PCB simples de 4 camadas com GND interno.

O empilhamento finalizado é mostrado abaixo. Neste empilhamento, usamos um empilhamento SIG+PWR/GND/GND/SIG; os componentes estarão no lado superior e o lado inferior pode ser usado para roteamento adicional conforme necessário.

Neste empilhamento, o valor de Dk não é tão importante, pois não temos requisitos de impedância controlada. O ponto importante aqui é a camada externa fina, bem como GND em L2 e L3. A camada externa fina com terra adjacente é chave para suprimir ruídos, como eu apontei em um artigo diferente sobre extração parasitária.

Em seguida, a seção isolada precisa ser colocada em sua própria área com seus conectores SMA fornecendo energia e sinal. Eu isolei isso no lado esquerdo da placa, enquanto os componentes restantes ficarão no lado direito. A colocação inicial é mostrada abaixo.

A colocação inicial alinha todas as seções analógicas no lado esquerdo da placa, enquanto o regulador e as linhas de E/S são roteadas diretamente para o lado direito (principalmente na camada de trás). Esta é uma estratégia típica para minimizar o acoplamento de ruído entre as linhas digitais e as linhas de alimentação analógicas. A barreira de isolamento corre verticalmente sob U3, então é aí que dividiremos as redes de terra em GND e AGND para manter o isolamento necessário.

Para fazer essa divisão, implementei uma pequena região de pour de cobre que se estende por todas as 4 camadas na PCB. A região fornece conexões AGND em J1 e J3, e as camadas serão conectadas com vias de costura.

As conexões térmicas nos pads SMA serão removidas ao alterar as regras de design. Eu uso uma estratégia semelhante na seção não isolada, mas com a diferença de que o preenchimento no L2 corre sob toda a conexão do ADC. Também adicionarei vias de costura a essa seção para supressão de ruído. Com este ponto concluído, podemos agora rotear o restante das conexões.

Um ponto que gostaria de destacar aqui é a colocação dos capacitores. Assim como acontece com um componente digital, é importante colocar quaisquer capacitores que fornecem energia ao pino de alimentação analógico perto desses pinos. Desta forma, o subsistema analógico poderá obter energia suficiente dentro do seu intervalo de amostragem e haverá uma queda mínima para qualquer referência interna. Um exemplo é mostrado abaixo. Especificamente, colocamos C18 e C19 para a alimentação digital, e C16 e C17 para o lado analógico.

Roteamento e Layout Finalizados

Após alguns ajustes nos componentes, consegui mover os grandes capacitores (C9 e C13) para que ficassem mais ao centro da placa. Isso me permite reduzir um pouco o tamanho da placa, de modo que não tenhamos uma grande área aberta sem componentes ou roteamento. Então, em L2 e L3, executei aterramento em todo lugar para manter a distribuição de cobre na pilha de camadas principalmente simétrica. O roteamento finalizado, com vias de costura incluídas, é mostrado abaixo.

Nesta visão, você pode ver a entrada de +5V e a saída de +3V3 roteadas como grandes polígonos, enquanto os outros polígonos na camada superior são GND ou AGND. Todos os sinais digitais são roteados na camada inferior, exceto nos pontos em que precisam se conectar aos ADCs em L1.

Uma visão 3D do layout finalizado da PCB é mostrada na imagem abaixo. Como de costume, temos alguns logotipos, bem como uma legenda em silkscreen para o pinout no cabeçalho de pinos. Os SMAs colocados no lado esquerdo têm vias de costura para unir essa região de terra em todas as camadas e para evitar que a interferência RF dispersa se propague para essa parte do substrato. Essas linhas também não são projetadas para uma impedância específica, e a suposição aqui é que os sinais de entrada serão de frequências tão baixas que as linhas de alimentação são eletricamente curtas.

O Que Mais Podemos Adicionar a Este Módulo?

O design, conforme mostrado acima, destina-se a interagir com um módulo de microcontrolador externo para coletar e processar os dados via conector de pinos. Para continuar desenvolvendo esta placa, poderia-se colocar uma seção digital com um microcontrolador na camada traseira, onde o microcontrolador aceita dados fornecidos pelas saídas dos ADCs. Um microcontrolador pequeno como o PIC (da Microchip) ou um STM32 menor (ST Microelectronics) seria apropriado para este módulo.

O design, como está agora, pressupõe uma impedância de fonte baixa e sem filtragem para limitar a largura de banda do sinal sendo coletado pelo dispositivo. Isso já é limitado pela taxa de amostragem baseada na taxa de amostragem de Nyquist, mas sinais de baixa frequência poderiam ser superamostrados e passados por um filtro anti-aliasing RC para reduzir ainda mais o ruído.

Se você usar um microcontrolador na camada traseira, provavelmente terá uma interface de saída para enviar dados a outro dispositivo, como um computador. Isso pode ser feito através de uma interface UART ou diretamente via USB. A opção UART é útil, pois então poderia ser direcionada para um cabeçalho de 2 pinos, que seria conectado ao dispositivo de destino. Como muitos microcontroladores têm uma opção UART, o próximo projeto que apresentarei será um módulo conversor de UART para USB que poderia aceitar dados de um microcontrolador como descrevi aqui.

Siga este link para baixar um arquivo ZIP com os arquivos fonte do projeto. Você também pode usar o link de download no embed acima para acessar os arquivos fonte.

Componentes de alta densidade com seções RF são fáceis de colocar e rotear com o conjunto completo de utilitários CAD em Altium Designer®. Quando você terminar seu design e quiser liberar os arquivos para seu fabricante, a plataforma Altium 365™ facilita a colaboração e o compartilhamento de seus projetos.

Apenas começamos a explorar o que é possível com o Altium Designer no Altium 365. Inicie seu teste gratuito do Altium Designer + Altium 365 hoje.