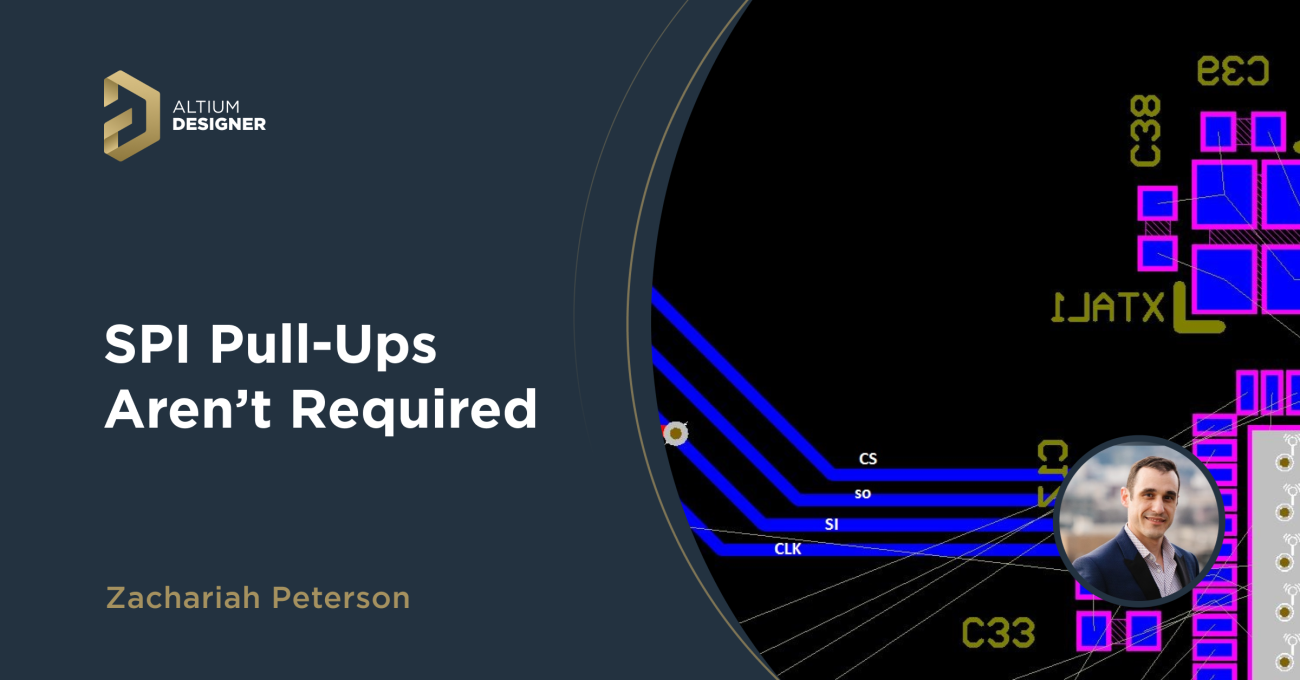

Vous n'avez pas toujours besoin de résistances de tirage sur les lignes SPI

Les résistances de tirage (pull-up) ne sont pas nécessaires sur les lignes SPI. Il existe certaines situations où elles peuvent être utilisées sans affecter la fonctionnalité du tampon push-pull.

Il existe une idée fausse populaire selon laquelle les résistances de tirage (pull-up resistors) sont requises ou nécessaires sur les lignes d'un bus SPI. Je suis ici pour vous dire de manière catégorique que les résistances de tirage ne sont pas requises sur un bus SPI pour réaliser sa fonction de base de transmission et réception de données numériques.

Le tampon dans une interface SPI possède une topologie push-pull qui (à un niveau élevé) implique des MOSFETs de commutation côté haut et côté bas, formant essentiellement un inverseur CMOS. Comme nous le verrons dans cet article, la présence de résistances de tirage n'a aucun impact sur la fonctionnalité d'un bus push-pull.

Cela dit, il existe des cas où il est judicieux de placer une résistance de tirage sur un bus push-pull, et dans certaines fiches techniques, un fabricant de composants le recommandera ou l'exigera. Nous examinerons ces situations et comment cela affecte le comportement de votre système. Bien qu'il puisse exister des solutions plus élaborées qui éliminent le besoin de résistances de tirage dans ces situations, le placement d'une résistance de tirage peut être une solution qui garde votre conception simple et offre une assurance que l'interface fonctionnera correctement.

Comment un bus SPI fonctionne avec des résistances de tirage

Jetons un coup d'œil au modèle typique d'un tampon dans une interface SPI. Tous les tampons SPI possèdent une topologie push-pull qui consiste en une commutation côté haut et côté bas qui transmet un signal sur le bus, et chaque signal dans le bus SPI (CS, MOSI, MISO et SCLK) aura cette topologie. Un exemple de ce circuit est montré ci-dessous. Notez qu'un vrai tampon SPI n'est pas aussi simple que deux MOSFETs, mais l'idée générale reste la même.

Un inverseur CMOS comme pilote SPI. La sortie se connecte à une trace (représentée comme des éléments groupés) et un circuit de charge (modèle équivalent RC).

La raison entière d'utiliser cette topologie est pour que les capacitances de décharge dans le circuit de tampon fournissent des taux de transition raisonnablement rapides sur la sortie, qui seront bien plus courts que la période d'horloge sur le bus. C'est ce qui permet d'atteindre des taux de données plus rapides qu'avec un protocole à drain ouvert (par exemple, I2C).

Un bus SPI qui inclut des résistances de tirage est essentiellement un pilote d'inverseur CMOS avec une résistance en parallèle avec le FET côté haute tension dans le tampon de sortie. Voyons maintenant ce qui se passe pendant chaque état de commutation dans le pilote et nous pouvons voir ce qui se passe sur le bus.

Sortie logique HAUTE

Pendant l'état de sortie logique HAUTE, le NMOS est ÉTEINT et le PMOS est ALLUMÉ. VDDIO fournit maintenant du courant dans la piste connectée et la charge. La capacité dans la piste et la charge commence alors à se charger jusqu'à ce que la tension vue à la charge corresponde à VDDIO. Ici, la résistance à l'état passant du PMOS est de l'ordre du mOhm, tandis que la résistance de tirage est de l'ordre de 1 à 10 kOhms. De toute évidence, la résistance de tirage est si grande qu'elle est essentiellement court-circuitée par le PMOS dans l'état de sortie logique HAUTE.

Parce que tout le courant passe à travers le PMOS dans l'état logique HAUT indépendamment de la présence de la résistance de tirage, les caractéristiques de commutation seront inchangées.

Sortie logique BASSE

Considérons maintenant que le circuit est passé à l'état de sortie logique BAS. Dans cet état, le NMOS est activé et le PMOS est désactivé, donc la trace et la capacité de charge se déchargent à travers le NMOS dans le réseau GND. Comme le PMOS est éteint, il apparaît comme une résistance très élevée (ordre des MOhms) qui est bien plus grande que la valeur de la résistance de tirage (1 à 10 kOhms).

Comme la résistance de tirage est la plus petite résistance dans ce cas, elle permettra un courant de VDDIO/R(pu) à s'écouler vers le NMOS. Pour une résistance de tirage de 1 à 10 kOhm et VDDIO = 3.3 V, le courant de fuite dans le NMOS serait de 0.33 à 3.3 mA. Cela est bien inférieur au courant SPI typique de ~50 mA, donc encore une fois, nous ne remarquerons aucun effet sur les caractéristiques de commutation. Le temps de descente sur le bus sera limité par les capacités de charge et de trace, l'impédance résistive de sortie du circuit tampon, et la résistance à l'état passant du NMOS.

Si la Commutation n'est pas Affectée, Pourquoi Utiliser une Résistance de Tirage ?

Il est clair que le placement d'une résistance de tirage (pull-up) sur une ligne SPI n'affecte pas sa capacité à transmettre un signal sur le bus. Par conséquent, la résistance de tirage doit remplir une autre fonction qui n'est pas liée à la transmission de données, sinon la résistance ne serait pas utilisée.

Les raisons d'utiliser une résistance de tirage sur une ou plusieurs lignes dans une interface SPI varient selon la situation proposée. Certaines situations où les résistances de tirage sont utilisées incluent :

- Placement sur la ligne CS pour un périphérique

- Placement sur la ligne MISO pour un dispositif hôte

- Placement sur la ligne MOSI pour un périphérique

- Placement sur toutes les lignes du bus près des broches de sortie

La raison invoquée pour le placement dans l'une de ces situations est de définir l'état logique sur l'un des composants périphériques du bus. La recommandation la plus courante est de placer une résistance de tirage sur la broche CS d'un périphérique afin de la tirer vers le haut. Si le périphérique possède une broche d'activation active à l'état bas, cela tirera toujours la broche vers le haut à moins que le côté conducteur de la traction ne mette la broche à l'état bas.

Un exemple d'une telle utilisation est montré ci-dessous. Dans l'agencement du PCB, la résistance de tirage serait placée près de la broche CS de ce périphérique.

Placement typique d'une résistance de tirage sur la broche CS d'un bus SPI.

Pourquoi cela serait-il utilisé ? La raison évoquée est que pendant le démarrage du système, la broche CS pourrait flotter dans n'importe quel état et cela créerait un risque que le bruit puisse corrompre les données sur le bus. De plus, si le dispositif hôte démarre avant le périphérique et que la broche CS devient activée involontairement, l'hôte pourrait commencer à manipuler les données dans le périphérique. Cela est parfois cité comme une raison de placer une résistance de tirage sur les périphériques de mémoire.

À ce jour, je ne trouve pas de raison convaincante de placer une résistance de tirage sur la ligne SCLK (horloge). La raison est que le circuit logique récepteur ne basculera pas si d'autres conditions (spécifiquement l'état de la ligne CS) ne sont pas remplies, indépendamment de la présence d'un signal d'horloge. Certains app notes et fiches techniques recommandent les résistances de tirage MISO ou MOSI pour diverses raisons, mais tester si cela fonctionne est simple et la résistance peut toujours être dessoudée lors du travail sur votre prototype.

La séquence d'alimentation est une solution plus élaborée

Étant donné que cela est le plus souvent cité comme un problème avec l'état de la broche CS lors du démarrage du système, je pense que la séquence d'alimentation entre les périphériques et l'hôte du système serait la meilleure approche pour prévenir ce problème lors du démarrage. Dans les systèmes plus petits, il se peut qu'il n'y ait pas d'espace disponible dans l'appareil pour plusieurs régulateurs ou pour un séquenceur d'alimentation capable de transmettre la puissance requise. C'est une solution plus simple que de placer une résistance de tirage, mais comprenez que ces résistances de tirage ne sont pas nécessaires pour que l'interface fonctionne correctement.

Que vous ayez besoin de construire des électroniques de puissance fiables ou des systèmes numériques avancés, utilisez l'ensemble complet de fonctionnalités de conception de PCB et d'outils CAO de classe mondiale dans Altium Designer®. Pour mettre en œuvre la collaboration dans l'environnement interdisciplinaire d'aujourd'hui, les entreprises innovantes utilisent la plateforme Altium 365™ pour partager facilement les données de conception et lancer les projets en fabrication.

Nous n'avons fait qu'effleurer la surface de ce qui est possible avec Altium Designer sur Altium 365. Commencez votre essai gratuit d'Altium Designer + Altium 365 dès aujourd'hui.