Roteamento Controlado por Impedância para Placas Feitas no Altium Designer

Os requisitos de computação e aplicações exigem que os dados sejam processados a taxas mais rápidas do que nunca. À medida que as faixas de comunicação começam a se encher e novos componentes chegam ao mercado, as PCBs precisarão operar em taxas de dados e frequências mais altas. Aplicações de rede e de data center como Ethernet de 100G e mais rápido, bem como protocolos sem fio avançados como 5G e 6G, continuarão operando bem dentro do regime de ondas milimétricas e além.

Esses fatos significam que problemas de integridade de sinal como diafonia, EMI, oscilações e controle de impedância estão se tornando cada vez mais críticos em designs avançados de PCBs. As ferramentas de análise precisam ser capazes de identificar e fornecer alguma visão sobre como compensar problemas de integridade de sinal em PCBs durante a fase de design. Ninguém quer receber sua placa acabada de um fabricante, apenas para testá-la e descobrir que as taxas de erro de bit estão altíssimas. É aqui que as ferramentas de simulação se tornam críticas, permitindo que você encontre as fontes de problemas de integridade de sinal antes que seu produto chegue ao mercado.

O ambiente de design no Altium Designer® agora inclui um avançado resolvedor de campo 3D que se integra ao seu Gerenciador de Pilhas de Camadas para controle de impedância preciso, extração de parasitas e cálculos de atraso de propagação. Se você não está familiarizado com o uso de fórmulas de impedância em métodos de otimização avançados, você pode determinar a geometria da trilha de que precisa para controle de impedância com esta ferramenta de design integrada. Veja como isso funciona no fluxo de trabalho de design orientado por regras do Altium Designer e como fazer o melhor uso da utilidade do resolvedor de campo 3D integrado.

Cálculos de Impedância: Fórmulas vs. Resolvedores de Campo

Em designs avançados com sinais de banda larga, como canais de alta taxa de dados em laminados de baixa perda, a dispersão no dielétrico é uma fonte de dificuldade em designs de PCB de alta velocidade. Fórmulas de impedância para geometrias padrão podem fornecer um ótimo ponto de partida para determinar a largura da trilha de que você precisa para roteamento controlado por impedância. As equações mais precisas são derivadas com mapeamento conforme e requerem uma técnica numérica para extrair a largura da trilha para uma impedância dada.

O problema ao usar essas equações é que elas dificultam a determinação da largura de trilha ideal para o roteamento de sinais de banda larga. Você pode incluir a dispersão em uma equação de impedância, mas a largura de trilha que você extrair será então uma função da frequência, o que forma um problema de otimização complexo para determinar a melhor trilha para minimizar desvios da impedância alvo. Por essa razão, a maioria das ferramentas de design de PCB força você a escolher uma frequência representativa para calcular a largura da trilha (geralmente a frequência de Nyquist). Essas outras ferramentas de design e calculadoras online podem não incluir tangente de perda, perdas por efeito pelicular e capacitância de carga ao calcular a impedância.

Some a isso outros problemas que ocorrem ao projetar linhas de transmissão para sinais de alta velocidade, como a aspereza do cobre. Um método melhor para determinar a largura de trilha perfeita que corresponde a uma impedância alvo é usar um solucionador de campo integrado que inclui dispersão de banda larga, aspereza do cobre e perdas por efeito pelicular. Seu roteador interativo então colocará trilhas com a largura apropriada de modo que suas trilhas terão o valor de impedância definido de que você precisa.

Configurando Cálculos de Impedância

O roteamento controlado por impedância no Altium Designer utiliza um solucionador de campo integrado da Simberian. Isso começa após a conclusão dos seus esquemáticos, mas antes de você montar o layout da sua placa. Você vai querer configurar esse recurso ao projetar o empilhamento da sua PCB. Após criar um arquivo PcbDoc em branco, você pode ir ao menu “Design” e clicar em “Gerenciador de Empilhamento de Camadas”. Depois de terminar de criar seu empilhamento, você pode começar a executar cálculos de impedância para diferentes pares de camadas. Para obter o valor de impedância necessário para diferentes pares de camadas, você precisará clicar na aba de Impedância na parte inferior da janela do Gerenciador de Empilhamento de Camadas.

Criando Perfis de Impedância

A partir daqui, você pode criar perfis de impedância de extremidade única e impedância diferencial para diferentes pares de camadas no seu empilhamento. Um perfil de impedância permite que você defina uma impedância especificada, e a ferramenta retornará a largura do traço que ajusta a impedância para o valor desejado. Para sinais diferenciais, você pode criar um perfil diferencial e especificar o espaçamento entre pares diferenciais, e o perfilador de impedância retornará a largura do traço necessária. Você também pode ajustar o espaçamento para o valor que deseja, e o perfilador de impedância ajustará a largura do traço em resposta.

Usando a ferramenta de perfilador de impedância para uma PCB de 10 camadas no Altium Designer.

Impedância Combinada de Modo Comum e Diferencial

Sob padrões de sinalização diferencial de alta velocidade, você frequentemente precisará definir a impedância diferencial para um valor específico enquanto também ajusta a impedância de modo comum de cada traço no par para seu próprio valor (Ethernet é um exemplo). Para fazer isso, você pode criar dois perfis de impedância para os sinais relevantes; um perfil de modo comum e outro diferencial. Isso procede através do seguinte processo:

- Crie um perfil de impedância de modo comum para determinar a largura necessária para o controle de impedância em redes de modo comum.

- Crie um perfil de impedância diferencial e defina os valores de impedância e tolerância desejados.

- Copie a largura determinada do perfil de modo comum para o perfil diferencial na mesma camada.

- Ajuste manualmente o espaçamento até que a impedância diferencial atinja o valor desejado.

A imagem abaixo mostra este tipo de controle de impedância, onde a impedância diferencial e de modo comum para o perfil diferencial são correspondidas a 85 Ohms e 50 Ohms, respectivamente.

Definindo perfis de roteamento controlados por impedância de modo comum e diferencial no Altium Designer.

Agora que os perfis de impedância relevantes foram definidos, é hora de habilitá-los como regras de design para roteamento de impedância controlada.

Usando Regras de Design para Controle de Impedância

Redes de Terminação Única

As regras de design que você definir a seguir especificarão a largura necessária para manter a impedância requerida. Para começar a configurar suas regras de design, abra o "Editor de Regras e Restrições do PCB". Clique no menu "Design" e depois clique na opção "Regras". Se você olhar para a lista no lado esquerdo do editor, verá uma entrada para "Roteamento". Clique em Roteamento -> Opção de Largura. Na imagem abaixo, o perfil de impedância de terminação única está ativado (o perfil nomeado S50), o que forçará o roteador a colocar trilhas com a largura definida no seu perfil de impedância.

Configurando o roteamento controlado por impedância no Altium Designer.

Há dois pontos importantes neste diálogo. Primeiro, você pode escolher aplicar o controle de impedância a trilhas em camadas de sinal específicas ou com redes de sinal específicas. Aqui, isso foi aplicado a "NetR_BIAS_1", que é uma rede de terminação única (selecionada perto do topo do diálogo). Segundo, você também pode aplicar o perfil de impedância como uma regra de design geral para todas as redes em todas as camadas, selecionando a opção "Todas as Redes". Você também pode aplicar esta opção a uma Classe de Rede, que automaticamente aplicará a regra a múltiplas redes em uma única classe.

Observe que, na tabela na parte inferior do diálogo, você pode ver quais camadas estão habilitadas no perfil de impedância. Aqui, a regra só se aplicará ao TopLayer e BottomLayer durante o roteamento. Para habilitar outras camadas de sinal, volte ao Gerenciador de Pilha de Camadas e abra a aba de Impedância. A partir daqui, você pode habilitar outras camadas onde deseja impor esta regra de design.

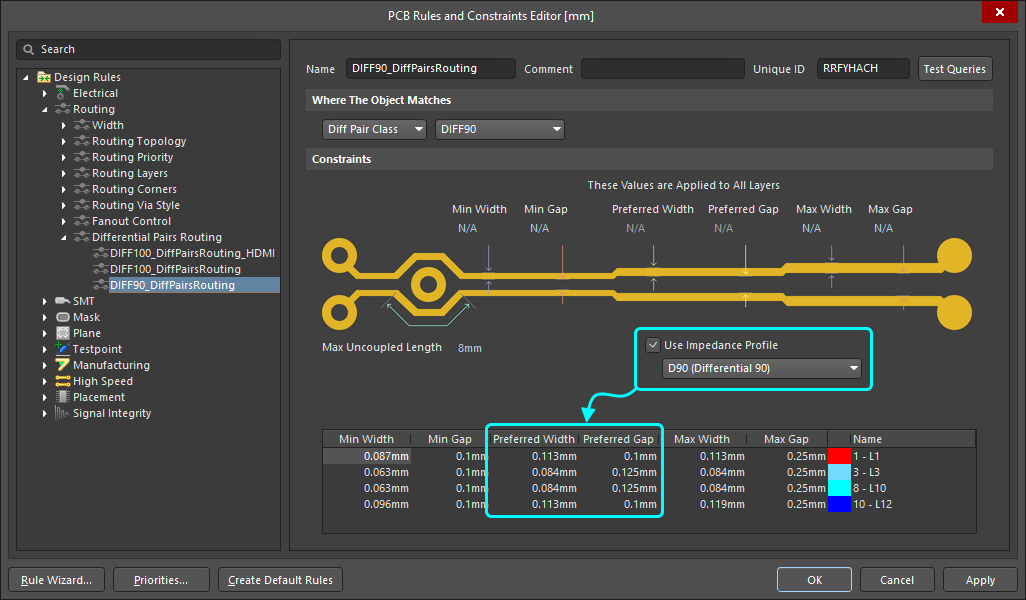

Pares Diferenciais

Para aplicar o perfil de impedância diferencial, vá para a opção Roteamento -> Roteamento de Pares Diferenciais no editor de Regras e Restrições do PCB. Daqui, você pode habilitar o perfil de impedância diferencial que configurou no gerenciador de pilha de camadas. Neste caso, quando você estiver usando o roteador interativo para pares diferenciais, o roteador irá impor a largura de traço e o espaçamento requeridos que você definiu no perfil de impedância.

Uma imagem do Editor de Regras e Restrições do PCB é mostrada abaixo, onde um perfil de impedância diferencial foi aplicado para definir a impedância de todos os pares em uma Classe de Par Diferencial para 90 Ohms.

Assim como a regra pode ser aplicada em redes de terminação única específicas ou Classes de Net, o roteamento controlado por impedância diferencial pode ser aplicado em pares diferenciais específicos ou Classes de Par Diferencial, conforme mostrado acima. Você pode selecionar as redes ou classes específicas onde esta regra será aplicada no topo do diálogo de Regras e Restrições do PCB. Você também pode habilitar camadas específicas onde a regra de controle de impedância diferencial será aplicada, assim como foi feito para redes de terminação única.

Chegou a Hora de Começar a Roteamento

Agora que a pilha de camadas está concluída e o controle de impedância está habilitado através de suas regras de design, você pode começar o roteamento no layout do PCB. Quando você estiver usando o roteador interativo, notará que “[Largura De: Regra Preferencial]” aparece na barra de status na parte inferior da tela enquanto você roteia. Suas trilhas aparecerão em sua placa com largura pré-definida (e espaçamento definido para pares diferenciais).

O controle de impedância define automaticamente a largura da sua trilha enquanto você roteia

Ao utilizar as ferramentas de roteamento em redes controladas por impedância (tanto de terminação única quanto diferencial), a ferramenta de roteamento priorizará automaticamente a largura que você definir nas regras de design. Não é necessário ajustar manualmente a largura. No entanto, se você deseja aplicar uma largura diferente, existem várias opções, como definir restrições de prioridade alternativas por camada ou definir restrições baseadas em salas para redes específicas. Isso permitiria alterar a restrição de largura em diferentes regiões da PCB, que seriam aplicadas automaticamente pelo roteador interativo.

Finalmente, o roteamento controlado por impedância em sua PCB não é preciso a menos que você execute simulações de integridade de sinal para determinar a largura apropriada para suas trilhas. Alguns desses aspectos podem ser examinados no Altium Designer, enquanto outros requerem uma aplicação de software externo. Algumas das métricas importantes de integridade de sinal que você pode considerar são:

- Forma de onda de reflexão TDR

- Forma de onda de resposta de um único bit

- Parâmetros-S (S11 e S21)

- Diagramas de olho para taxas de dados seriais altas

- Conversão de modo (para pares diferenciais)

No Altium Designer, é possível examinar grandes desajustes de impedância na extremidade de recepção de uma interconexão ao observar a forma de onda de reflexão. Esta seria a forma de onda de resposta de um único bit mencionada acima. Isso permite a identificação de ressonância e potencial para ultrapassar os limites de alta/baixa tensão para o estado lógico ALTO. Fazer isso corretamente requer a descrição precisa da interface para seus pinos de sinal, o que requer conhecimento da família lógica do pino ou o uso de um modelo IBIS. Alguns fabricantes disponibilizam modelos IBIS para download e uso em analisadores de integridade de sinal no domínio do tempo, como o recurso Análise de Integridade de Sinal no Altium Designer.

O motor de design baseado em regras no Altium Designer facilita a implementação de um esquema de roteamento controlado por impedância. Se você tem um design existente que apresenta problemas de integridade de sinal, o simulador de integridade de sinal pode iterar através de possíveis esquemas de terminação e mostrar os resultados, permitindo que você selecione o esquema correto para terminar suas trilhas.

Fale hoje mesmo com um especialista da Altium para saber mais sobre as ferramentas de roteamento e integridade de sinal no Altium Designer.