Cách Thiết kế Bố cục PCB Hỗn hợp

Nếu bạn cần các vật liệu dựa trên PTFE thay thế hoặc vật liệu vải thủy tinh có Dk thấp, hãy xem xét việc sử dụng cấu trúc PCB hỗn hợp. Bạn sẽ có chi phí thấp hơn và lợi thế của vật liệu ít tổn hao trên một lớp.

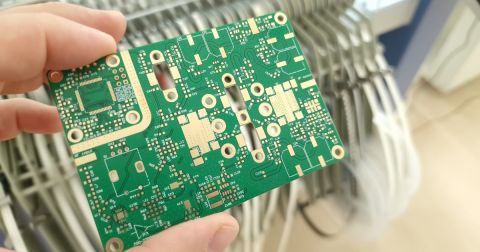

Mô-đun đánh giá radar từ Texas Instruments được hiển thị ở trên là một ví dụ về thiết kế chứa một phần mmWave hoàn chỉnh với định tuyến RF và truyền dẫn công suất cao, cũng như một phần kỹ thuật số tốc độ vừa phải với nhiều IC. Tôi không liên kết với TI, nhưng lý do chính tôi thích bo mạch này như một công cụ giáo dục là nó cho thấy một cách sử dụng các loại laminate dựa trên PTFE như Rogers hoặc Taconic để xây dựng một sản phẩm RF thương mại. Đôi khi, khi chúng ta nói về việc sử dụng laminate PTFE hoặc các lựa chọn thay thế như laminate vải thủy tinh Dk thấp, chúng ta không nói về việc xây dựng toàn bộ cấu trúc từ vật liệu PTFE đắt tiền với bondplies.

Trong một số trường hợp, việc xây dựng một bo mạch hoàn toàn từ laminate PTFE hoặc laminate Dk thấp là có ý nghĩa. Tôi đã làm điều này với các backplane tốc độ cao hỗ trợ hàng chục kết nối dài trên nhiều lớp với băng thông cắt tại ~80 GHz. Khi bạn cần định tuyến các kênh nối tiếp đa gig giữa hai kết nối qua 15 inch không gian bo mạch, bạn cần giảm thiểu tổn thất càng thấp càng tốt để đảm bảo tín hiệu tại bộ thu có thể được phục hồi. Tuy nhiên, trong các trường hợp khác, bạn thực sự chỉ cần một laminate tổn thất thấp trên một lớp. Đây chính là bản chất của một cấu trúc bo mạch hybrid, và nó có thể là lựa chọn tốt hơn cho bo mạch của bạn.

Khi nào nên sử dụng cấu trúc PCB hỗn hợp

Câu hỏi đầu tiên cần được đặt ra khi lựa chọn vật liệu và lên kế hoạch cho cấu trúc là: cần những vật liệu nào và nên sử dụng bao nhiêu lớp? Giả sử bạn đã xác định bạn cần một loại laminate ít tổn hao và bạn đã xác định số lượng lớp cần thiết, đã đến lúc cân nhắc liệu bạn có nên sử dụng cấu trúc hỗn hợp hay không. Có một số tình huống rộng lớn mà bạn có thể xem xét sử dụng cấu trúc hỗn hợp với laminate ít tổn hao trong PCB của mình:

- Tiết kiệm chi phí: Sử dụng toàn bộ PTFE hoặc toàn bộ vật liệu có Dk thấp có thể tốn kém. Đối với nguyên mẫu, sự chênh lệch chi phí không lớn, nhưng những chênh lệch chi phí này sẽ tăng lên ở khối lượng cao.

- Số lượng kết nối RF thấp: Nếu bạn có thể sắp xếp tất cả các tín hiệu tốc độ cao/RF trên một lớp, không có lý do gì để xây dựng toàn bộ cấu trúc từ các lớp phủ chuyên biệt có tổn hao thấp. Bạn có thể xem xét việc tăng kích thước bảng mạch để giảm số lượng via và sắp xếp tất cả trên lớp tổn hao thấp.

- Thiết kế sóng mm: Một số hệ thống RF hoạt động trong băng tần ISM hoặc WiFi 6-7 GHz sẽ hoạt động tốt trên các lớp phủ cấp FR4 miễn là các kết nối ngắn. Khi bạn chuyển sang tần số radar ô tô hoặc cao hơn, bạn sẽ cần các lớp phủ tổn hao thấp trừ khi các kết nối của bạn rất ngắn đến mức không thực tế.

Hình ảnh dưới đây cho thấy một cấu trúc hybrid 6 lớp tôi đã trình bày trong bài viết trước. Cấu trúc này là một ví dụ tốt cho các mô-đun radar hoặc các ứng dụng chuyên biệt khác của tín hiệu sóng mm như hình ảnh.

Lớp xếp chồng trên cũng phù hợp cho các hệ thống số với băng thông mở rộng sâu vào vùng mmWave, mặc dù cần chú ý đến sự phân tán trong lớp laminate ít mất mát. Các nhà sản xuất vật liệu RF cố gắng xây dựng hệ thống laminate của họ với sự phân tán phẳng ra đến các tần số GHz cao. Tuy nhiên, trên một giới hạn tần số cao nào đó, sự phân tán sẽ xảy ra trở lại để tạo ra nhiều mất mát và méo pha trong tín hiệu số. Nếu bạn đang hoạt động ở các tần số cực cao trên giới hạn không phân tán, hãy chắc chắn liên hệ với nhà cung cấp laminate để lấy dữ liệu hằng số điện môi để bạn có thể thực hiện các tính toán trở kháng và S-parameter chính xác.

Ngoài ra, một số nhà sản xuất có thể nói với bạn rằng lớp xếp chồng này không thể được sản xuất vì bạn đã đặt PWR và SIG cạnh nhau trong hai lớp nội bộ. Nếu bo mạch nhỏ, điều đó sẽ không quan trọng; bo mạch này sẽ không trải nghiệm bất kỳ sự cong vênh nào cho đến khi kích thước của nó đạt đến kích thước backplane nhiều U. Bạn cũng có thể cân bằng lớp nội bộ bằng cách đổ đồng nếu cần.

Nói chuyện với Nhà sản xuất của Bạn Sớm

Nếu bạn đã lên kế hoạch cho một cấu trúc lớp hỗn hợp dựa trên yêu cầu về độ mất mát, độ dày của bảng mạch và số lượng lớp, bạn nên gửi cấu trúc lớp của mình cho nhà sản xuất trước khi bắt đầu thiết kế. Điều này rất quan trọng vì nhà sản xuất có thể xác định xem bảng mạch có thể vượt qua quá trình ép nhiệt mà không bị phân hủy hoặc bong lớp không, vì một số vật liệu cần nhiệt độ và áp suất cao hơn so với những vật liệu khác. Đừng ngần ngại liên hệ với nhà sản xuất sớm để nhận lời khuyên về việc sử dụng laminate giảm mất mát mong muốn của bạn trong một cấu trúc lớp hỗn hợp. Hãy chắc chắn cung cấp cho họ:

- Số lượng lớp cần thiết

- Độ dày lớp mong muốn

- Vật liệu laminate giảm mất mát

- Vật liệu laminate lấp đầy

Hãy cố gắng quyết định xem yêu cầu nào là bắt buộc và yêu cầu nào chỉ là mong muốn, vì bạn có thể cần phải thỏa hiệp về một số yêu cầu của mình.

Cho phép không gian cho Bondply

Nhà sản xuất của bạn có thể cung cấp cho bạn một số hiểu biết về sự biến đổi độ dày mà bạn có thể mong đợi thấy trên bảng mạch hoàn thiện sau khi lớp bondply được thêm vào. Hãy chắc chắn xem xét điều này khi lên kế hoạch cho stackup. Bạn nói chung không cần phải lo lắng về hằng số điện môi của lớp bondply trừ khi bạn cần phải định tuyến qua nó. Nếu bạn đã thiết kế với một lớp laminate giảm tổn thất ở lớp trên cùng, bondply có thể cần phải đặt giữa L2 và L3 để vật liệu giảm tổn thất dính vào các lớp laminate cấp FR4. Nhà sản xuất của bạn có thể cung cấp cho bạn thêm thông tin về điểm này.

Nộp một Stackup Sơ bộ

Ngay cả sau khi bạn tạo một bố cục xếp chồng sơ bộ, bạn nên gửi nó cho nhà sản xuất của mình để họ có thể kiểm tra trước khi tiến hành sản xuất. Đôi khi, bạn không thể tự do chọn bất kỳ hệ thống vật liệu nào và laminate giảm tổn hao mà bạn muốn sử dụng trong bố cục xếp chồng hỗn hợp. Nhà sản xuất của bạn sẽ có tiếng nói trong việc chọn lựa vật liệu nào có sẵn, có thời gian chì ngắn, hoặc nếu họ sẽ phải thuê ngoài sản xuất. Nếu bạn có thể nhận được sự đánh giá bố cục xếp chồng trước khi bạn tạo phần còn lại của thiết kế, nhà sản xuất của bạn có thể đề xuất một hệ thống vật liệu thay thế phù hợp với quy trình lamin hóa PCB yêu cầu. Họ cũng có thể đề xuất một số độ dày laminate thay thế có thể giúp bạn đạt được yêu cầu độ dày tổng thể của bảng mạch.

Đọc Bảng Dữ Liệu Vật Liệu

Nếu bạn đang chọn vật liệu cho một bố cục xếp chồng hỗn hợp và bạn muốn đóng một vai trò tích cực hơn trong việc xây dựng bố cục xếp chồng hỗn hợp, hãy xem xét các bảng dữ liệu của vật liệu trước khi bạn tạo một bố cục đề xuất. Hãy cố gắng khớp giá trị CTE, giá trị Tg, nhiệt độ chảy nhựa, và nhiệt độ chữa để đảm bảo tính tương thích đầy đủ. Bạn vẫn nên gửi bố cục xếp chồng để đánh giá đảm bảo khả năng sản xuất.

Khi bạn cần tạo một bố cục PCB hỗn hợp, các công cụ thiết kế PCB trong Altium Designer® bao gồm mọi thứ bạn cần để xác định cấu trúc bố cục của mình, tính toán trở kháng, và nhập thông tin bố cục vào bản vẽ chế tạo. Tiện ích Draftsman giúp bạn nhanh chóng tạo bản vẽ chế tạo và lắp ráp với bố cục PCB hỗn hợp của mình và xuất chúng dưới dạng PDF. Khi bạn đã hoàn thành thiết kế và muốn gửi các tệp cho nhà sản xuất của mình, nền tảng Altium 365™ làm cho việc hợp tác và chia sẻ dự án của bạn trở nên dễ dàng.

Chúng ta mới chỉ khám phá bề mặt của những gì có thể thực hiện với Altium Designer trên Altium 365. Bắt đầu dùng thử miễn phí Altium Designer + Altium 365 ngay hôm nay.