您需要了解的所有关于阻抗的信息

术语阻抗在许多不同的上下文中被使用,如传输线、扬声器和基本电气元件。在学校,我们都学过使用电学的一般物理知识来理解电感的阻抗。然而,如果工程师没有在PCB或电气元件中处理过实际的阻抗问题,其实际含义可能不清楚。如果不理解阻抗的起源,并且听说它在许多不同的上下文中被使用,很容易感到困惑。在这篇文章中,我将介绍阻抗的基础知识。

Z = U/I

基本上,阻抗并不复杂。无论阻抗这个术语在哪个上下文中使用,其含义都是完全相同的:它是电压和电流之间的关系。它与电阻的不同之处在于具有频率依赖性,而电阻在所有频率下都是恒定的。如果你的信号是纯正弦波,对于电感的阻抗,你感兴趣的是在正弦信号频率下的阻抗。如果你的信号阻抗是数字的,你感兴趣的是了解从直流到信号的最高频率的阻抗。在分析阻抗和电压除以电流的计算时,你需要考虑频率。阻抗是在特定频率下的电压除以电流。由于电压和电流之间的关系,阻抗的单位是欧姆。

反应元件

基本的电气反应元件是电容和电感。我不使用术语电容器和电感器,因为这些与实际的物理组件有关,而现在我们只考虑理想现象。这两种理想的“组件”具有依赖于频率的阻抗。这意味着在恒定电压下,通过组件的电流随频率的变化而变化,因为电感的阻抗随频率变化。例如,一个理想的电容器具有如图1所示的典型阻抗。在低频时阻抗高,但频率升高时阻抗变小。如果我们想要在低频和高频下通过电容的电流保持相同,我们需要在信号在低频操作时增加更高的电压,在信号频率较高时减小电压。

图1. 理想电容器阻抗。横轴和纵轴都是对数

电感的行为恰恰相反。它的阻抗在低频时较低,并随着频率的增高而增加,如图2所示。这两个反应元件决定了所有电路和组件的阻抗。电感器的阻抗总是电容和电感的结果。

图2. 理想电感器阻抗

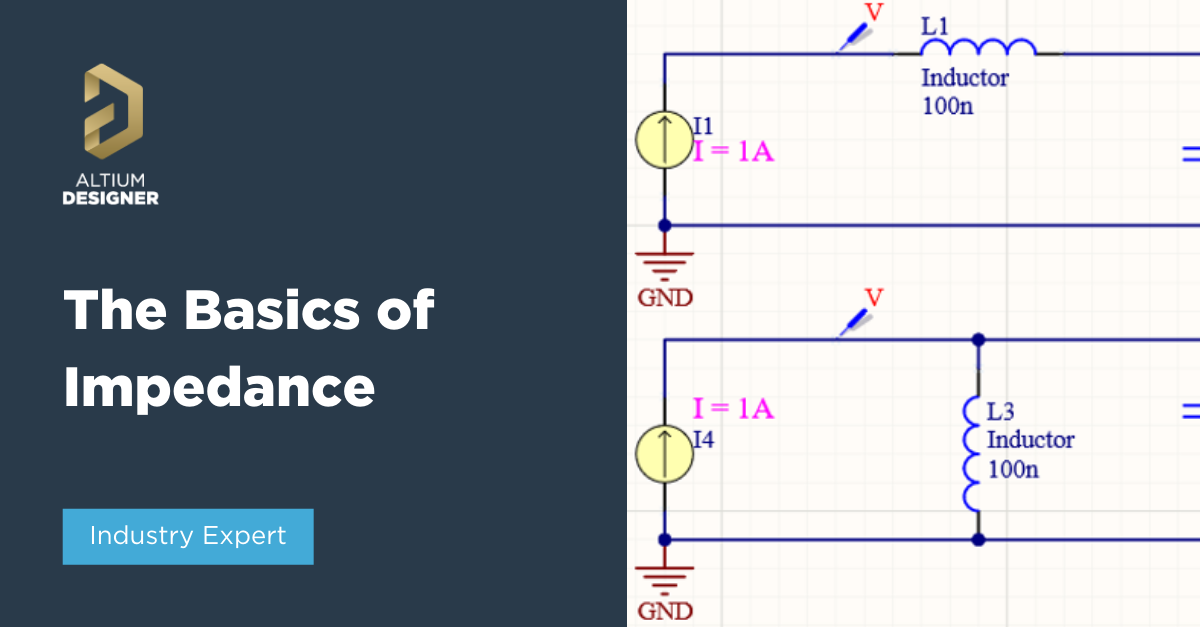

(R)CL 电路

实际上,所有实际的阻抗都是不同电感和电容串联或并联组合的结果。这两个组件共同创建的阻抗取决于电容和电感是并联还是串联连接,如图3所示。

图3. 并联(绿色)和串联(红色)连接的电容和电感的阻抗。

当电容和电感串联时,在低频和高频下阻抗都很高,最小点位于这些频率之间的某处。在并联的情况下,我们看到在低频和高频下阻抗都很低,但在中间变高。在LC电路中,阻抗的减小来自系统电容,阻抗的增加来自系统电感。低阻抗和高阻抗峰值都是电容和电感共同产生的共振频率。在共振频率处,阻抗达到极小值或极大值,共振频率取决于电容和电感,根据下面的方程式。

Fresonance = 12πLC

在图3中,电容为1nF,电感为100nH,这给出了一个15.9MHz的共振频率。

如果CL电路包含电阻,电阻对所有频率都是恒定的,它设定了共振频率处的最小阻抗水平。例如,假设我们在100nH电感和1nF电容串联中加入理想的10Ω电阻。在这种情况下,我们得到一个类似的阻抗曲线,但最小阻抗水平为10Ω,如图4中的仿真结果所示。请注意,在现实生活中,我们很少看到像图4中绿色图表所示的阻抗,因为电阻元件有它们的寄生效应,为高频提供了一个较低的阻抗路径。尽管如此,在实践中,现实生活中的所有阻抗都是由电容、电感和电阻的串联或并联组成的。

图4. 并联(绿色)和串联(蓝色)连接的RCL电路的阻抗。

真实元件

每个元件都有电容、电感和电阻。我们可以通过并联和串联连接的电感和电容来模拟每个电气元件的等效电路。在许多情况下,电路也包含电阻元素,例如,由于电容器的ESR。图5是一个SMD电阻等效电路的例子。

图 5. 真实电阻的等效电路。 图片来源 www.vishay.com

一个简单的电阻器因为元件端子具有电感,且电阻元件具有并联电容,所以具有反应组件。因此,电阻器的阻抗不是恒定的,如图 6所示,高频时更加依赖频率。电阻器的电阻元件是恒定的,但寄生元件导致其阻抗依赖频率。因为元件的寄生电容和电感取决于物理参数,如元件的端子,物理尺寸对元件的阻抗有重大影响。元件的物理尺寸越大,其寄生电容和电感就越显著,这直接影响系统阻抗。同样的原理适用于所有电气元件,等效电路取决于特定的元件。

图 6. 真实电阻的阻抗。 图片来源 www.vishay.com

真实走线

每次我们在PCB上设计走线时,我们都在设计电感和电容。由于电流环路,走线总是具有电感,由于走线与其参考平面的物理分离,走线具有电容。再次,值得注意的是,走线的尺寸和其相对于参考平面的几何形状决定了电容和电感,从而决定了走线的阻抗。设计走线阻抗需要设计走线尺寸和3D中的电路布局。这就是为什么一些布局比其他布局效果更好的原因,即使它们的功能相同:布局几何形状不同。

以几条不同的PCB走线的仿真为例。在这块PCB上,我们有三条直走线。其中两条走线下没有参考平面,它们的长度分别是走线1,35mm,和走线2,120mm。第三条走线下面有一个实心参考平面,其长度与走线2相同,为120mm。根据Altium Designer的堆叠工具的阻抗计算器,走线3的阻抗为50Ω。走线及其堆叠在图7中展示。走线的仿真是使用CST进行的,首先,我通过为每条走线添加端口来模拟每条走线的s参数。然后我用50Ω源驱动这些走线,而走线的末端由50Ω电阻终止。

图7. 模拟的走线和PCB堆叠。尺寸单位为毫米。

在图8中,您可以看到没有实心参考平面下的走线的仿真结果。我们看到当频率增加时,阻抗开始增加,我们也看到是走线的长度决定了阻抗开始增加的频率。这类走线具有相对较大的电感和低电容,这导致了此种阻抗行为。

图 8. 两条无参考平面轨迹的电磁阻抗仿真

在我们的第二个仿真示例中,我们比较了两条120mm的轨迹,但一条有参考平面,另一条则没有。从图 9 的仿真结果中,我们可以看到参考平面的影响;它使得阻抗保持恒定。由于附近的导电参考平面,电容增加,但由于回流电流在轨迹下方流动,使得电流环路物理上变小,因此电感降低。添加参考平面将我们的轨迹变成了传输线。

图 9. 120mm迹线带有和不带参考平面的电磁模拟

传输线

在传输线中,阻抗可能是最为人所知的。如图 9 所示,特性阻抗是恒定的,并且理想情况下不会随频率变化。传输线是利用迹线的电感和电容的智能发明,其结果是在宽带宽中阻抗恒定。通过迹线宽度与其下方参考平面的距离的适当几何关系,实现恒定的电感器阻抗。这允许使用具有宽带宽的信号,如高速数字信号。如果没有传输线,我们必须保持在低频率上。

传输线也是电感和电容的结果。传输线可以被建模为分布式电感器 - 电容器对,其中电感器串联,电容器连接到地面,如图 10 所示。

图 10. 传输线等效电路。

这些分布式LC对形成了串联和并联连接的谐振电路,其阻抗最小值和最大值不断变化。特征电感阻抗然后是电感与电容之比的平方根。通过改变走线的宽度或调整走线与参考平面之间的距离,可以调整阻抗水平。这意味着我们改变了单个电容或电感元件。同样,走线与参考平面之间的介电材料以同样的方式影响电容,就像它影响真实电容器的电容一样。如果您正在设计传输线,Altium 在层堆栈管理工具中直接提供阻抗模拟。有了这个,您可以快速检查设计的传输线的阻抗,无需进行电磁模拟。

结论:阻抗来源于几何形状和材料属性

阻抗是电子设计中的一个重要参数,因为它决定了组件或互连如何修改信号阻抗。电感器阻抗源于电气元件的物理尺寸、其到电流返回路径的距离,以及所用材料的电气特性。所有这些都为电气元件贡献了寄生电容和电感,并导致元件的电压-电流比率变得频率依赖。

想了解更多关于Altium Designer®如何帮助您进行下一个PCB设计的信息吗?与Altium的专家交谈。

Back

Back