Automatisiertes PCB-Routing mit dem Situs Topological Autorouter

Diese Seite betrachtet den Situs Topological Autorouter. Dieser Teil des PCB-Editors verwendet topologisches Mapping, um den PCB-Verlaufspfad zu definieren und diesen in eine hochwertige Route umzuwandeln.

Es gibt ein Werkzeug in einer PCB-Designanwendung, das die Leute lieben zu hassen: Autorouter. Ich habe Autorouter in einigen meiner ersten Entwürfe verwendet, die viele Leiterbahnen hatten. Diese ersten paar Platinen hatten keine Anforderungen, die die Routingfreiheit einschränken würden, wie kontrollierte Impedanz oder Verlustbudgets. Ich hätte diese frühen Platinen wahrscheinlich (und sollte) von Hand routen sollen, nur um mehr Erfahrung im PCB-Layout zu sammeln, aber ich habe trotzdem einen Autorouter verwendet.

Obwohl viele Autorouter der aktuellen Generation in gewissem Maße jede dieser Anforderungen erfüllen, stellen die rasterbasierten, formbasierten oder geometrischen Ansätze, die sie bei der Kartierung des Routingraums verwenden, ernsthafte Einschränkungen bei dichteren, nicht-orthogonalen und geometrisch unregelmäßigen Komponentenverpackungstechnologien dar - Technologien, die in modernem Platinendesign immer häufiger werden. Autorouter der aktuellen Generation produzieren aufgrund ihrer geometrischen Einschränkungen auch Ergebnisse, die "autoroutet aussehen", was zu umfangreicher manueller Nacharbeit führt. Tatsächlich meiden viele Designer die Verwendung von Autoroutern allein wegen dieser Einschränkung.

Der Situs™ Autorouter von Altium Designer ist ein Werkzeug, das zur automatischen Verlegung spezifischer Netze oder Netzklassen verwendet werden kann und könnte ein nützliches Werkzeug für Ihren Entwurfsprozess sein. Es ist wichtig zu beachten, dass dieser Autorouter ein fortgeschrittenes Automatisierungswerkzeug ist, das helfen kann, eine Menge manueller Verlegung zu eliminieren, aber es ist wichtig zu wissen, wann und wo er eingesetzt werden sollte.

Der Situs Autorouter ist kein Point-and-Click-Werkzeug. Er erfordert Planung und Konfiguration.

Um dieses Werkzeug optimal zu nutzen, bedarf es einiger Planung und Überlegung im PCB-Layout, dem Einrichten von Netzklassen, so dass spezifische Netzgruppen mit dem Autorouter gezielt werden können, und sogar dem Entwerfen einer benutzerdefinierten Verlegestrategie, die mit dem Situs Autorouter implementiert wird.In diesem Artikel werden wir einige Hintergründe zum Autorouting untersuchen, wie man den Situs Autorouter konfiguriert und ein Beispiel zeigen, das die Ergebnisse eines Autorouters wie Situs zeigt. Nutzen Sie die Links im Inhaltsverzeichnis oben, um zu jedem Abschnitt in diesem Leitfaden zu springen.

Übersicht über den Situs Autorouter

Traditionelle Ansätze zum Autorouting

Ein elektronisches Design ist im Wesentlichen eine Sammlung von Komponenten, deren Pins auf eine bestimmte Weise miteinander verbunden sind. Das Design wird umgesetzt, indem die Komponenten auf einer mehrschichtigen mechanischen Struktur, einer sogenannten Leiterplatte (PCB), angeordnet werden. Die Verbindungen werden physisch durch diskrete Kupferpfade realisiert, die über und durch die PCB verlaufen, von einem Komponentenpin zum anderen.

Die Aufgabe, den diskreten Kupferpfad oder die Route für jede Verbindung zu erstellen, kann sehr komplex sein. Ein typisches Design könnte viele Tausend Verbindungen zwischen den Pins der Komponenten haben, und die Pfade müssen möglicherweise zwischen Komponenten erstellt werden, die sehr dicht auf der PCB-Oberfläche gepackt sind.

Frühe Autorouter kartierten einen Designraum, indem sie ein festes, regelmäßiges Gitter über das gesamte Board definierten, mit dem Ziel, jeden Komponentenpin direkt auf einem Gitterpunkt liegen zu haben und genügend Gitterpunkte im freien Raum zu haben, um alle Verbindungen zu routen. Frühe Komponenten wurden mit ihren Pins in Vielfachen von 0,1 Zoll Abstand geliefert, sodass die Definition eines geeigneten Gitters relativ einfach war, wie unten gezeigt.

Als alle Komponenten Pins im 0,1"-Raster hatten, konnte ein Gitterrouter verwendet werden.

Mit der Einführung von oberflächenmontierten Bauteilen wurde der Abstand zwischen den Anschlussstiften der Komponenten deutlich kleiner, und die Hersteller begannen auch, Komponenten mit metrischem Stiftabstand anzubieten. Verbesserungen in der Fertigungstechnologie ermöglichten es dem Designer, sehr schmale Routingpfade zu verwenden, die enger zusammengelegt werden konnten. Diese Faktoren zusammen machten traditionelle einheitliche Gitter-Router für Designs, die diese Verpackungs- und Fertigungstechnologien verwendeten, unbrauchbar. Da das Gitter fein genug sein musste, um effektiv mit den neuen Technologien umgehen zu können, benötigten gitterbasierte Router enorme Mengen an Speicher und Rechenleistung - ganz zu schweigen von der Zeit - um das Routinggitter zu erstellen und das Design zu routen.

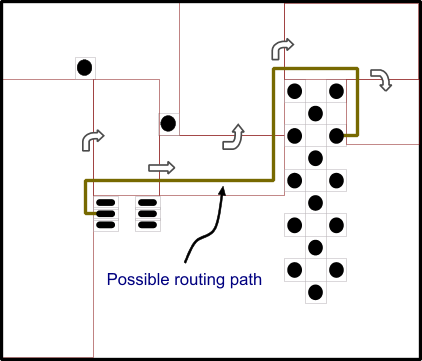

Um diesen Ansatz zu verbessern, wurde eine Technik namens rektilineare Expansion [1] entwickelt. Diese Technik definiert den Raum zwischen Hindernissen auf der Platine als eine Reihe von Rechtecken. Sobald der Satz von Rechtecken definiert wurde, wird ein Routingpfad bestimmt, indem den Kanten der Rechtecke gefolgt wird. Diese Technik ermöglichte es, Komponenten mit unterschiedlichem Stiftabstand zu routen, und sie ermöglichte es dem Autorouter auch, mit den damals neueren Fertigungstechnologien wie oberflächenmontierten Komponenten umzugehen. Dieser Ansatz wird oft als formbasiertes Autorouting bezeichnet, weil er die Routingkanäle mithilfe von rechteckigen Formen modelliert, wie im Bild unten gezeigt.

Ein rektlinearer Router teilt den Raum in rechteckige Zonen auf, die dann verwendet werden, um einen Routenpfad zu finden.

Obwohl rektlineare Expansions-Autorouter einige der Geschwindigkeits- und Speicherprobleme von uniformen Gitter-Routern überwinden können, sind sie dennoch geometrisch in den möglichen Routenpfaden, die sie identifizieren können, eingeschränkt. Sobald die rechteckige Karte für eine Platine erstellt ist, expandieren die Routing-"Wellenfronten" entlang der Kanten der angrenzenden Rechtecke - nur in vertikaler und horizontaler Richtung. Das Routing ist orthogonal zu den Grenzen der Rechtecke eingeschränkt. Probleme können bei nicht-orthogonalen Geometrien auftreten, wie sie beispielsweise bei gestaffelten Pin-Grid-Array-Komponenten oder rotierten Komponenten zu finden sind. Oft kann in diesen Fällen kein orthogonaler Routenpfad gefunden werden, und rektlineare Expansions-Router werden scheitern.

Die Verpackung von Komponenten wird weiterhin kleiner in Größe und Pin-Abstand, und neuere Pakete wie Ball Grid Arrays (BGAs) verwenden gestaffelte Gitter, um die Dichte ihrer Pins zu maximieren. In Kombination damit erfordern kleine und ungewöhnliche Produktverpackungen oft, dass Komponenten in unregelmäßigen Orientierungen und auf ungewöhnlich geformten PCBs platziert werden. Da diese Trends an Fahrt gewinnen, wird es für rektlineare Expansions-Router immer schwieriger werden, den Routing-Herausforderungen des modernen Platinendesigns gerecht zu werden.

Was benötigt wurde, war eine neue Technik zur Kartierung des Routing-Raums, die das Board nicht als einfache Rechtecke modelliert und nicht auf rechtwinklige Pfade zwischen den Hindernissen beschränkt ist.

- [1] Ein Verfahren zum rasterlosen Routing von gedruckten Schaltkarten, 22nd Design Automation Conference, Paper 32.2 1984, A.C. Finch, K.J. Mackenzie, G.J. Balsdon, G Symonds von Racal Redac Ltd.

Der topologische Ansatz

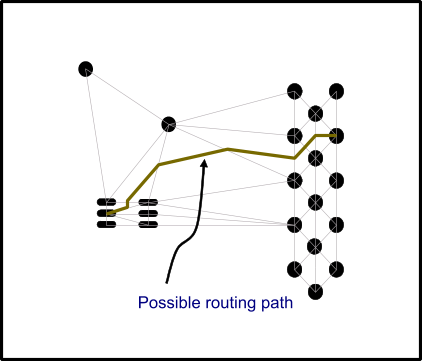

Ein topologischer Ansatz zum Autorouting, wie er vom Situs-Autorouter von Altium Designer verwendet wird, nutzt eine andere Methode zur Kartierung des Routing-Raums - eine, die geometrisch nicht eingeschränkt ist. Anstatt Arbeitsbereichskoordinateninformationen als Bezugspunkt zu verwenden, erstellt ein topologischer Autorouter eine Karte, die nur die relativen Positionen der Hindernisse im Raum verwendet, ohne Bezug auf ihre Koordinaten.

Topologisches Mapping ist eine Technik der Raum-Analyse, die den Raum zwischen benachbarten Hindernissen trianguliert. Diese triangulierte Karte wird dann von den Routing-Algorithmen verwendet, um zwischen den Hindernispaaren "hindurchzuweben", vom Startpunkt der Route bis zum Endpunkt der Route. Die größten Stärken dieses Ansatzes sind, dass die Karte formunabhängig ist (die Hindernisse und Routing-Pfade können jede Form haben) und der Raum kann unter jedem Winkel durchquert werden - die Routing-Algorithmen sind nicht ausschließlich auf rein vertikale oder horizontale Pfade beschränkt, wie bei einem rektangulären Expansionsroutern.

Um eine topologische Karte eines Boards zu erstellen, verknüpft Situs jedes Hindernis auf dem Board mit seinen benachbarten Hindernissen und schafft so etwas Ähnliches wie ein Netz verbundener Spinnweben. Potenzielle Routing-Pfade werden dann definiert, indem man von einem Spinnfaden zum nächsten und dann zum nächsten und so weiter schreitet, bis das Ziel erreicht ist. Dieser Ansatz zur Kartierung ist geometrisch nicht an den Routing-Raum gebunden; der potenzielle Pfad webt sich einfach seinen Weg zwischen jedem Paar von Hindernissen hindurch, wie im Bild unten gezeigt.

Die topologische Karte entfernt die grundlegende Einschränkung früherer Router - die Einschränkung, die durch die Verwendung desselben geometrischen Raums zur Kartierung von Pfaden entsteht, wie sie auch zum Routen verwendet wird. Indem der Kartierungsraum vom Routingraum getrennt wird, kann der topologische Router natürlichere Pfade kartieren und auch Routingpfade finden, die nicht orthogonal sind. Dieser Kartierungsprozess funktioniert sehr ähnlich wie bei Designern, in dem Sinne, dass Designer nach einem Pfad suchen, der die Platine auf direkteste Weise durchquert, während sie in gewissem Maße die Schichtrichtungen beibehalten, die sie zugewiesen haben. Designer beschränken ihre Entscheidungen nicht darauf, ob eine Verbindung durch einen bestimmten Bereich mit einer Reihe orthogonaler Spuren hergestellt werden kann, sondern entscheiden einfach, ob eine Spur durch einen möglichen Routingkanal passt oder nicht.

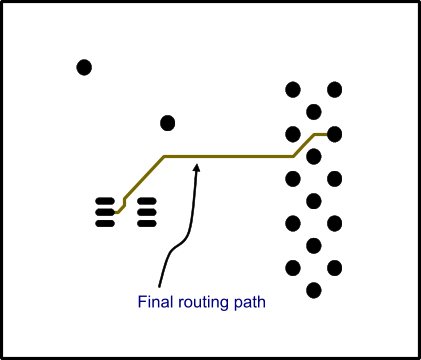

Wie durch den im Bild links dargestellten Pfad gezeigt, ist der anfänglich topologisch definierte Pfad möglicherweise nicht als fertiger Routenpfad geeignet. Durch ausgeklügelte Routing-Algorithmen wandelt Situs den kartierten Pfad in einen geeigneten Routingpfad um, ein Beispiel dafür ist im Bild rechts dargestellt.

Ein topologischer Router versucht nicht, in die Geometrie des Raums zu kartieren, er sucht einen Pfad zwischen den Hindernissen.

Die initiale topologische Analyse eines Leitungspfades, ohne Berücksichtigung der Koordinaten von Hindernissen, führt zu hohen Fertigstellungsquoten und hohen Geschwindigkeiten auf Platinen, die traditionell als schwierig für Autorouter betrachtet werden - zum Beispiel solche mit nichtstandardisierten Geometrien, dicht gestaffelten Pin-Komponenten oder unregelmäßig geformten Umrissen und Ausschnitten.

Finden eines Leitungspfades

Ein weiterer Vorteil des topologischen Ansatzes ist, dass die Analyse und Bestimmung von Routingpfaden viel mehr dem Vorgehen eines Designers beim manuellen Verlegen einer Platine ähnelt.

Zum Beispiel hat die Erfahrung gezeigt, dass es am effizientesten ist, alle Verbindungen, die eine Schicht teilen, in die gleiche Richtung zu verlegen, was zum Konzept der Routing-Schichtausrichtung führt. Bei einfachen Zwei-Schicht-Platinen wird dies erreicht, indem einer Schicht die horizontale und der anderen die vertikale Ausrichtung zugewiesen wird. Sowohl der Designer als auch der Autorouter können dann die Routen gemäß dieser Konvention platzieren.

Wie Fahrspuren auf einer Straße bringt dieser Ansatz Ordnung in die Verlegungsaufgabe und ermöglicht es dem Designer oder Autorouter, die Platine als eine Reihe von Kanälen zu betrachten, die dann auf geordnete Weise zugewiesen werden können. Sowohl bei traditionellen Gitter-Routern als auch bei rektilinear erweiternden Routern sind die Schichtrichtungen auf vertikal - Leiterbahnen, die von der Oberseite der Platine bis zum Boden verlaufen, und horizontal - Leiterbahnen, die quer über die Platine von einer Seite zur anderen verlaufen, beschränkt.

Mit zunehmender Dichte des Designs wird jedoch auch die Anzahl der Schichten, die benötigt werden, um die Platine zu verlegen, steigen. Sobald das Design mehr als zwei Schichten erfordert, kann es effizienter sein, nach Verlegewegen in anderen Richtungen als vertikal und horizontal zu suchen. Genau das würde ein Designer tun - den Fluss der Verbindungslinien untersuchen und, wenn es eine ausreichende Anzahl in einer bestimmten Ausrichtung gibt, sagen wir diagonal, eine Schicht in dieser Richtung zuweisen, dann diese Verbindungen auf dieser Schicht in dieser Richtung verlegen.

Weder der Router mit festem Raster noch der rektilinear expandierende Router können direkt in eine nicht-orthogonale Richtung abbilden; sie können den Raum nur horizontal/vertikal kartieren. Um ordentliche diagonale Routen zu erzeugen, müssen diese Arten von Autoroutern zunächst eine Route mit orthogonalen Spuren definieren und dann spezielle Nachbearbeitungsroutinen ausführen, um die rechtwinkligen Ecken in Diagonalen umzuwandeln.

Ein topologischer Router hingegen ist nicht durch orthogonale Geometrien eingeschränkt und kann diagonale Routen direkt identifizieren und der richtigen Schicht zuweisen. Dies führt nicht nur zu einem natürlicheren Autorouting, sondern produziert auch eine effizientere Verdrahtung und minimiert die Anzahl der in der fertigen Konstruktion benötigten Durchkontaktierungen (Vias).

Routing abschließen

Wie zuvor erwähnt, bietet die topologische Analyse eine effiziente Methode zur Bestimmung eines möglichen Verdrahtungspfades, aber dieser topologische Pfad muss in eine qualitativ hochwertige fertige Route übersetzt werden. Wie ein Designer wird auch der Autorouter auf eine Vielzahl von Situationen treffen, die auf unterschiedliche Weise behandelt werden müssen, wie das Auflösen des Verdrahtungspfades durch die Karte, das Folgen einer Grenze oder das Drücken gegen vorhandene Routenobjekte in dem Versuch, sie zu verschieben.

Um diesen verschiedenen Situationen gerecht zu werden, setzt Situs eine Reihe von Routing-Engines ein, darunter einen Speicherrouter, Muster-Router, einen Strom- und Masse-Router, einen Wellenfront-Router, formbasierte Push-und-Shove-Router sowie eine Anzahl von heuristischen Routern für spezifische Situationen, wie zum Beispiel BGA-Fanout. Diese Engines basieren auf ausgereiften und leistungsfähigen Routing-Algorithmen und wurden über viele Jahre hinweg entwickelt. In Situs nutzen diese Routing-Engines die intelligente Wegfindung des topologischen Mapping-Prozesses, um hochwertige fertige Verbindungen zu erzeugen.

Die Situs-Routing-Engines werden von einem ausgeklügelten Satz von Strategiedateien gesteuert, die als das "Gehirn" des Autorouters fungieren. Ein menschlicher Designer hat gegenüber einem Autorouter beim Routing einer Platine eine Reihe von Vorteilen. Der menschliche Geist kann planen, und währenddessen kann er eine große Anzahl von Faktoren berücksichtigen und ordnen, sich auf ein einzelnes Element konzentrieren und dann zurückkehren, um die Situation neu zu bewerten. Autorouter verwenden eine Strategiedatei, um ihre Denkmuster zu definieren. Die Strategiedatei steuert die Routing-Engines, ruft sie bei Bedarf auf und gewichtet ihre Aktionen entsprechend.

Um die wichtige Rolle der Strategiedatei zu würdigen, betrachten Sie, wie sich die Art der Routing-Aufgabe ändert, während das Routing fortschreitet. Die Ansätze, die verwendet werden, um eine leere Platine zu Beginn des Routing-Prozesses zu routen, unterscheiden sich deutlich von denen, die verwendet werden, wenn die Routing-Dichte zunimmt und unterschiedliche Routing-Engines entsprechend gewichtet benötigt werden. Die in der Strategiedatei geschriebenen Anweisungen definieren einen Plan, wie die Platine geroutet werden soll, indem sie die Routing-Engines auf eine bestimmte Weise aufrufen und gewichten, wenn der Routing-Raum relativ leer ist, und dann die Engines und ihre Gewichtungen ändern, wenn sie die letzten Routen durch dicht belegten Routing-Raum quetschen.

Indem der Denkprozess oder das Gehirn des Autorouters in einer Strategiedatei implementiert wird, ist es für Altium möglich, den Autorouter leicht zu entwickeln, wenn sich die Board-Technologien ändern. Die Situs-Strategiedatei ist eine der ausgefeiltesten Strategiedateien eines Autorouters, die heute verfügbar sind. Sie verkörpert Jahre der Forschung in den Routing-Prozess und fängt die Expertise vieler erfahrener PCB-Designer ein.

Das Autorouting einer PCB

Der Situs Topological Router bringt einen neuen Ansatz für die Herausforderung des Autoroutings. Er verwendet fortgeschrittene topologische Kartierungen, um zunächst den Routingpfad zu definieren und ruft dann eine Vielzahl bewährter Routing-Algorithmen auf, um diesen „menschlichen“ Pfad in eine hochwertige Route umzuwandeln. Als integraler Bestandteil des PCB-Editors folgt er den elektrischen und Routing-Regeldefinitionen der PCB.

Planung der Verwendung von Autorouting

Obwohl Situs einfach einzurichten und zu betreiben ist, gibt es einige Schritte vor dem Routing, die Sie unternehmen können, um sicherzustellen, dass das Tool ein optimales Routing mit minimaler Nacharbeit produziert. Einige Tipps für das Autorouting umfassen:

- Identifizieren Sie die Netze mit den lockersten Einschränkungen. Diese sind in der Regel langsamere digitale Netze, die keine Impedanzanforderung haben.

- Bestimmen Sie, welche Gruppen von Netzen Sie automatisch routen möchten, und fügen Sie diese zu Netzklassen hinzu.

- Routen Sie die kritischsten Netze zuerst. Diese sind in der Regel schnellere Differentialpaarnetze, höherfrequente RF-Netze und analoge Schnittstellen mit niedrigerer Frequenz.

- Lassen Sie Routingkanäle offen, damit das Tool Leiterbahnen platzieren kann.

- Wenden Sie das Autorouting-Tool auf jede Netzklassen individuell an. Sie können das Tool auch verwenden, um spezifische Komponenten oder sogar einzelne Netze zu zielen (siehe unten).

Komponentenplatzierung

Letztendlich hat die Platzierung der Komponenten den größten Einfluss auf die Routing-Leistung. Der PCB Editor von Altium Designer umfasst eine Reihe von Werkzeugen, wie dynamisch optimierte Verbindungsleitungen, die es Ihnen ermöglichen, die Platzierung der Komponenten fein abzustimmen. Die optimale Komponentenplatzierung ist erreicht, wenn die Verbindungsleitungen so kurz und so wenig "verwickelt" wie möglich sind.

Weitere gute Designpraktiken umfassen das Platzieren von Komponenten, sodass ihre Pads auf einem regelmäßigen Raster liegen (um die Menge an freiem Raum zwischen den Pads für das Routing zu maximieren), das genaue Gegenüberstellen von ähnlich großen Oberflächenmontagekomponenten auf doppelseitigen Platinen und das Konsultieren von Datenblättern der Gerätehersteller für Richtlinien zur Entkopplungsplatzierung. Dies ist keine vollständige Liste von Platzierungsüberlegungen, sondern lediglich einige Vorschläge.

Sperrbereiche

Der Router benötigt eine geschlossene Grenze, die aus platzierten Sperrobjekten besteht. Typischerweise folgt diese Grenze dem Rand der Platine. Platzierte Objekte werden die entsprechende Freiraumregel befolgen, um sicherzustellen, dass sie einen geeigneten Abstand von dieser Grenze einhalten, um etwaige mechanische oder elektrische Freiraumanforderungen des Designs zu erfüllen. Der Router wird auch Sperrbereiche innerhalb dieser äußeren Grenze sowie schichtspezifische Sperrbereiche beachten.

Sie können eine geschlossene Begrenzung erstellen, die dem Rand der Platinenform folgt, indem Sie das Dialogfeld "Linien-/Bogenprimitive aus Platinenform" verwenden. Für weitere Informationen über Keepouts siehe Objektspezifische Keepouts.

Polygonfüllungen

Polygon- (oder Kupfer-) Füllungen können entweder solide (gefüllt mit einer oder mehreren Kupferregionen) oder gerastert (konstruiert aus Spuren und Bögen) sein. Eine mittelgroße bis große gerasterte Polygonfüllung umfasst eine große Anzahl von Spuren und Bögen. Obwohl der Router eine Platine, die solche Polygonfüllungen enthält, routen kann, erhöht die schiere Anzahl der Objekte, die sie einführen, die Komplexität des Routingprozesses.

Typischerweise sollten Sie Polygonfüllungen nur vor dem Routing platzieren, wenn sie erforderlich sind, zum Beispiel, wenn sie verwendet werden, um ungewöhnlich geformte Vor-Routings zu konstruieren, vielleicht das Routing der Eingangsstromversorgung oder eine kritische Massefläche. Andernfalls ist es vorzuziehen, dass Polygonfüllungen dem Design hinzugefügt werden, sobald das Routing abgeschlossen ist.

Ist es routbar?

Ein Autorouter versucht, den Routing-Prozess zu verstehen und zu modellieren. Wenn die Platine einen Bereich enthält, der von Hand nicht geroutet werden kann, dann wird er auch nicht automatisch geroutet. Wenn der Router kontinuierlich bei einem Bauteil oder einem Abschnitt der Platine scheitert, sollten Sie versuchen, es interaktiv zu routen. Es könnte sein, dass Platzierungs- oder Regelkonfigurationsprobleme vorliegen, die ein Routing vollständig unmöglich machen.

Vor-Routing

Kritische Netze vorab routen und, falls es wesentlich ist, dass sie durch den Routing-Prozess nicht verändert werden, diese durch Aktivieren der Option Alle Vor-Routen sperren im Situs Routing Strategies-Dialog sperren. Vermeiden Sie jedoch unnötiges Sperren; eine große Anzahl gesperrter Objekte kann das Routing-Problem erheblich erschweren.

Differentielle Paarnetze müssen manuell geroutet und vor der Verwendung des Autorouters gesperrt werden. Wenn Sie dies nicht tun, ist es sehr wahrscheinlich, dass das Routing geändert wird und die Signalintegrität des differentiellen Paares beeinträchtigt.

Designregeln konfigurieren

Der Begriff Standardregel wird verwendet, um eine Regel mit einem Abfragebereich von Alle zu beschreiben.

Wenn eine Regel Mindest-, Bevorzugte und Höchstwerte enthält, wird der Autorouter den bevorzugten Wert verwenden.

Stellen Sie sicher, dass die Routing-Designregeln für die von Ihnen verwendete Platinentechnologie geeignet sind. Schlecht angepasste oder unangemessene Designregeln können zu sehr schlechter Autorouting-Leistung führen. Beachten Sie, dass der Router allen elektrischen und Routing-Designregeln folgt, mit Ausnahme der Regel für Routing-Ecken.

Regeln werden im PCB-Regeln und Einschränkungen-Editor-Dialog (Design » Regeln) definiert, auf den direkt über den Situs Routing-Strategien-Dialog zugegriffen werden kann.

Wenn eine Regel Mindest-, Bevorzugte und Höchstwerte enthält, verwendet der Autorouter den bevorzugten Wert.

Das Regelsystem von Altium Designer ist hierarchisch aufgebaut. Die Idee ist, dass Sie mit einer Standardregel für alle Objekte beginnen und dann zusätzliche Regeln hinzufügen, um gezielt andere Objekte anzusprechen, die unterschiedliche Anforderungen haben. Zum Beispiel sollten Sie eine Standardregel für die Routingbreite haben, die die am häufigsten verwendete Routingbreite auf der Platine abdeckt, und dann nachfolgende Regeln hinzufügen, um gezielt andere Netze, Netzklassen usw. anzusprechen.

Um zu überprüfen, ob eine Regel die richtigen Objekte anvisiert, kopieren Sie die Abfrage der Regel in das PCB-Filterfeld und wenden Sie es an. Nur die Objekte, auf die die Regel abzielt, sollten den Filter passieren und in voller Stärke angezeigt werden. Alternativ können Sie das PCB-Regeln und Verstöße-Panel verwenden, um schnell die Anwendung von Regeln über jede definierte Regel für das aktuelle Board zu sehen.

Die wichtigsten Regeln sind die Breiten- und Abstands-Regeln. Diese Routing-Technologieeinstellungen definieren, wie dicht das Routing 'gepackt' werden kann. Die Auswahl ist ein Balanceakt - je breiter die Bahnen und je größer der Abstand, desto einfacher ist es, das Board zu fertigen; im Gegensatz dazu, je schmaler die Bahnen und Abstände, desto einfacher ist es, das Board zu routen. Es ist ratsam, Ihren Hersteller zu konsultieren, um deren 'Preispunkte' für Routingbreiten und -abstände zu ermitteln, jene Werte, bei deren Unterschreitung niedrigere Fertigungsausbeuten und höherpreisige PCBs resultieren. Neben der Erfüllung der elektrischen Anforderungen des Designs sollte die Routing-Technologie auch so gewählt werden, dass sie zur Komponententechnologie passt, um jeden Pin routen zu können.

Die dritte Regel, die Teil der Routing-Technologie ist, ist der Routing Via Style. Sie sollte ebenfalls so ausgewählt werden, dass sie zu den Leiterbahnen und Freiräumen passt, wobei die Fertigungskosten der gewählten Lochgröße und des Ringes berücksichtigt werden sollten.

Man sollte auch übermäßige oder unnötige Regeln vermeiden - je mehr Regeln, desto mehr Verarbeitungszeit, desto langsamer das Routing. Regeln können deaktiviert werden, wenn sie für das Autorouting nicht erforderlich sind.

Leiterbahnbreite

Stellen Sie sicher, dass es eine Leiterbahnbreitenregel mit einer Abfrage von Alle (eine Standardregel) gibt, und dass die bevorzugte Einstellung für die am häufigsten benötigte Leiterbahnbreite geeignet ist. Achten Sie darauf, dass diese Breite in Kombination mit der entsprechenden Freiraumregel es ermöglicht, alle Pads anzuschließen. Konfigurieren Sie zusätzliche Leiterbahnbreitenregeln für Netze, die breitere oder schmalere Leiterbahnen erfordern.

Wenn es Bauteile mit feinem Raster gibt, die Pins an Netzen mit breiteren Leiterbahnen haben - zum Beispiel Stromnetze - testen Sie das Herausführen aus einem Strompin und führen Sie auch den Pin auf jeder Seite heraus, um sicherzustellen, dass es physisch möglich ist, diese Pins zu verdrahten.

Abstandsbegrenzung

Überprüfen Sie auf spezielle Freiraumanforderungen, wie zum Beispiel Bauteile mit feinem Raster, deren Pads näher beieinander liegen als die standardmäßigen Leiterplattenabstände. Diese können mit einer geeignet definierten und priorisierten Designregel berücksichtigt werden. Beachten Sie, dass Sie zwar eine Regel definieren können, die auf einen Footprint abzielt, diese jedoch nicht die Verdrahtung, die zu diesem Footprint führt, berücksichtigt. Wie gerade im Abschnitt zur Leiterbahnbreite erwähnt, testen Sie die Route, um sicherzustellen, dass die Anschlussstifte der Komponente verdrahtbar sind.

Stil der Verbindungsvias

Stellen Sie sicher, dass es eine Regel für den Stil der Verbindungsvias mit einer Abfrage von Alle gibt und dass die bevorzugte Einstellung angemessen ist. Schließen Sie Regeln mit höherer Priorität für jene Netze ein, die einen anderen Via-Stil benötigen als die Standardregel.

Altium Designer unterstützt blinde und vergrabene Vias. Der Einsatz dieser wird durch die erlaubten Lagenwechsel bestimmt, die durch die in dem Layer Stack Manager (Design » Layer Stack Manager) definierten Via-Typen festgelegt sind. Ähnlich wie beim interaktiven Verlegen von Leiterbahnen prüft der Autorouter beim Wechsel zwischen zwei Lagen die aktuellen Via-Typ-Definitionen - wenn diese Lagen als ein blindes oder vergrabenes Lagernpaar definiert sind, dann werden die Vias mit diesen Lagen als Start- und Endlagen platziert. Es ist wichtig, die Einschränkungen beim Einsatz von blinden/vergrabenen Vias zu verstehen; sie sollten nur in Absprache mit Ihrem Leiterplattenhersteller verwendet werden. Neben den Einschränkungen, die durch die Fertigungs-Stackup-Technologie auferlegt werden, gibt es auch Überlegungen hinsichtlich Zuverlässigkeit und Testzugänglichkeit. Einige Designer halten es für besser, mehr Routing-Lagen hinzuzufügen, als blinde/vergrabene Vias zu verwenden.

Routing-Lagen

Stellen Sie sicher, dass eine Routing-Lagen-Regel mit einer Abfrage von All vorhanden ist. Alle aktivierten Signallagen (definiert im Lagenstapel) werden aufgelistet. Aktivieren Sie die Lagen, auf denen Sie das Routing erlauben möchten, wie erforderlich. Fügen Sie höher priorisierte Regeln für Netze hinzu, die Sie nur auf spezifischen Lagen verlegt haben möchten.

Möchten Sie ein bestimmtes Netz (oder eine Klasse von Netzen) vom Routing durch den Autorouter ausschließen, definieren Sie eine Routing-Layer-Regel, die auf dieses Netz oder die Netzklassen abzielt, und stellen Sie sicher, dass in dem Bereich für die Einschränkungen dieser Regel die Option Erlaube Routing für jede aktivierte Signallage deaktiviert ist. Die Priorität der Regel muss höher sein als die der Standardregel (die mit einer Abfrage von Alle).

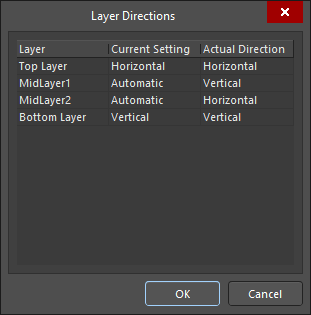

Schichtausrichtungen

Die Routing-Richtung der Schichten wird im Dialogfeld "Schichtrichtungen" festgelegt, das über den Dialog "Situs-Routingstrategien" aufgerufen wird. Alle aktivierten Signallagen (definiert im Lagenaufbau) werden aufgelistet. Wählen Sie geeignete Schichtrichtungen, die zum Verlauf der Verbindungsleitungen passen. Situs verwendet topologisches Mapping, um Routingpfade zu definieren, daher ist es nicht darauf beschränkt, horizontal und vertikal zu routen. Typischerweise ist es am besten, die äußeren Schichten horizontal und vertikal zu haben. Wenn Sie jedoch eine Mehrlagenplatine mit einer großen Anzahl von Verbindungen in einem '2-Uhr-Winkel' haben, dann stellen Sie eine oder mehrere innere Schichten so ein, dass dies die bevorzugte Routingrichtung ist. Die Layer Patterns-Passage macht insbesondere Gebrauch von diesen Informationen, und die Wahl der richtigen Richtung kann einen signifikanten Unterschied für die Routing-Leistung in Bezug auf Zeit und Qualität machen. Beachten Sie, dass Sie, wenn Sie Winkelschichten verwenden, keine Partnerlage benötigen, die um 90 Grad zu dieser Schicht verläuft, da der Router typischerweise horizontal oder vertikal routet, wenn er ein Hindernis auf einer Winkelschicht umgehen muss.

Vermeiden Sie die Verwendung der Beliebigen Richtung - die Schicht, die für die Verlegung einer Verbindung gewählt wird, basiert darauf, wie genau die Verbindung mit der Schichtrichtung ausgerichtet ist, sodass diese Schicht zur Schicht der letzten Wahl wird. Die Beliebige Richtung wird typischerweise nur auf einseitigen Platinen verwendet.

Routing-Priorität

Verwenden Sie die Routing-Prioritätsregeln, um eine höhere Priorität bei schwierigen Netzen festzulegen, oder bei solchen, die Sie am saubersten verlegt haben möchten.

SMD-Fanout-Kontrolle

Das Abfragesystem umfasst Schlüsselwörter, die speziell auf die verschiedenen Oberflächenmontage-Komponentenpakete abzielen, einschließlich IsLCC (Leadless Chip Carrier), IsSOIC (Small Outline IC) und IsBGA (Ball Grid Array). Standardregeln werden automatisch für die gängigsten Pakete erstellt, und da die Fanout-Durchläufe früh im Autorouting-Prozess ausgeführt werden, gibt es kaum Nachteile, Regeln beizubehalten, die auf keine Komponenten zutreffen. Sie sollten mindestens eine SMD-Fanout-Kontroll-Designregel haben, wenn sich Oberflächenmontagekomponenten auf der Platine befinden - eine geeignete Abfrage für eine einzelne Regel, die alle Oberflächenmontagekomponenten abzielt, wäre IsSMTComponent. Für Informationen darüber, wie jedes Abfrageschlüsselwort ein Komponentenpaket identifiziert, öffnen Sie den Query Helper, geben das erforderliche Schlüsselwort ein und drücken F1.

Die Fanout-Regeln umfassen Einstellungen, die steuern, ob die Pads ein- oder ausgefächert werden sollen oder eine Mischung aus beidem. Um sich mit dem Verhalten der Attribute der Fanout-Steuerungsregel vertraut zu machen, kann der Befehl Route » Fanout » Komponente auf jede Oberflächenmontagekomponente angewendet werden, der keine Netze zugewiesen sind. Neben der Verwendung dieses Befehls, um zu überprüfen, wie gut eine Komponente mit der aktuellen Routing-Technologie, die im Board definiert ist, ausgefächert wird, können Sie ihn auch verwenden, um eine Komponente auszufächern, die Sie als vorausgefächerten Footprint in einer Bibliothek behalten möchten. Sobald sie im PCB-Arbeitsbereich ausgefächert ist, kopieren und fügen Sie die Komponente sowie die Fanout-Leiterbahnen und -Vias in eine Bibliothek ein.

Regelprioritäten

Die Vorrangigkeit oder Priorität von Regeln wird vom Designer definiert. Die Regel-Priorität wird verwendet, um zu bestimmen, welche Regel angewendet werden soll, wenn ein Objekt von mehr als einer Regel abgedeckt ist. Wenn die Priorität nicht korrekt festgelegt ist, kann es vorkommen, dass eine Regel überhaupt nicht angewendet wird.

Zum Beispiel, wenn die Regel mit einer Abfrage von InNet('VCC') eine niedrigere Priorität hat als die Regel mit einer Abfrage von Alle, dann wird die Regel Alle auf das VCC-Netz angewendet. Verwenden Sie die Schaltfläche Prioritäten im Dialog PCB-Regeln und Einschränkungen Editor, um auf den Dialog Regelprioritäten bearbeiten zuzugreifen, von wo aus die Prioritäten bei Bedarf verfeinert werden können. Beachten Sie, dass die Priorität nicht wichtig ist, wenn sich zwei Regelbereiche nicht überschneiden (nicht dieselben Objekte ansprechen). Zum Beispiel macht es keinen Unterschied, welche dieser beiden Regelbereiche eine höhere Priorität hat - InNet('VCC') oder InNet('GND').

Die goldene Regel

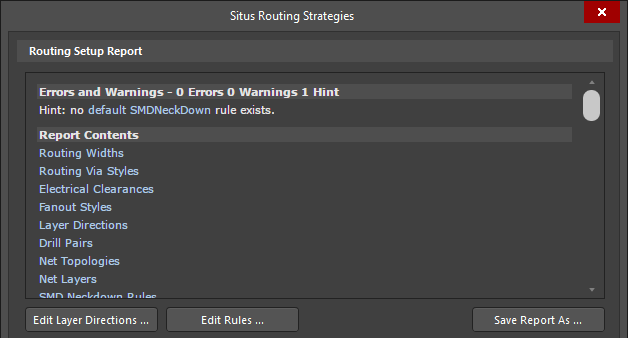

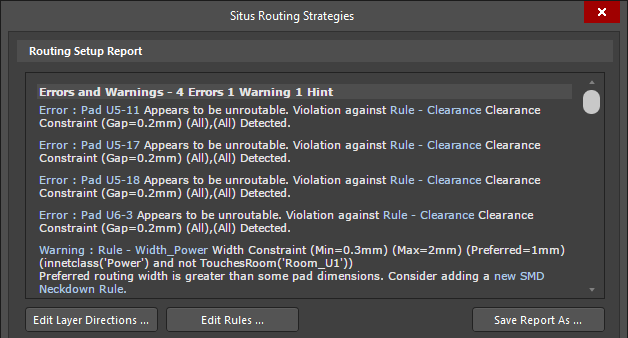

Der wichtigste Schritt ist, eine Designregelprüfung (DRC) durchzuführen, bevor mit dem Autorouter begonnen wird. Wenn die Befehle Route » Auto Route » Setup oder Route » Auto Route » Alle verwendet werden, führt Situs seine eigene Vor-Routing-Analyse durch und präsentiert die Ergebnisse als Bericht im Dialog Situs Routing-Strategien.

Stellen Sie sicher, dass der Bericht zur Routing-Einrichtung sauber ist, bevor Sie den Autorouter starten.

Der Bericht enthält Informationen, einschließlich:

- Derzeit für das Design definierte Entwurfsregeln, an die sich der Autorouter halten wird (und die Anzahl der Entwurfsobjekte - Netze, Komponenten, Pads - die von jeder Regel betroffen sind)

- Festgelegte Routing-Richtungen für alle Signalleiterbahnebenen

- Bohrschichtpaar-Definitionen

Der Bericht listet potenzielle Probleme auf, die die Leistung des Routers beeinträchtigen könnten. Wo möglich, werden Hinweise gegeben, um eine bessere Vorbereitung des Designs für das Autorouting zu beraten. Alle aufgeführten Fehler/Warnungen/Hinweise sollten genau geprüft und, falls nötig, die entsprechenden Routing-Regeln angepasst werden, bevor mit dem Routing des Designs fortgefahren wird.

Überprüfen Sie alle Fehler, Warnungen und Hinweise, um zu verstehen, mit welchen potenziellen Problemen der Autorouter konfrontiert wird.

Es ist wesentlich, dass alle mit dem Routing zusammenhängenden Regelverstöße gelöst werden, bevor der Autorouter gestartet wird. Verstöße können nicht nur das Routing an der Verstoßstelle verhindern, sondern auch den Router erheblich verlangsamen, da er kontinuierlich versucht, einen nicht routbaren Bereich zu routen.

Tipps zum Ausführen des Autorouters

- Die Befehle des Autorouters befinden sich im Route » Auto Route Untermenü.

- Sowohl die Befehle Route » Auto Route » All als auch Route » Auto Route » Setup öffnen das Situs Routing Strategies Dialog. Der Unterschied besteht darin, dass bei der Auswahl von All der Dialog einen Route All-Button enthält.

- Haben Sie keine Angst zu experimentieren. Wenn die Ergebnisse nicht akzeptabel sind, ändern Sie etwas an der Herangehensweise des Routers. Fügen Sie Zwischenreinigungen und Geradeaus-Pässe hinzu, schaffen Sie mehr Raum um dichte Bereiche oder ändern Sie die Richtungen der Schichten.

- Wenn Sie mit dem Router experimentieren - indem Sie Ihre eigenen Strategien erstellen, um die Reihenfolge der Durchläufe zu steuern, die Anzahl der Vias mit der Via-Steuerung ändern, die Routing-Schicht-Richtungen ändern, den Router auf orthogonale Routen beschränken und so weiter - halten Sie Notizen über die Kombinationen fest, die Sie ausprobiert haben. So können Sie identifizieren und wiederverwenden, welche Konfigurationen am besten mit Ihren Entwürfen funktionieren.

- Führen Sie zuerst Fanout-Pässe eigenständig durch und bewerten Sie die Qualität. Möglicherweise müssen Sie problematische Bereiche manuell fanouten.

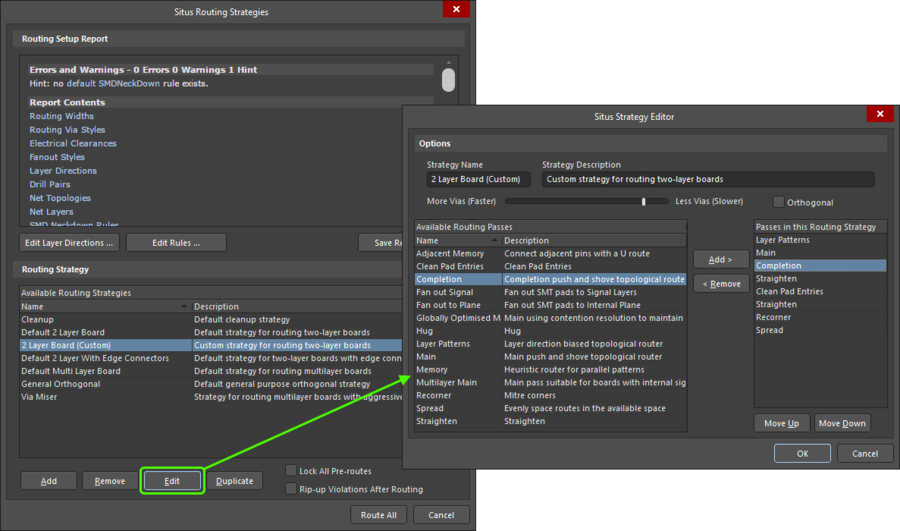

Routing-Pässe und Routing-Strategien

Derzeit definierte Routingstrategien werden im unteren Bereich des Situs Routing Strategies Dialogs aufgelistet. Klicken Sie auf die Schaltfläche Hinzufügen, um auf den Situs Strategy Editor Dialog zuzugreifen, von wo aus Sie die Durchgänge festlegen können, die in eine neue Strategie aufgenommen werden sollen. Alternativ verwenden Sie die Schaltfläche Duplizieren, um eine vorhandene Strategie zu duplizieren und dann nach Bedarf zu bearbeiten.

Beispiel für die Bearbeitung einer duplizierten Strategie.

Benutzerdefinierte Strategien können jederzeit bearbeitet werden, aber diese Standardstrategien können nicht modifiziert werden:

- Aufräumen

- Standard 2-Lagen-Platine

- Standard 2-Lagen mit Randsteckverbindern

- Standard Mehrschichtplatine

- Allgemein Orthogonal

- Via Geiz

Die folgenden Routingdurchgänge sind verfügbar. Die Durchgänge können in beliebiger Reihenfolge verwendet werden, als Anleitung betrachten Sie eine bestehende Strategie, um die Reihenfolge der Durchgänge zu sehen.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Beispiel Autorouter-Ergebnisse

In diesem Beispiel werden wir eine Interface-Breakout-Platine verwenden, die in einigen kürzlich veröffentlichten Videos verwendet wurde, und wir werden den Autorouter auf einige der Netze anwenden. Ziel ist es zu sehen, wann der Autorouter Fehler macht, wie das Werkzeug mit komplexen (und möglicherweise gegenseitig ausschließenden) Regelsätzen umgeht, sowie wie man allgemein mit dem Werkzeug arbeitet.

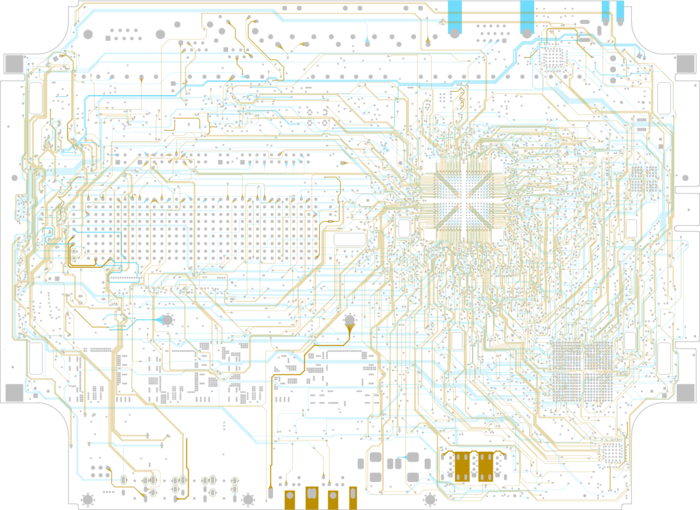

Um zu beginnen, habe ich eine fertige Platine, die wir als Ausgangspunkt in diesem Beispiel verwenden werden; die gesamte Platine wurde von Hand verdrahtet. Dies wird unten gezeigt.

Diese Platine ist halbkomplex, zumindest was die Regeln für Layout und Verdrahtung betrifft. Diese Platine ist eine Schnittstellenplatine zwischen einigen SMD-Steckverbindern auf gegenüberliegenden Seiten der Platine. Die Layoutregeln umfassen kontrollierte Impedanz für differentielle Paare, und die Platine enthält interne Schichten für mehrere Stromschienen, Masse und einige differentielle Kanäle.

In diesem Beispiel wurden die folgenden Einstellungen verwendet:

- Allgemeine orthogonale Routingstrategie (oben und unten horizontal, SIG1 und SIG2 vertikal)

- Alle Vor-Routen wurden gesperrt

- Alle Netze waren digitale Niedriggeschwindigkeitsnetze (GPIOs und I2C), keine Impedanzkontrolle erforderlich

- Insgesamt waren 27 Netze zu verlegen

Der letzte Punkt und der Aufbau des PCB-Stackups ermöglichen es uns im Allgemeinen, mit dem Verlegen dieser Signale in mehreren Schichten, durch mehrere Vias und ohne jegliche Längenbeschränkung auszukommen. Komplexere Platinen oder dichtere könnten spezialisiertere Einstellungen erfordern.

Die Ergebnisse für die Routen in den Signallagen sind unten dargestellt.

Also, was ist das Urteil? In diesem speziellen Fall war die Reinigung von nur einem Kurzschlussverstoß auf der unteren Schicht erforderlich. Das ist ziemlich gut, wenn man die Anordnung der Pins am oberen horizontalen Stecker bedenkt. Ich denke, das ist angemessen

Abschließende Gedanken

Im Laufe dieses Tutorials wurde mir etwas Wichtiges klar: Die Autorouter-Strategie und eine akzeptable Routing-Topologie auf Ihrer Platine müssen übereinstimmen. Nehmen wir zum Beispiel an, Sie haben eine Mehrlagenplatine mit einer großen Anzahl von Netzen und möchten ein Autorouting mit orthogonalen Bahnen implementieren; Ihr spezieller Autorouter eignet sich am besten für die Umsetzung dieser Strategie, nur wenn eine orthogonale Option in Ihrem Autorouter integriert ist. Ist dieser Ansatz der richtige für Sie? Das hängt ganz von Ihrem speziellen Arbeitsablauf und Ihrem Ansatz für Designs ab.

Nicht alle Platinen eignen sich dafür. In einigen Beispielen habe ich Platinen gezeigt, bei denen eine orthogonale Strategie, eine Edge-Connector-Strategie oder eine 2-Lagen-Routing einfach nicht die Betriebsanforderungen für jedes Netz erfüllen. In diesem Fall ist es eine gute Idee, zuerst die empfindlichsten Leiterbahnen zu routen und dann zu versuchen, die verbleibenden Netze automatisch zu routen. Ein gutes Beispiel, über das ich kürzlich gesprochen habe, befindet sich in großen Phased-Array-Systemen; die Speiseleitungen erfordern eine sehr präzise Phasenanpassung, und die Einrichtungszeit könnte länger sein als Ihre manuelle Routing- und Anpassungszeit. Da diese Leiterbahnen so wichtig sind, macht es Sinn, diese von Hand zu routen.

Ich denke, ein guter Autorouter ist nur so gut wie die Fähigkeiten des Benutzers damit und das erforderliche Maß an Einrichtung. Wenn Sie sich etwas Zeit nehmen, um die erforderlichen Regeln einzustellen, spezifische Gruppen von Netzen für jede Durchführung zum Autorouten zu planen und eine Bereinigungsstrategie zu entwickeln, können Sie manuelle Nacharbeit minimieren. Das Tolle an einem Automatisierungswerkzeug ist, dass es für andere Designs wiederverwendet werden kann. Sobald die Regelprofile erstellt sind, können sie für das Autorouting in anderen PCB-Layouts implementiert werden.

Wenn Sie Zugang zu den besten Automatisierungswerkzeugen für PCB-Design benötigen, nutzen Sie das komplette Set an PCB-Layout- und Routing-Tools in Altium Designer®. Wenn Sie Ihr Design abgeschlossen haben und Dateien an Ihren Hersteller freigeben möchten, erleichtert die Plattform Altium 365™ die Zusammenarbeit und das Teilen Ihrer Projekte.

Wir haben nur an der Oberfläche dessen gekratzt, was mit Altium Designer auf Altium 365 möglich ist. Starten Sie heute Ihre kostenlose Testversion von Altium Designer + Altium 365.